TOPIC-WISE QUESTIONS (151)

Topics Used in This Course

[বিঃদ্রঃ সকল প্রশ্ন এখনও টপিক-ওয়াইজ সেকশনে নিয়ে আসা সম্ভব হয়নি।

আমাদের কাজ চলমান। শীঘ্রই এই কোর্সের জন্য সকল প্রশ্ন টপিক অনুসারে এখানে আলাদাভাবে দেখতে পাবেন।]

8080 Microprocessor

1 Questions

1.

Regarding Address Bus, Bus width determines maximu......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Cache Memory

2 Questions

1.

Describe the bottleneck for Cache Design.

Marks: 7.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

2.

Assume that there are three (03) small caches, eac......

Marks: 8.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Cache Memory Mapping Techniques

2 Questions

1.

What are the differences among direct mapping, ass......

Marks: 2.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

2.

Assume that there are three (03) small caches, eac......

Marks: 8.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Central Processing Unit (CPU)

1 Questions

1.

By Showing the major components of a CPU, briefly ......

Marks: 2.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

Computer Architecture

1 Questions

1.

How can processor performance be evaluated? Explai......

Marks: 6.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Fetch–Decode–Execute Cycle

1 Questions

1.

What do you know about fetch-execute cycle? Define......

Marks: 3.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Hit Ratio and Miss Penalty

2 Questions

1.

Consider a two-level cache with access time 5 nsec......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

2.

Assume that there are three (03) small caches, eac......

Marks: 8.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Interrupt Handling

1 Questions

1.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Interrupts and Interrupt Service Routines (ISR)

1 Questions

1.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

MAR (Memory Address Register)

1 Questions

1.

What do you know about fetch-execute cycle? Define......

Marks: 3.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

MBR (Memory Buffer Register)

1 Questions

1.

What do you know about fetch-execute cycle? Define......

Marks: 3.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Memory Addressing

1 Questions

1.

Regarding Address Bus, Bus width determines maximu......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Memory Bottlenecks

1 Questions

1.

Describe the bottleneck for Cache Design.

Marks: 7.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Memory Hierarchy

1 Questions

1.

Consider a two-level cache with access time 5 nsec......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Memory Operations

1 Questions

1.

What do you know about fetch-execute cycle? Define......

Marks: 3.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Memory and I/O

1 Questions

1.

Regarding Address Bus, Bus width determines maximu......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Moor's Law

1 Questions

1.

Explain Moor's Law in Computer architecture.

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

Processor

1 Questions

1.

Distinguish between RISC and CISC processor.

Marks: 2.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

Processor Performance

2 Questions

1.

How can processor performance be evaluated? Explai......

Marks: 6.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

2.

Explain the performance of a processor.

Marks: 3.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

RAM

2 Questions

1.

Differentiate between SRAM and DRAM.

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

2.

Differentiate between SRAM and DRAM

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

System Bus

2 Questions

1.

Regarding Address Bus, Bus width determines maximu......

Marks: 10.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

2.

Describe the multiplexed bus with advantages and d......

Marks: 4.00 |

Exam: 1st Mid |

Session: 22-23 |

Exam Date: 18 Sep, 2025 |

Course Teacher:

N/A

Solution is Coming!

Uncategorized Questions

136 Questions

1.

Assuming that ENIAC had the capability to have mul......

Marks: 10.00 |

Exam: 1st Mid |

Session: 20-21 |

Exam Date: N/A |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

2.

Assuming that ENIAC had the capability to have mul......

Marks: 5.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

3.

The ENIAC was a decimal machine, where a register ......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

4.

In DMA operation, describe about “Cycle Stealing".

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

5.

Assuming that ENIAC had the capability to have mul......

Marks: 5.00 |

Exam: 1st Mid |

Session: 21-22 |

Exam Date: 12 Mar, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

6.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: 20-21 |

Exam Date: N/A |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

7.

When a block that is resident in the cache is to b......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

8.

Consider a two-level cache with access time 5 nsec......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

9.

When a block that is resident in the cache is to b......

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

10.

Consider a two-level cache with access time 5 nsec......

Marks: 10.00 |

Exam: 1st Mid |

Session: 21-22 |

Exam Date: 12 Mar, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

11.

Regarding Address Bus, Bus width determines maximu......

Marks: 5.00 |

Exam: 1st Mid |

Session: 20-21 |

Exam Date: N/A |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

12.

Consider a two-level cache with access time 5 nsec......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

13.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

14.

Analyze the geometric depiction of 4-bit numbers f......

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

15.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: 21-22 |

Exam Date: 12 Mar, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

16.

The hypothetical machine of the Figure (given at r......

Marks: 10.00 |

Exam: 1st Mid |

Session: 20-21 |

Exam Date: N/A |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

17.

Suppose three interrupt handlers A, B and C (havin......

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

18.

Regarding Address Bus, Bus width determines maximu......

Marks: 5.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

19.

Distinguish between RAID 4 and RAID 5.

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

20.

Regarding Address Bus, Bus width determines maximu......

Marks: 5.00 |

Exam: 1st Mid |

Session: 21-22 |

Exam Date: 12 Mar, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

21.

What are the four main components of any general-p......

Marks: 5.00 |

Exam: 1st Mid |

Session: 20-21 |

Exam Date: N/A |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

22.

Regarding Address Bus, Bus width determines maximu......

Marks: 5.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

23.

Describe the bottleneck for Cache Design.

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

24.

We would like to design a cache of 64kByte. Main m......

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

25.

Describe the bottleneck for Cache Design.

Marks: 5.00 |

Exam: 1st Mid |

Session: 21-22 |

Exam Date: 12 Mar, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

26.

Describe the bottleneck for Cache Design.

Marks: 10.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

27.

How to determine the performance of a processor? E......

Marks: 5.00 |

Exam: 1st Mid |

Session: N/A |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

28.

It is possible to build a computer which uses only......

Marks: 10.00 |

Exam: 2nd Mid |

Session: 20-21 |

Exam Date: 22 Sep, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

29.

Analyze the step(s):

(i) no interrupt,

(ii) int......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

30.

Analyze the concept of "Write Back" in order to av......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

31.

What are the differences among direct mapping, ass......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

32.

Explain the performance of a processor.

Marks: 3.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

33.

Describe the necessity of I/O modules?

Marks: 2.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

34.

What is instruction? Mention the elements of an in......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

35.

Distinguish between 0-addresses, 2-addresses, 3-ad......

Marks: 6.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

36.

The ENIAC was a decimal machine, where a register ......

Marks: 6.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

37.

Von Neumann computer architecture is the basic com......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

38.

Interrupts are provided primarily as a way to impr......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

39.

Discuss about the memory hierarchy and typical cac......

Marks: 4.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

40.

Write notes on associative mapping function relate......

Marks: 6.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

41.

The simplest technique for replacement policy in c......

Marks: 6.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

42.

Distinguish between RAID 4 and RAID 5.

Marks: 4.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

43.

What is the purpose of using addressing mode techn......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

44.

In interrupt handler, analyze the step(s):

(i) no......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

45.

Analyze the concept of "Write Back" in order to av......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

46.

What are the differences among direct mapping, ass......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

47.

Describe the necessity of I/O modules?

Marks: 2.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

48.

Describe how an assembler works with its two phase......

Marks: 3.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

49.

How to determine the performance of a processor?

Marks: 2.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

50.

Analyze the step(s): (i) no interrupt, (ii) interr......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

51.

Analyze the concept of "Write Back" in order to av......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

52.

What are the differences among direct mapping, ass......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

53.

A computer has a 256 KByte, 4-way set associative,......

Marks: 3.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

54.

Describe the necessity of I/O modules?

Marks: 2.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

55.

Consider a magnetic disk drive with 8 surfaces, 51......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

56.

Define pipelining. Show the timing diagram of pipe......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

57.

Constructing a computer that utilizes only static ......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

58.

Display the synchronous system bus read/write timi......

Marks: 6.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

59.

In cache memory, overwriting a block before main m......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

60.

Examine the pros and cons of CD-ROMs.

Marks: 2.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

61.

How can processor performance be evaluated? Explai......

Marks: 2.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

62.

In Direct Memory Access (DMA) operation, describe ......

Marks: 6.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

63.

I/O is much slower than the CPU, so the CPU can re......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

64.

Distinguish between 3-addresses, 2-addresses, 1-ad......

Marks: 8.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

65.

8080 has 16 bit address bus. Then how much memory ......

Marks: 2.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

66.

Let's design a cache of 64KByte. Main memory is 16......

Marks: 8.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

67.

Assume that there are three (03) small caches, eac......

Marks: 5.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

68.

Von Neumann computer architecture is the basic com......

Marks: 5.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

69.

In Direct Memory Access (DMA) operation, describe ......

Marks: 6.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

70.

Briefly describe the data processing and data move......

Marks: 3.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

71.

Explain the trade-off (more or less) of the number......

Marks: 6.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

72.

Explain Moor's Law in Computer architecture.

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

73.

While processor power has raced ahead at breakneck......

Marks: 5.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

74.

Distinguish between traditional bus architecture a......

Marks: 4.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

75.

What are the differences among direct mapping, ass......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

76.

Draw and explain the block diagram of the hardware......

Marks: 6.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

77.

RAID 4 involves a write penalty when an I/O write ......

Marks: 6.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

78.

In Direct Memory Access (DMA) operation, describe ......

Marks: 5.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

79.

How can you classify computer instructions? Explai......

Marks: 5.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

80.

Explain Moor's Law in Computer architecture

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

81.

How much memory space 8080 will provide that has 1......

Marks: 2.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

82.

Let's design a cache of 64KByte. Main memory is 16......

Marks: 8.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

83.

Assume that there are three (03) small caches, eac......

Marks: 5.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

84.

Von Neumann computer architecture is the basic com......

Marks: 5.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

85.

In Direct Memory Access (DMA) operation, describe ......

Marks: 6.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

86.

Distinguish between 0-addresses, 2-addresses, 3-ad......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

87.

Differentiate between SRAM and DRAM.

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

88.

The ENIAC was a decimal machine, where a register ......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

89.

Let's design a cache of 64kByte. Main memory is 16......

Marks: 8.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

90.

Assume that there are three (03) small caches, eac......

Marks: 5.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

91.

Von Neumann computer architecture is the basic com......

Marks: 5.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

92.

In Direct Memory Access (DMA) operation, describe ......

Marks: 6.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

93.

Briefly describe the data processing and data move......

Marks: 3.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

94.

Explain Processor with an accumulator register.

Marks: 3.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

95.

Analyze the structure of the "Control Unit".

Marks: 2.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

96.

Regarding Address Bus, Bus width determines maximu......

Marks: 2.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

97.

We would like to design a cache of 64kByte. Main m......

Marks: 8.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

98.

Distinguish between RAID 4 and RAID 5.

Marks: 3.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

99.

Describe the multiplexed bus with advantages and d......

Marks: 3.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

100.

In I/O controller in computer architecture, O/S wo......

Marks: 6.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

101.

What are the key elements of an operating system i......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

102.

Discuss the concept of associate mapping address i......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

103.

Write short notes on the following:

i) Hit time ......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

104.

Show the Asynchronous timing diagram for system bu......

Marks: 6.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

105.

List and briefly define three (03) techniques for ......

Marks: 3.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

106.

Describe the multiplexed bus with advantages and d......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

107.

Describe O/S as a resource manager in I/O controll......

Marks: 4.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

108.

Briefly describe the instruction cycle of program ......

Marks: 5.00 |

Exam: Final |

Session: 17-18 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

109.

Distinguish between computer architecture and comp......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

110.

Instruction processing consists of two steps: The ......

Marks: 4.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

111.

Discuss with figures: Timing of Asynchronous Bus O......

Marks: 5.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

112.

Discuss the features of Synchronous DRAM (SDRAM).

Marks: 5.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

113.

Describe O/S as a resource manager in I/O controll......

Marks: 3.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

114.

Explain interrupt driven I/O technique.

Marks: 4.00 |

Exam: Final |

Session: 18-19 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

115.

Regarding Cache design, write short notes on the f......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

116.

Describe with figure: Asynchronous timing diagram ......

Marks: 6.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

117.

List and briefly define three (03) techniques for ......

Marks: 3.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

118.

Describe the multiplexed bus with advantages and d......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

119.

Describe O/S as a resource manager in I/O controll......

Marks: 4.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

120.

How Stack is organized in CPU? With proper block d......

Marks: 8.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

121.

Write two short notes from the below:

i) Op-cod......

Marks: 5.00 |

Exam: Final |

Session: 19-20 |

Exam Date: N/A |

Course Teacher:

Dr. Md. Manjur Ahmed

Solution is Coming!

122.

Write short notes on the following:

i) Hit time

......

Marks: 6.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

123.

Show the Asynchronous timing diagram for system bu......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

124.

List and briefly define three (03) techniques for ......

Marks: 3.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

125.

Describe the multiplexed bus with advantages and d......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

126.

Describe O/S as a resource manager in I/O controll......

Marks: 4.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

127.

Briefly describe the instruction cycle of program ......

Marks: 5.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

128.

Briefly describe the data processing and data move......

Marks: 5.00 |

Exam: Final |

Session: 20-21 |

Exam Date: 03 Nov, 2024 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

129.

Differentiate the terms architecture and organizat......

Marks: 2.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

130.

In interrupt cycle, analyze the step(s) if: (i) no......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

131.

Regarding internal memory, analyze the error corre......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

132.

The ENIAC was a decimal machine, where a register ......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

133.

Analyze the geometric depiction of 4-bit numbers f......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

134.

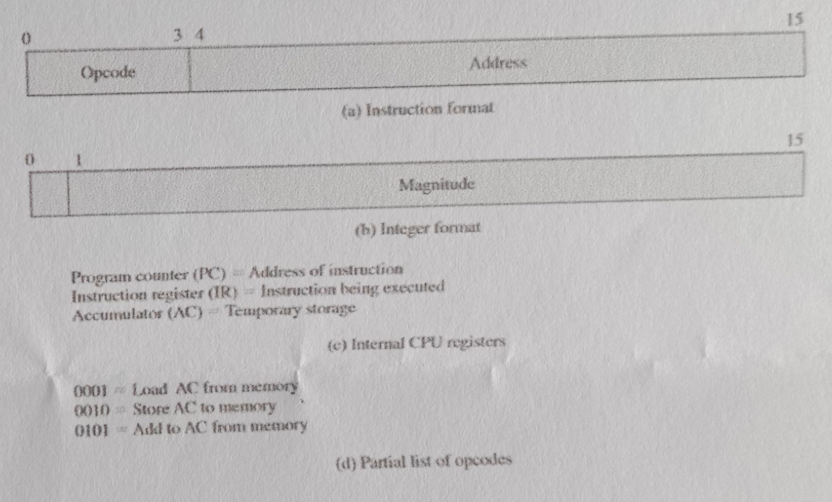

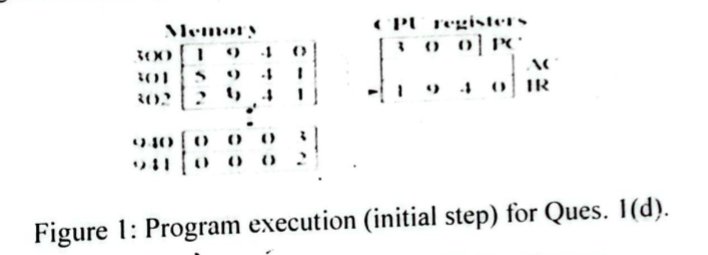

Figure 1 illustrates a partial program execution, ......

Marks: 4.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

135.

Discuss about Synchronous DRAM (SDRAM) as external......

Marks: 3.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

136.

Discuss the concept of von Neumann computer archit......

Marks: 3.00 |

Exam: Final |

Session: 21-22 |

Exam Date: 22 Jul, 2025 |

Course Teacher:

Dr. Md Manjur Ahmed

Solution is Coming!

Show All Questions