20-21

question 6

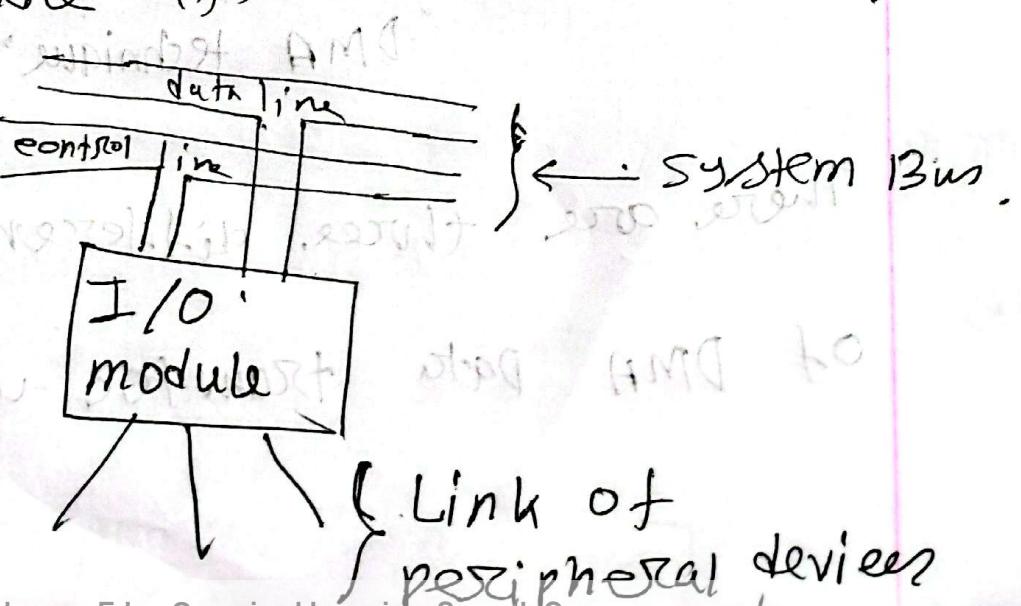

④ Describe the necessity of I/O modules?

Sol Input / output (I/O) modules are needed

to connect to input and output devices like (Keyboard, mouse, printer) to the computer.

They help the CPU communication with these devices by sending and receiving data properly.

Without I/O modules, the CPU can't directly handle different I/O devices.

(B)

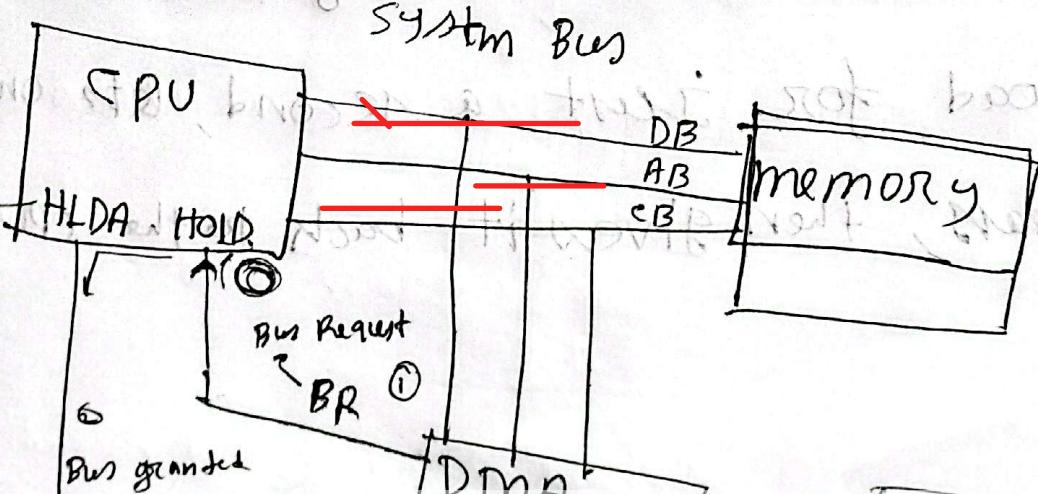

In Direct memory Access (DMA) operation describe about cycle stealing.

Quesn

DMA is a method that allows hardware devices to ~~allow~~ directly transfer data to or from memory without using the CPU in for each data transfer.

"DMA technique"

There are three different modes

of DMA data transfer which are -

## DMA mode

enables DMA to transfer data to memory

Burst mode      cycle stealing mode      interleaving mode

How does it work? (Answer to subquestion)

Cycle stealing mode:

~~Answer to subquestion~~ Cycle stealing mode is a process used in DMA operations where

DMA controller takes control of the

system bus for a short time to transfer

data while the CPU is temporarily paused.

CPU is paused briefly: The CPU stops for a moment so DMA can use the bus to transfer data.

Transfers small amount: only one unit is transferred in each cycle.

→ The CPU continues its work quickly after each transfer.

Imagine CPU and DMA are sharing a road. In cycle stealing, DMA borrows the road for just a second, lets one car pass, then gives it back to the CPU.

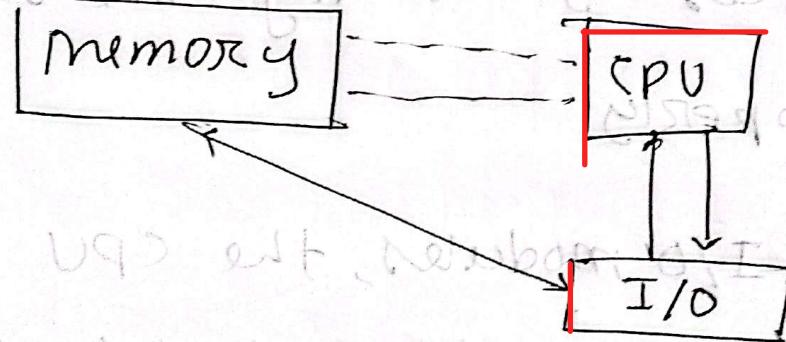

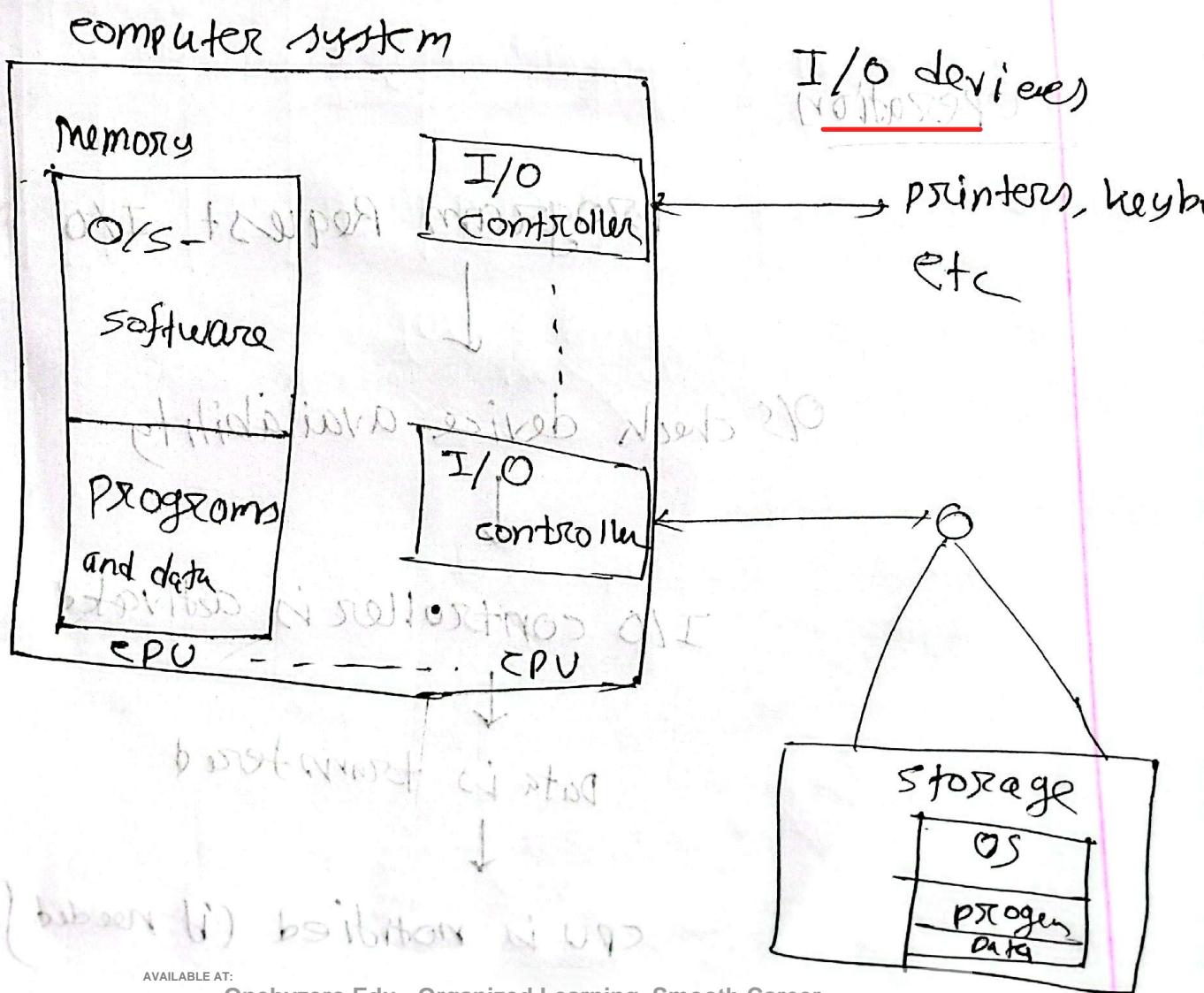

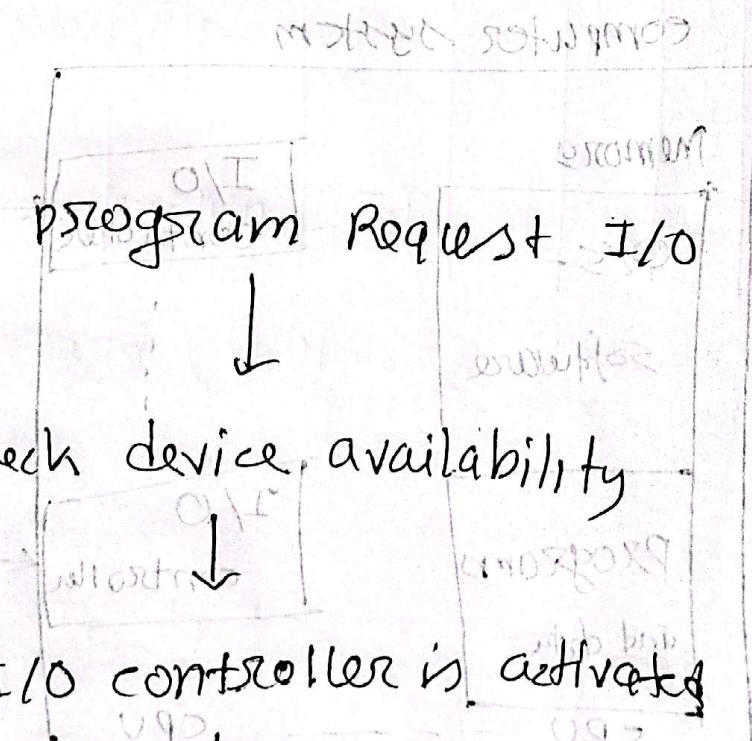

6(c) Describe ~~OS~~ as a resource manager in I/O controller.

Ans The operating system works as a resource manager to manage I/O devices through the I/O controller.

## Functions of OS as a Resource manager

- The OS allocates I/O devices to different process as needed

- It schedules I/O requests and maintain desired order of program execution.

- It manages data transfer between memory and devices using I/O controller.

## Operation

↓

CPU is notified (if needed)

AVAILABLE AT:

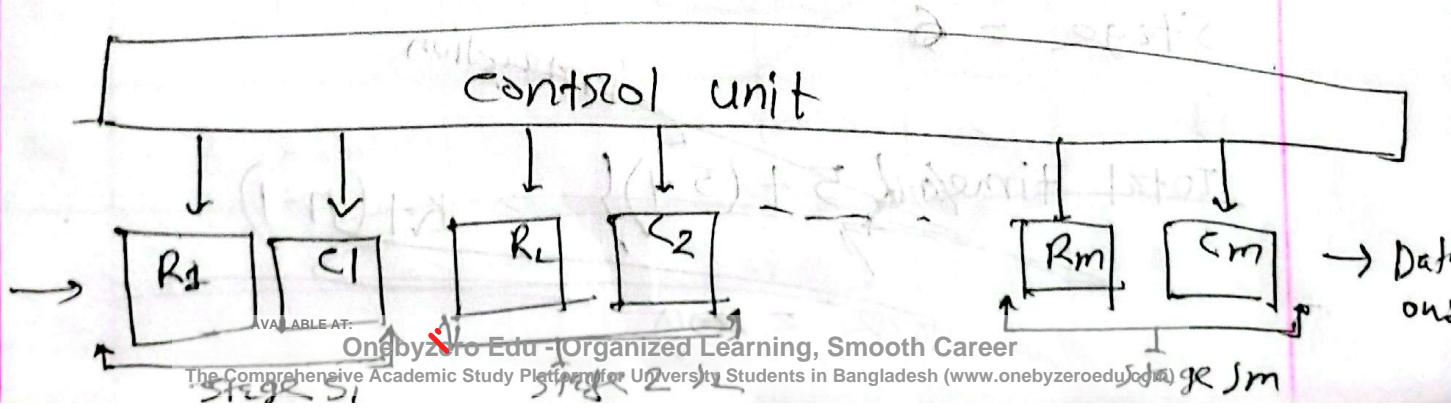

8(a) Pipeline Pipelining. Show the timing diagram of pipelining.

10M

Pipelining :- Pipelining is a technique used in CPUs to increase instruction execution speed by dividing the instruction into multiple stages.

Each stage works at the same time on different instructions.

While one instruction is being executed the next one can be decoded, and another can be fetched all the same time.

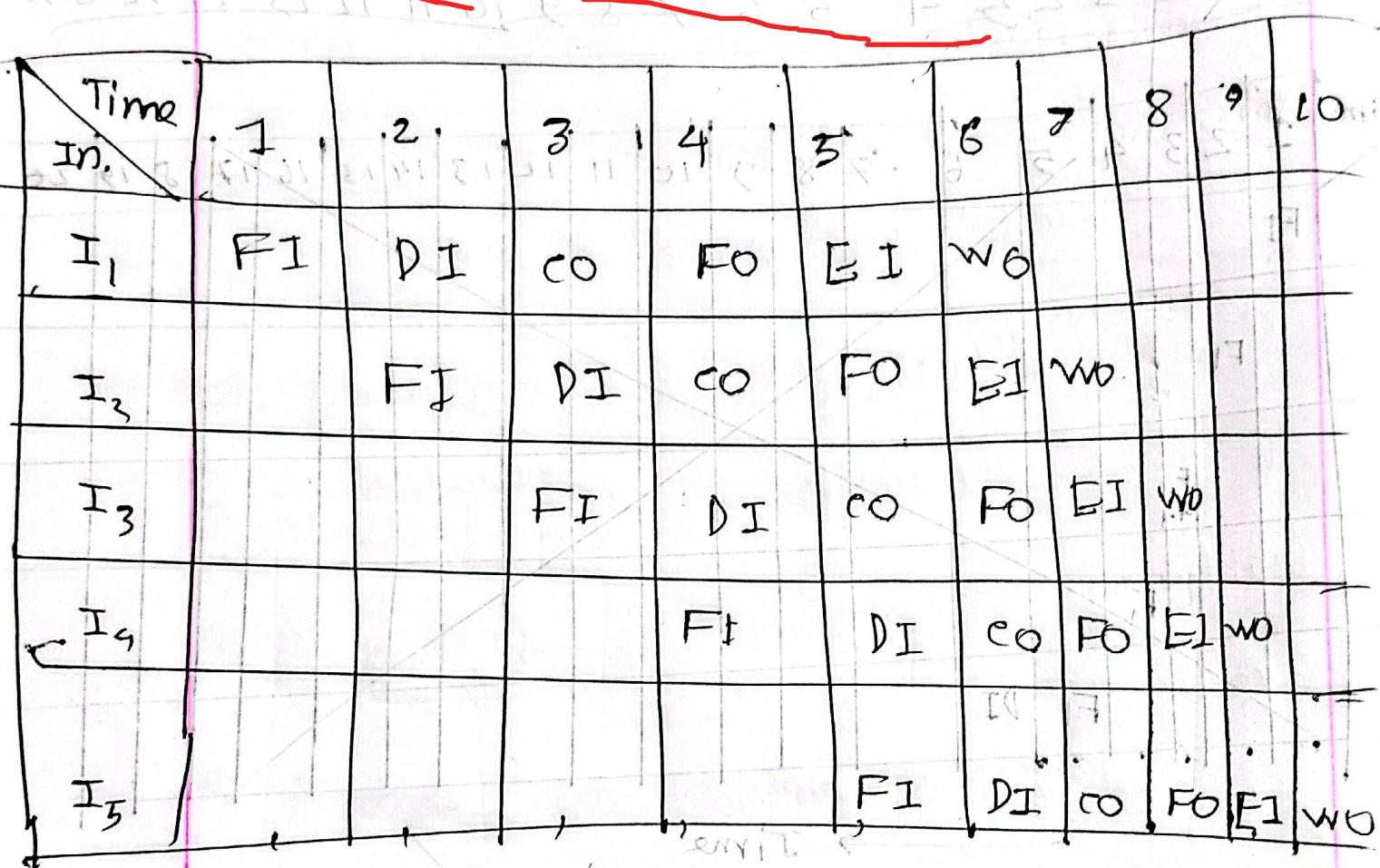

## Timing diagram for 5 instructions

~~5 stage pipeline~~

~~1. FI~~

1. Fetch Instruction (FI)

2. Decode Instruction (DI)

3. calculate operands (CO)

4. Fetch operands (FO)

5. Execute Instruction (EI)

6. write operand (WO)

Instructions (I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub>, I<sub>4</sub>, I<sub>5</sub>)

Stage = 6

Time =  $5 + (5-1)$

Total time =  $5 + (5-1) \} \geq k + (n-1)$

$$\text{Total cycle} = K + (n-1) = 6 + (5-1) = 10$$

Timing diagram for Pipeline

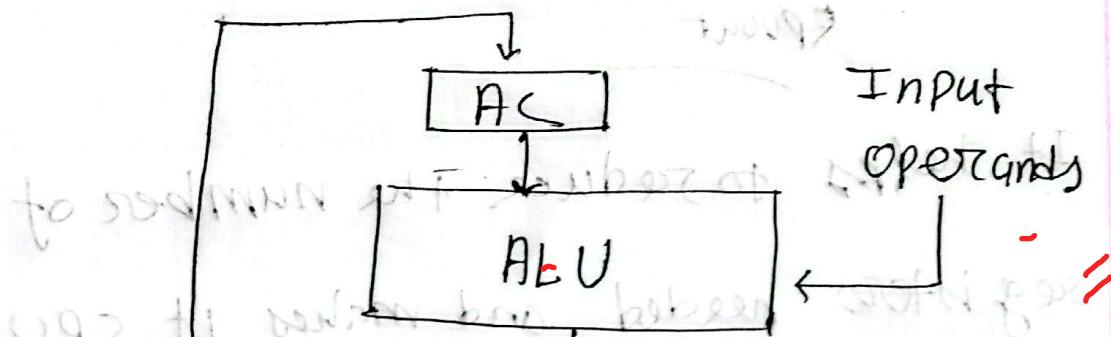

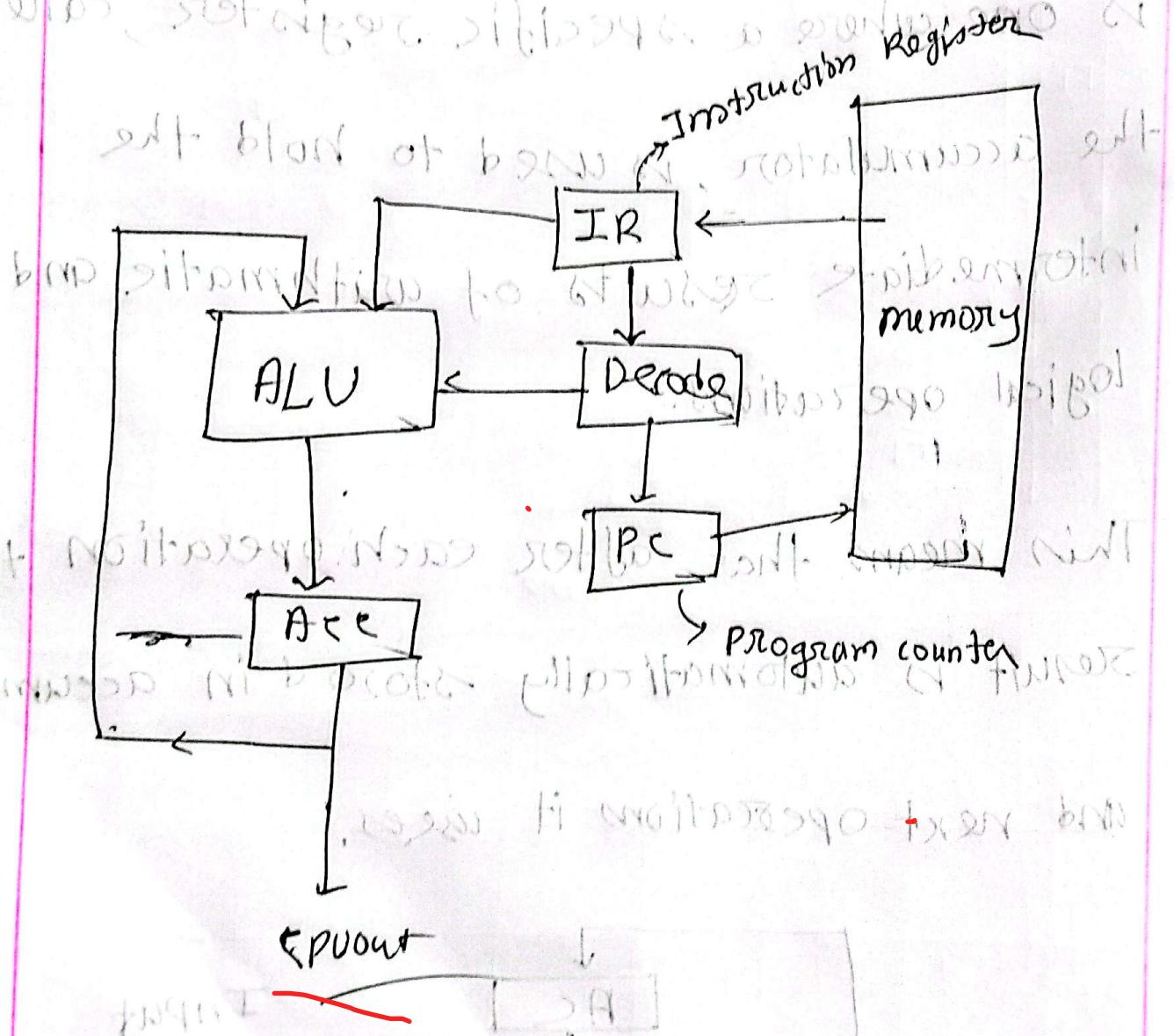

8(b) Explain processor with an accumulator

register gains and loss to 10,000,000

~~Some~~ A processor with an accumulator register

is one where a specific register, called

the accumulator, is used to hold the

## Intermediate results of arithmetic and

## logical operations.

This means that after each operation the

Result is automatically stored in accumulator

and next operations it uses.

All operations like addition, subtraction, AND, OR, etc are done using the Accumulator and another value from memory

It helps to reduce the number of registers needed, and makes it CPU design simple and faster

8c

same as 7(b)