## ALL Mid Solution

# Computer Anchitecture

Sapation : (30)

Mid: 20-21 (Book page=60, problem 2.9)

Chaving probority level AXBXE

1) Assuming that ENIAC had the capability to have multiple vaculary tubbs tubes in the ON and OFF state simultaneously, why is his representation a avastebul" and what range of integer values could I we represent using the 10/20/30 vacuum to

Solution: This representations is wasteful because to represent a single decimal digit from 0 to 9 we need to have ten tubes

If we could have an arbitary number of these tubes ON at the same time, then those same tubes could be treated as binarry bits.

With 10/20/30 vacuum tubes on bits, we can ne present 2n patterns (210, 220, 230) on tom (for exprole 210)

So the range of integer values could we represent using 10/20/30 bit is to to (2n-1). on 1048575

### Mid: 20-21, 17-18, 19-20

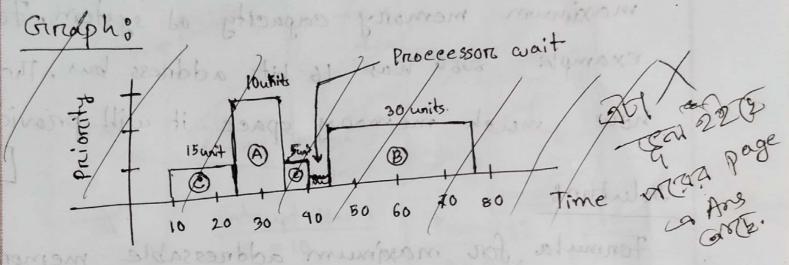

Suppose three intenrupt handlers A, B, and C (having prelority level A>B>e) with Intenrupt Sensice Routine (ISR) 10, 30 and 20 nespectively. Graphically show the transfer of control for intenrupt sequence of C, A and B at time t=10, 25 and 45 nespectively. [10]

Solutions

Given Datu, two is subtracting and sulf is without

interrupt s = A, B, and c

priority = A>B>e

JSR execution time;

A > 10 units, B > 30 units, c > 20 units.

Interrupt sequence (Time);

c occurs at t. = 10

A occurs at t = 25

o occurs at t=43

Now, ther Hene is the graph and explainations

#### Explaination:

when t.=10 c stants execuition. c needs 20 times units (scheduled t.=10 to t=30).

Dut at t=25 A intenrupt because A has higher priority than C, so C is preempted and A stants execuition for 10 times units (till t=25 tot=35) At t=35, A ends execuition and again c stants and Rexecuite the remaining part untill t=40. Then t=40 to t=45 processor remain Idle and at 45 t=45 B start execuition. B

execuite un 30 times unit instill t= 75.

| 1  | 1 |

|----|---|

| 1, | / |

| Subject |       |

|---------|-------|

| Date:   | Time: |

Regarding Address Bus, Bus width determines maximum memony capacity of system. For example 8080 has 16 bit address bus. Then how much memony space it will provide?

Solution:

Formula for maximum addressable memory

momony capacity = 2 Address Bus width x word size

since each address typically neters to wone byte (wond size = 1 byte). So the total memory capacity is  $2^{16} = 65536$  byte = 64 KB.

THE Greath picture of a: no: 2

Users Prioriam  $21+1 = \frac{2^{m}+1}{3}$   $\Rightarrow 61+3=2^{m}+2$   $\Rightarrow 51+3=2^{m}$   $\Rightarrow 12=\frac{1}{3}(2^{m}-3)$  P. TeO

Subject..... User Program e (ISR) A(ISR) intrupt time ISR execution the Proinitys A= 10 units B = 3 ounits B = 45 c = 20 units User Program (C(ISR) A(ISP) 七=29 B (ISR)

Fig: Multiple interrupts

or, average access time

eti excha

= main memony

AMATE TE + MEXITY (MILX MIN

access time

Miss hit Pate of L1 edere

Another formulas

Mid: 17-18, 19-20 (981).

(9) Consider two-level cache with access time 5 nsee and consec respectively. If the hit reation

95% and 75%. Respectively in the two

caches and main memory access time is

250 nsec. What is the effective access time?

Tiz

Solutions

Given that,

LI elicache:

Access time = 5 nsee

Hit reatio, H, = 95%. = 0.95

C2 cache:

Access time, T2 = 80 nsee

Miss ratio, H2 = 75% = 0.75.

Miss ratio, M2 = 1-0.25 = 0.25.

Main memory access time, Tm = 290 nsee tig: Multiple intenunts

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.co

|                                        | TEAT TO XIII + MILK TO XIII + MIL ME THE                                                                                             |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 10                                     | Subject                                                                                                                              |

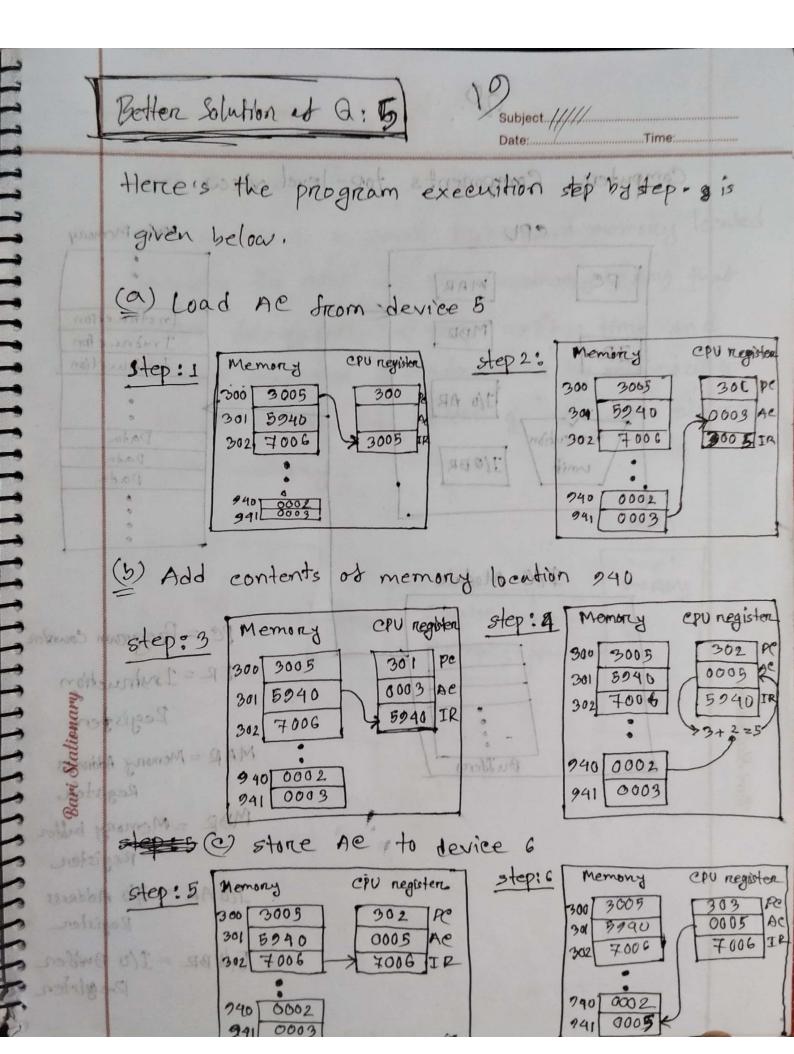

| (-1)(11-1                              | Assume that the next value retnieved from                                                                                            |

| NO SEE                                 | device 5 is 3 and that location 140 contains                                                                                         |

|                                        | a value of 2. [10]                                                                                                                   |

|                                        | Solution: This solution is not good,                                                                                                 |

|                                        | Given & Program Execution Steps: Better Soln at page 19                                                                              |

|                                        | an pige 1)                                                                                                                           |

| 10,0                                   | Steps pe Instruction (IR) Action Ae  Steps pe Instruction (IR) Action  Ae  Steps pe Instruction (IR) Action                          |

|                                        | Steps Pe Instruction (IF)  Steps Pe Instruction (IF)  Load from device 5 > Ac=3 3  1 300 3005 (Load Ac   Coad from device 5 > Ac=3 3 |

|                                        | 1 201 5090 (Add memory Memory location contains 5                                                                                    |

| ozla                                   | 1 2 ( 10 Ae) 2, 60 AC= 3+2=5                                                                                                         |

| A some                                 | 302 7006 (stone Ac to blone AC (5) to Sevice 5  device 6)                                                                            |

| nary                                   | Mid : 20-21,                                                                                                                         |

| Statio                                 | Office A sends 1100                                                                                                                  |

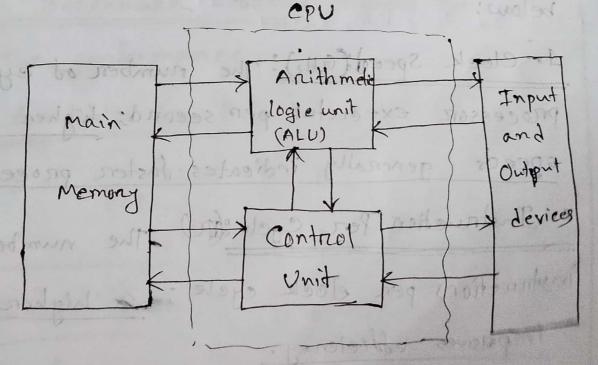

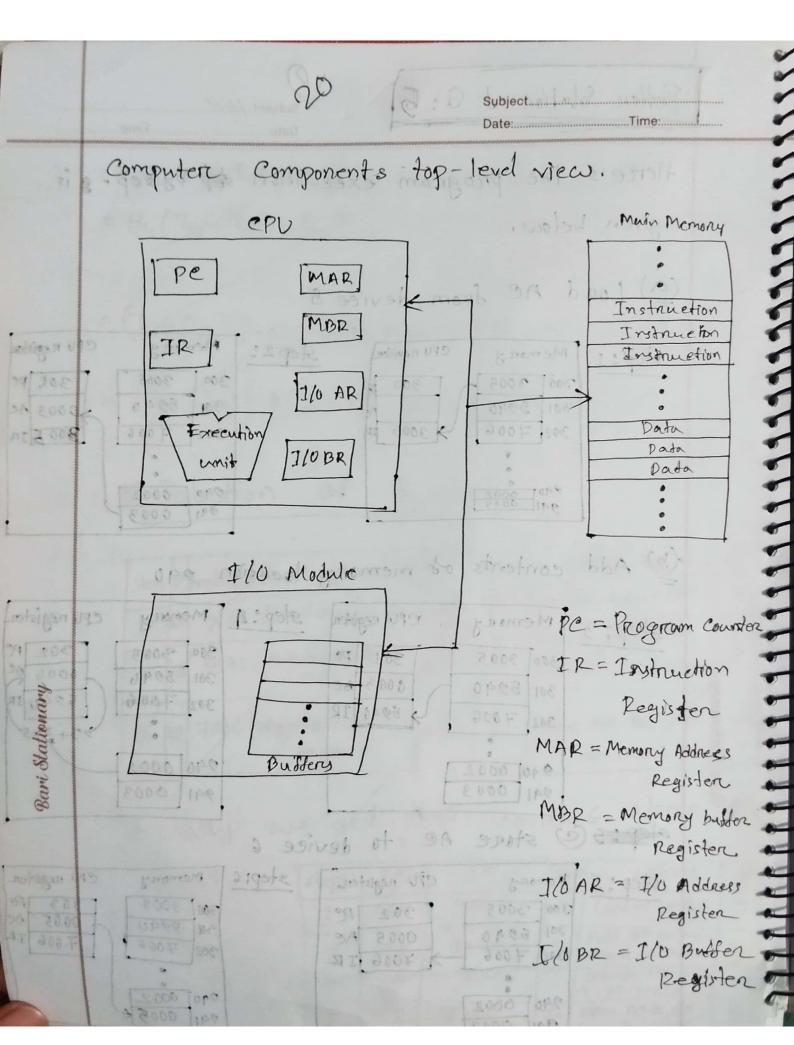

| Bari.                                  | (c) What are the four main components of                                                                                             |

| ************************************** | any general-purpose component? [5]                                                                                                   |

| y 57 1 197                             | The fourt main components are given below                                                                                            |

| -34 54                                 | 1) Main Memory & 11 stones both data and                                                                                             |

|                                        | instructione.                                                                                                                        |

- Anithmetic and logic unit (ALU): Penform anithmetic and logical operations on data.

- Control Unit: Dineets and manages execution of instructions.

- Input and Output (110) Devices: Enable communication between the computer and external environment.

Fig: Four moun companied

0

Subject......Time:

Mid: 17-18

A processor? Explain. [5]

Solution:

underline to may amil

The performance of a processor is determined in several ways. Some ways the are given

below:

1. Clock Speed (GHz): The number of cycles a processor executes per second; higher clock speeds generally indicates faster processing.

2. Instruction Per Cyclestre) the number we instruction per cyclestre ; a higher IPC improves efficiency.

Jasten execution of instructions.

Formula. T = Instruction count (Ie) x CPI x eyele time

Another formulas & , we,

MIPS rate 2 PI × 106

MFLOPS rate = Number of executed floating point

Execution Time x 106

Both of are reommon pendonmance measurement dommula of a processor.

4: Benchmark Scores: Higher the scores, higher

# the pensonmance.

5: Amdahl's law [Parallel processing Speedup):

$$S = \frac{1}{(1-p) + \frac{p}{N}}.$$

Mid: 17-18,19-20

(8) Describbe the bottleneck for decatche

Design. [10]

. Cooke tilt us Miss Rodos A Lia

forces the processor

P.T.O.

The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com

morning traditie, causing delays in data or

| Subject |       |

|---------|-------|

| Date:   | Time: |

A bottleneck referes to a limitation on constraints that show a down the overall performance of a system. It is the weakest point that restricts efficiency, or a system and prevent the system to a achive its full potential.

There are several bottlenecky that impacts of system we faces to design a cache which a impacts on system performance, such as

1. Cache Size vs Access times

Larger caches stone more data but încrease acees time.

2. Cache Hit vs Miss Rate: A high miss rate

Forces the processor to access slower main

memory, increasing latency.

memony tradite, causing delays in data retrieval.

I cache Cohenency: In multi-core system, maintaining cores consistency between caches leads to additional overhead:

- 5. Power Consumption: Larger and faster eaches consume more power.

- 6. Associativity trade-offs: It neduces conflicts but increase lookup time and handware complexity.

Physical Address (24)

= (29 × 20) bytes

2 224 bytes.

Mid: 20-21

(9) We would like to design a cache of 64 kbyte. Main Memory is 16 Mbytes. Coche Block is 4 bytes (2 bit word identifier) and nest of bits is block identifier. Use the concept of dineet mapping address. [10]

Solution: Main memory = 16 Mbytes

(10) When a block that is resident in the cache is to be replaced, there are two cases to consider. Describe the write through and write back. [10]

Solution?

When a block in the cathe is updated or replaced, there are two common write policies:

1. Write-Through;

It updates both eache and main memory simultaneously.

Multiple CPUs can monitorer memory tradfie to keep local CPU up to date.

The Lots of traffie

It Slows down writer and bogus write through cachest.

Bari Stalionary

rid may substructed to its of sub ovier

\*

# 2. Unite Back:

The Updates initially made in cache only.

Enche block is replaced.

到 I/O must access main memory through cache. 如 When an update occurs, a dinty bit associated aith the line is set.

Mid: 20-21

(11) It is possible to build a computer which uges only static RAM. This would be very dost and would need no cache. Analyze its cost.

Solution: Using only static RAM (SRAM) in a computer would be extremly fast but highly expensive due to its B-transistor per bit design compare to DRAM's 1-transistor, 1-copyriston

design. SRAM consumes more power, takes more less density to stone data in a writ, complex design and haiden to space, and timits storage capacity making it

impractical for the large memory system.

Instead more modern computers use a memory

hierarchy (SRAM cache + DRAM main memony)

to balance speed and east efficiently.

Overall SRAM computer would be Sast than

other but it is imposimpractical for

large seale implementation for itis. high

cost and complexity.

\_ x \_

EAT = (Hit Patioli x Access & time (1) + (Miss Ratio (1

x/Hit Patio (2 x Access time) (2) +

(Miss Ratio LI x Miss Ratio (2 x Main memon)

= (HL, × TL) + (1-HL) × HL2 × TL2 }+ (1-HL) (1-HL2) Tm)

He, The + Her That He, Her Tra + (1- Her He, Hez) The

|    | 11 | 9 |

|----|----|---|

| 21 | 1  | A |

|    |    |   |

| Subject |       |

|---------|-------|

| Date:   | Time: |

discourses &

DRAM VS SPAM ?

What is cache?

Detween the CPU and main memory (RAM) that stones strequently memory acress time and improve processon & pendonmance by minimazing delays caused by fetching data strom slowers main memory.

conficuent simple design plans some plans of many land and seed plans of many land and seed plans of many land and seed plans of many land and m

due to refresh slower eyele Power Consumption Consume more power cost Cheaper (1 transiston + 1 capusiton) per bit storage capacity Capacity Used main memory Usage (2 AM) Bari Stationary Density Higher density, & ston more data per unit simpler design Hiremind, 5

SRAN

|     | oubjectTime:                      |

|-----|-----------------------------------|

| 0   | dans si tax                       |

|     | if solono A to                    |

| 9 9 | SRAM                              |

| 1   | Foster and no nednesh             |

| 340 | Is needed.                        |

| 2   | Consume less power                |

| 5   | Expensive (6 transisters) pen bit |

| ·   | lower eapacity                    |

| 1   | Used cache memony                 |

| re  | less data per unit                |

|     | less data per unit                |

|     | complex degign and                |

|     | hander to manufacture             |

|     |                                   |

|     |                                   |

|     |                                   |

Hallowery. -5

Heckler-10

matador - 3