#### (DLD) Latches

Latch? Latches are the basic builting blocks of any flip flop and they are capable of holding 1 bit whit necessary. Latch [Flip-flop]

NOR Latch & NAND gote Laten?

[ counter [ Resiston

The SR Latch is a cincuit with two-cross-coupled NOR gates/ two cross-coupled NAND gates and two imputs labeled & for 'Set' and R for 'Reset' Outputs an and an is are the complement of each

other. X 0 0 0

\*\* A Flip-Flop is a capable of storing one stable state the output 0 on 1 (it is called bi-state multi-vibrator.).

bihany storage device bit of information. In a of a flip-stop is either

ΑΛΑΙΙ ΑΒΙ Ε ΑΤ **Onebyzero Edu - Organized Learning, Smooth Career** The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onek

an the area as the custon NORS an+1 An 0 ON 0 0 O NON G 1 hey Q, ATTE 0 + Fur mp 99 Dr 1 0 1 1 lip-flup Car memory as site att imput 123,113 tanina output. 123ma anao fuzar 125 (2) an que an 220133 often complement. 2122 an brane triesuit output 12200 a for a conta an. abeled & dout gran tomot thushis after stragt pand Brocontrolo key, 125ma, mer mai ma nh An+1 5 R Q. 0 0 Konshid 0 1 C route noton m 0 0 1 1 ~ ( stotesteder - ikhens stuste -id 12 1

AVAILABLE AT The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

SR - Slip-flop

SR Slip-Slop: It is a Slip-dlop with a floor inputs, one S(set) and another is P(Reset). Set -15 basically indicates set the Slipdop which means complement of output 1 and reset do 1 rehard a teristics et set (output = 0). ! clock pulse is supplied to operate the Here a Slip Flop . Excitation table Fixme Forned Table Cincuit diagram Block diagram: input R ontput + CLK Dot 5 On th An R S ruth table? 0 0 0 0 9 D 0 0 20 0 1 0 0 1 O 3 1 0 0 1 10:22 0 3 1 0 X 0 1 6 1 1 7

SR-SLip. Jup also It is digeligeli Sni ON O bs'm sr 10 00 9 01 11 4 4 6 ms 1 q! 00 × 6 11,5 0, t.M. PENK 01 characteristies equation. Less 6000 F. ( o = tugtero ) ann'z pares stat, r'an; selva 19019 Excitation tuble Table Functional S anti an It diagtern X 0 Qn+1 ()5 S 0 an 1 0 0 0 C 1 0 1. 0 diagram. State O alder S1211 0 0 SR=00 aa aa 512 21 0 01 SR 200 10 SREDI SR = 01

ΔΥΔΙΙ ΔΒΙ Ε ΔΤ The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

D Slip - Slop The D (Duta / Delay) Slip-Slop, tracks the input I and produce the same value as at output sin Stip Hop when highers I and & fied together. 3 Qn CIK A (2321) Qn. na 150 Chrth a ON anton 1L Qu any Qn P an+ O 3 0 0 0 0 0 Jandk 6 0 0 C 0 az sam-千 0 0 0 input 314 0 Ô 217 7 0 1/24,0 21/25 0 In put istant 310 0 155 FC G D12517 J-K Stip-Flop H = IFNO

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroe

T (togale) Ship Slop The T (toggle) Stip-Slop is a compense of flip-flop and can be obtained from J-K flip-flop when inputs J and k are same tied together. Q. CIC an anan K any an 0 6 ()Jand Kaa n () didderent input 0 0 0 0 27 al 21 4 2013 Ô J 93 612/20 0 T STS Fall, 0 0 Qual = J D Qu

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.co

## Explain how a NAND/NOR latch store a bit. What is their limitation? (20-21, 19-20) [3]

#### Answer:

A NAND/NOR latch can store a single bit of information (0 or 1) using cross-coupled logic gates. In those latch the inputs are indicated by S(set) and R(reset) and outputs are indicated by  $Q_n$  and  $|Q_n$ .

The process of storing bit of NAND Latch:

- 1. When S = R = 1, the latch maintains the current state.

- 2. When S = 0 and R = 1, the output = 1 means set the latch.

- 3. When S = 1 and R = 0, the output = 0 means reset the latch.

Limitations:

- 1. When S = R = 0, the output = invalid and latch throws error.

- 2. When  $Q_n = |Q_n|$  = same bit of value (0 or 1), the latch level-triggered and it goes to race condition.

The process of storing bit of NOR Latch:

- 1. When S = R = 0, the latch maintains the current state.

- 2. When S = 0 and R = 1, the output = 0 means reset the latch.

- 3. When S = 1 and R = 0, the output = 1 means set the latch.

Limitations:

- 1. When S = R = 1, the output = invalid and latch throws error.

- 2. When  $Q_n = |Q_n|$  = same bit of value (0 or 1), the latch level-triggered and it goes to race condition.

## 2. What are the limitations of S-R flip flop? How can be resolved these? (20-21, 18-19)[4]

The limitations and resolutions of S-R flip-flop are given below:

#### **Indeterminate State:**

- Limitation: When both inputs (S and R) = 1, the output becomes unstable.

- Solution: Use a J-K flip-flop, which toggles instead of becoming undefined when both inputs are high.

#### Lack of Clock Control:

- Limitation: Basic S-R flip-flops are level-triggered and may not reliably capture input changes.

- Solution: Use a Clocked S-R flip-flop or a D flip-flop for stable, edge-triggered responses.

#### **Glitches from Asynchronous Inputs:**

- Limitation: Small timing differences can cause unstable output.

- Solution: Use a Clocked or Master-Slave flip-flop to synchronize inputs and prevent glitches.

#### Limited in Complex Circuits:

- Limitation: The S-R flip-flop's simplicity restricts its use in advanced circuits.

- Solution: Use more versatile flip-flops like D or J-K flip-flops in complex designs.

| R       | Qn                                                        | Qn+1                                                                                                                                                                                                                                                                                                       |

|---------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (reset) |                                                           |                                                                                                                                                                                                                                                                                                            |

| 0       |                                                           | invalid                                                                                                                                                                                                                                                                                                    |

| 0       |                                                           | invalid                                                                                                                                                                                                                                                                                                    |

| 1       |                                                           | 1                                                                                                                                                                                                                                                                                                          |

| 1       |                                                           | 1                                                                                                                                                                                                                                                                                                          |

| 0       |                                                           | 0                                                                                                                                                                                                                                                                                                          |

| 0       |                                                           | 0                                                                                                                                                                                                                                                                                                          |

| 1       |                                                           | unchanged                                                                                                                                                                                                                                                                                                  |

| 1       |                                                           | unchanged                                                                                                                                                                                                                                                                                                  |

|         | R<br>(reset)<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>1<br>1 | R         Qn           0         0           0         0           1         0           0         0           1         1           0         0           1         1           1         1           1         1           1         1           1         1           1         1           1         1 |

| S (set) | R       | Qn | Qn+1      |

|---------|---------|----|-----------|

|         | (reset) |    |           |

| 0       | 0       | 0  | unchanged |

| 0       | 0       | 1  | unchanged |

| 0       | 1       | 0  | 0         |

| 0       | 1       | 1  | 0         |

| 1       | 0       | 0  | 1         |

| 1       | 0       | 1  | 1         |

| 1       | 1       | 0  | invalid   |

| 1       | 1       | 1  | invalid   |

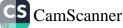

## **3. Define race-around condition in J-K flip-flop? How can you overcome the problem? Explain with appropriate figure and waveforms. (20-21, 19-20) [5]**

#### Answer:

In JK Flip-flop, if J=K=1, and if clk=1 for a long period of time, then Q output will toggle as long as CLK is high, which makes the output of the flip-flop unstable or uncertain. This problem is called race around condition in J-K flip-flop.

The truth table of the J-K flip-flop is given below:

| J | K | Q <sub>n+1</sub> |  |

|---|---|------------------|--|

| 0 | 0 | Qn               |  |

| 0 | 1 | 0                |  |

| 1 | 0 | 1                |  |

| 1 | 1 | invalid          |  |

|   |   |                  |  |

The invalid at J = K = 1 is known as the race-around condition.

To overcome this condition, a Master-slave JK filp-flop is used.

#### **Explaination:**

- 1. The master-slave flip flop is constructed by combining two JK flip flops.

- 2. These flip-flops are connected in a series configuration. In these two flip flops, the 1st flip flop work as a "master", called the master flip flop, and the 2nd work as a "slave", called the slave flip flop.

- 3. When the clock pulse is true, the slave flip flop will be in the isolated state, and the system's state may be affected by the J and K inputs. The "slave" remains isolated until the CP is 1. When the CP is set to 0, the master flip-flop passes the information to the slave flip-flop to obtain the output.

#### 4. How a NAND/NOR latch store a bit? (19-20) [2]

#### Answer:

#### NAND Latch

- 1. Setup: Made of two cross-connected NAND gates.

- 2. Inputs: S(Set) and R(Reset).

- 3. Operation:

- Set: S = 0 and R = 1, makes output Q = 1.

- Reset: S = 1, R = 0, makes output Q = 0.

- Hold: S = 1, R = 1, keeps the last value of Q, storing a bit.

#### NOR Latch:

- 1. Setup: Made of two cross-connected NOR gates.

- 2. Inputs: S(Set) and R(Reset).

- 3. Operation:

- Set: S = 0 and R = 1, makes output Q = 0.

- Reset: S = 1, R = 0, makes output Q = 1.

- Hold: S = R = 0, keeps the last value of Q, storing a bit.

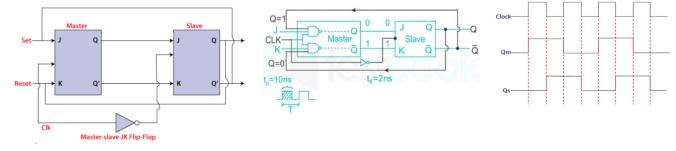

#### 5. Explain the synchronous/clocked S-R filp-flop with waveforms. (19-20) [4]

#### Answer:

A **synchronous/clocked S-R flip-flop** is a type of S-R (Set-Reset) flip-flop that includes a clock signal to control when the inputs S (Set) and R (Reset) can affect the output. The flip-flop changes its state only during a specific clock edge (usually the rising edge) if the clock signal is active, making it synchronous with the clock.

#### Waveform:

The waveforms in Figure show how a clocked S-R flip-flop operates:

- 1. Initial State: All inputs are 0, and Q is assumed to be 0.

- 2. First Clock Pulse (Point a): With both S and R at 0, the flip-flop remains in its current state (Q = 0).

- 3. Second Clock Pulse (Point c): S = 0 and R = 0, so the flip-flop sets Q to 1.

- 4. Third Clock Pulse (Point e): S = 0 and R=1, so the flip-flop clears Q to 0.

- 5. Fourth Clock Pulse (Point g): S=1 and R=0, setting Q to 1 again.

- 6. Fifth Clock Pulse: S=1 and R=0 again, so Q remains at 1 since it's already high.

- 7. Invalid Condition: When S=R=1, this creates an ambiguous state and should be avoided.

| S | R | Q <sub>N</sub> | Q <sub>N+1</sub> |

|---|---|----------------|------------------|

| 0 | 0 | 0              | 0                |

| 0 | 0 | 1              | 1                |

| 0 | 1 | 0              | 0                |

| 0 | 1 | 1              | 0                |

| 1 | 0 | 0              | 1                |

| 1 | 0 | 1              | 1                |

| 1 | 1 | 0              | -                |

| 1 | 1 | 1              | -                |

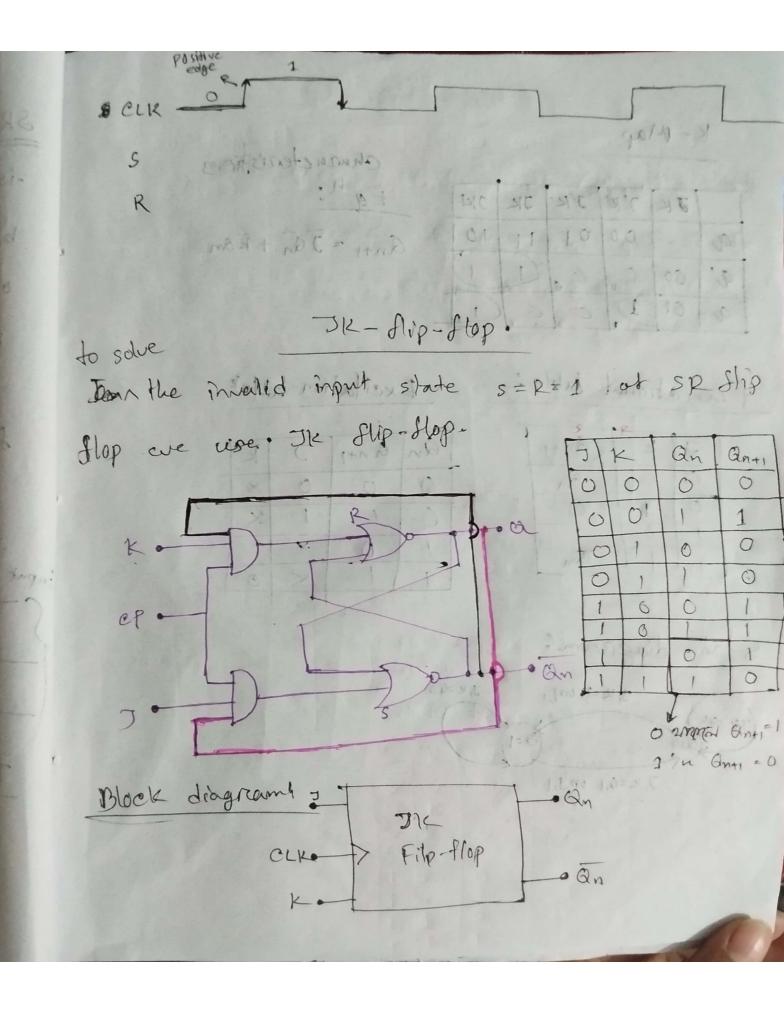

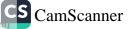

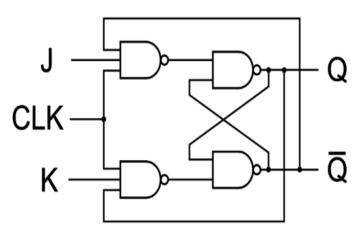

## 6. What is a flip flop? Explain the function of a JK flip flop with suitable circuit diagram. (18-19) [4]

#### Answer:

A flip-flop is a fundamental memory element in digital electronics that can store a single bit (0 or 1) of data.

#### J-K Flip-Flop

The **J-K flip-flop** is an improvement over the S-R flip-flop, as it eliminates the indeterminate (invalid) state that occurs when both Set (S) and Reset (R) inputs are 1. Instead, the J-K flip-flop includes feedback that allows it to toggle its output when both inputs are high.

| Truth Table |   |                |                         |  |

|-------------|---|----------------|-------------------------|--|

| J           | К | Q <sub>N</sub> | <b>Q</b> <sub>N+1</sub> |  |

| 0           | 0 | 0              | 0                       |  |

| 0           | 0 | 1              | 1                       |  |

| 0           | 1 | 0              | 0                       |  |

| 0           | 1 | 1              | 0                       |  |

| 1           | 0 | 0              | 1                       |  |

| 1           | 0 | 1              | 1                       |  |

| 1           | 1 | 0              | 1                       |  |

| 1           | 1 | 1              | 0                       |  |

#### **Function and Operation**

The J-K flip-flop's operation depends on the values of J, K, and the clock:

When Clock is Low: The flip-flop maintains its previous state; inputs J and K have no effect.

When Clock is High (or on the rising edge, in edge-triggered designs):

- J = 0, K = 0: The flip-flop holds its previous state.

- J = 0, K = 1: The output Q is reset to 0,

- J = 1, K = 0: The output Q is set to 1.

- J = 1, K = 1: The output Q toggles (switches between 0 and 1) with each clock pulse.

event amplification faster and Basic bilgma trans

Binany Addition, Subtraction, Mailfippreadion transmos

an divitions addition: +1 [] 0 carry corry below: 1 Retation between Band & is given Lets Examples eve. 1100 + 1110 [] ] 010 []] ] 010.001 [ ) <= cariny covery SIA- THE OLA abstituting appin appin un get Subtraction:  $\frac{1}{1} = 0 = 0 = \frac{1}{1} = 0$ (10/27) 175 1-0 ALE Condition numercalor and E devision of 10m2 ] 0 = 01 - 0 [ 2n0] \$1-1-10= K(200) R= x . This is the neguined netationship. Αναίι αρι ε ατ The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroe

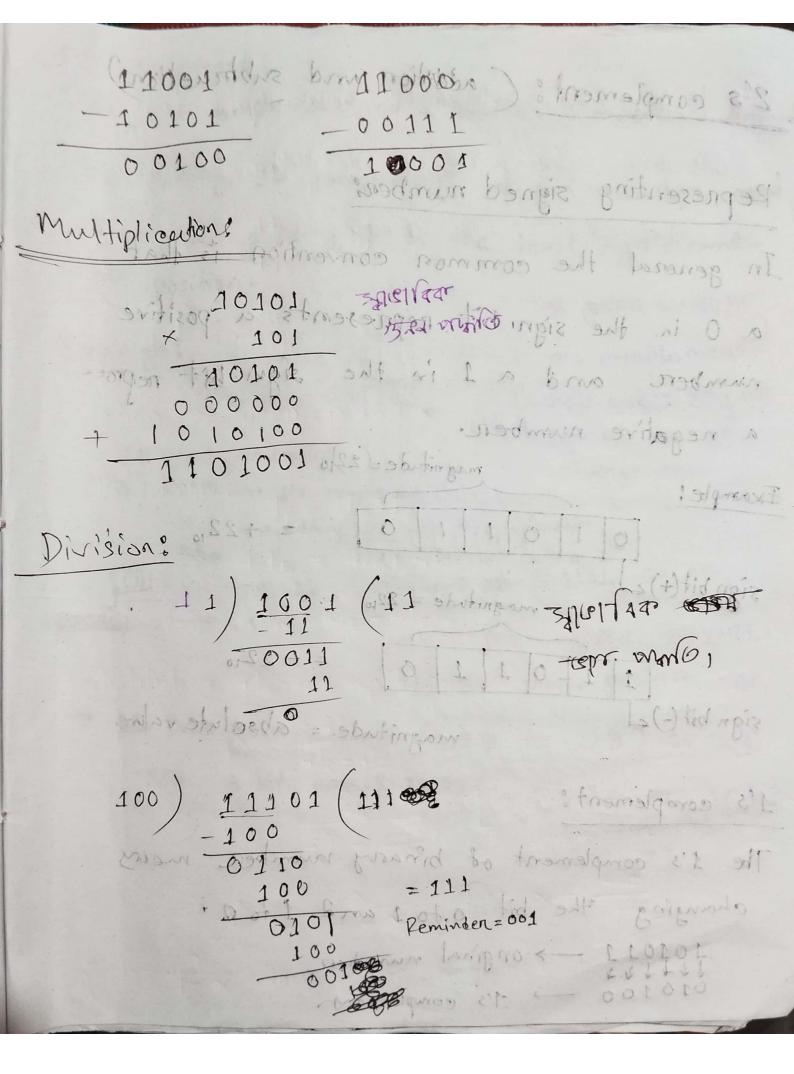

2's complement: (addition and subtruction)

Representing signed numbers:

In general the common convention is that

a 0 in the sign bit, represents a positive

number and a 1 in the sign bit repre-

a negative number.

Example:

$$0 \pm 0 \pm 1 \pm 0 \pm 1 = 0$$

$1 \pm 0 \pm 1 = 0$

$1 \pm 0 \pm 0 \pm 0$

$1 \pm 0$

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

2's complement: The 2's complement of a bineing number is formed by taking 1's complement of the number, and then a adding I to the least-significant. bit position. 100 per \* (2017 ET 34.0 2011 /200 Example: 56 56 50 6.10 12261 32.16 8 2's complement 9510 = 101101 (उकामने स्ट्रांग्रे - राज्य जान sign bit at sign 101101 -> oroginal change 2(21, word 010010 -> 1's complement 10000 + 1 -> adding 1 with 1's complement (010011 > 2's complement of 1011012 on 4510 positive that negative - 204 (ME) 7-4510 negative and positive any \* Die Desimal number (127 to -128) 019 313 2(21 8-bit farmi 175173 7734, 233 (alar 270) 16 bit. 4- (-) bid NER

CS CamScanner

HI Using 2's complement system perdonin the Sollowing operations: (19-20) [2] D-65-88 (D)+ 34+55 D -65-188 128 0 0 4 69 32 16 \$ complemen. 12 0 0 0 2) (-65) + (-88) se tid mai 9 shipers - 101101 NOW, 1975 0100001 65 9 amos 10111110 -> 1's complement 10111111 2's complement 65) Sign bit (-) OV TO 2B914 000 88 PC-001411 1's comple stat priver injoi 10101000 -> 2's -88)complement sign bit(-)

of this result again. - 69 - 88 Eleo - over flow conting · So, 1 11 1 1111 001100111 00000000 1 0011000 -> 1's complement + 1/00 0000000010011001 2's complement 100 11 10 1 or, [10011001 sign bit(-) convent this negult to decimal which NOW 18-153 010 ay we expect 60010101111111111 34+55  $34 \rightarrow 00100010$ >00110111 + 5 5 111 >01011001 89 í. 10 sign bit (+) 1/1 2000 The result of 34+55 in 2'3 01011001. 189 00 Αναίι αρι ε ατ

Onebyzero Edu - Organized Learning, Smooth Career

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

Adert (1) Boolean expression: Sum = AB + AB = A DB Adders. AB Jobbo Hut Half eiddert carry = ST-Decoder, Encoder, half adden state? 2 5 2 9 2 F e nelded Q. exemp 9 7 ज्यानी जित्य राखा -> ( Del 5 @ Block diagnour . Joh 1117 expression Brac (VI) adden? apol 0 7.17 diagram (2) more a Half adder (S) FURA (C) Block diagram: 00 table : S Full do adden 0 Ô 0 3

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.co

Trenth table:

#- \* input a 2122 2251 input Output A (217 277 (22) Ca Sum Carry B A O 0 0 0 O Sum = 0 and carry = ] 1 1 0 0 0 0 O 0 2731 1 0 C 222 124 021 2 12171 273 0 0 Ø X 1 Ò 0 TOTAT Sum 21, carry 21 1 0 1 1 0 272, 1 1 1 1

Boolean expression:  $S = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$   $= \overline{ADC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$   $= \overline{C}(\overline{AD} + \overline{AB}) + \overline{C}(\overline{AD} + \overline{AB})$   $= \overline{C}(\overline{ABB}) + \overline{C}(\overline{ABB})$   $= \overline{C}(\overline{ABB}) + \overline{C}(\overline{ABB})$   $= C \oplus (\overline{ABB})$   $= C \oplus (\overline{ABB})$   $\therefore Sum = C \oplus (\overline{ABC})$ Canny =  $\overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$   $= A\overline{BC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$   $= A(\overline{BC} + \overline{BC}) + BC(\overline{A} + \overline{A})$  $= A(\overline{BC} + \overline{BC}) + BC$

> AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu

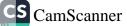

Logie gate:

ΔΥΔΙΙ ΔΒΙ Ε ΔΤ The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com) CamScanner

Parallel adders. Basie and carran added OZCar elo'TE ANAN CARTON CIN = O RATCHE, 21 3.2211 1373 Carry m 101 M 1 3 DE FRANKE) 01 Input corry bra 1000 sure GARY 21103 A: 1 0 1 i= index-3 2 10 4 10  $B_i \rightarrow$ 1 1 0 0 110 1 1 1 0 Sum -0 19 ( P. 10) P. P. man Output carry > O 0 bit TEN 2 bit on an Parallel addent mechanism. Pt 31 wow for Finally adde 01 Ubit a -27.27(51 \* n-bit para binary parallel adder CARO AT 3131 ET Panallel. adders attact 1 (13 09-15 ON2 CITA PARAllel 3 2133 22 22461 MAL EREN Block diagram," (4-bit panallel adder) addition. JB3 Ba 1B A2 Jabba la liezag Ca FAID Cont F/A F/A FA SW sum

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroe

bit binary parallel adders H/A and 米ンケ 23 202724 Noter ATER OTER PAR MARCH EE to A H/A (man) 2(21 ANAN (22/2) Cin = 0 21/20,21 मिलि 3 22 ना मिलि 221 F/A OFIA H/A F/A sum Et Parallel adder / subtractor using 2's complement System: Undenstand the Ic 791383, It is a 4-bit panallel adder, 9-bit panallel adder 27 internal mechanism Already Crentz JC 23 Cara 22 Bar CIVI (520) am. ( it bit paraelle set dea 9-bit panallel adder Co 746883

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzero

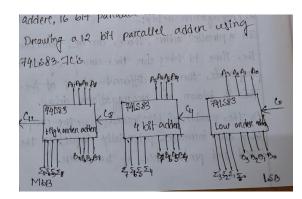

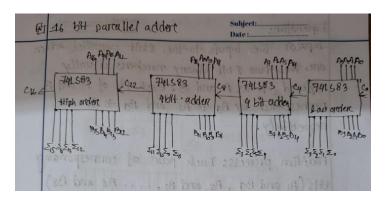

## 7. What is the limitation of a parallel adder? Using 74LS83 ICs draw a 16/12 bit parallel adder. (20-21, 18-19) [3]

#### Answer:

The main limitations of a parallel adder are:

- 1. **Carry Propagation Delay:** Each bit addition depends on the carry from the previous bit, which causes a delay as it moves through each stage of the adder. This delay increases with the number of bits, slowing down the adder.

- 2. Complexity: Larger adders need more gates and connections, increasing cost and size.

- 3. Limited Scalability: Due to the increased delay and complexity with each additional bit, parallel adders are not efficient for high-bit operations, such as in 32-bit or 64-bit processors.

## 8. Explain how 2's compliment system can facilitate arithmetic operation in digital computing. (20-21, 18-19) [3]

#### Answer:

The **2's complement system** is widely used in digital computing to represent negative numbers and simplify arithmetic operations, particularly subtraction. Here's how it facilitates these operations:

#### 1. Unified Addition and Subtraction:

- In 2's complement, subtraction can be performed as addition, simplifying the circuit design.

- To subtract a number, simply add its 2's complement (invert all bits and add 1).

- This means a single adder circuit can handle both addition and subtraction, making it efficient for hardware design.

#### 2. Single Representation of Zero:

• Unlike other signed number systems, 2's complement has only one representation for zero, reducing ambiguity in calculations.

#### 3. No Special Circuit Needed for Sign:

- Positive and negative numbers can be added directly without separate circuits to handle the sign, simplifying the hardware.

- Overflow conditions are handled automatically when the sum exceeds the responsible range.

#### 4. Efficient Use of Bits:

• In a fixed number of bits, the 2's complement system maximizes the range of representable values, allowing both positive and negative values in a simple format.

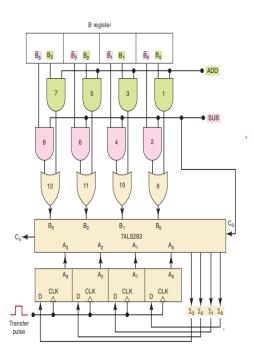

### 9. Draw a parallel adder/subtractor using 2's complement system and explain its operation. (20-21) [6]

#### Answer:

Here's a simplified description of the operation of the parallel adder/subtractor circuit:

- 1. Addition Mode (ADD = 1, SUB = 0):

- Control Signal: SUB = 0 disables certain AND gates

(2, 4, 6, 8) to hold their outputs at 0, while ADD = 1 enables AND gates (1, 3, 5, 7) to pass the B<sub>0</sub> to B<sub>3</sub> values.

- **Operation**: The B register values B<sub>0</sub> to B<sub>3</sub> pass through OR gates to the adder, where they are added to A<sub>0</sub> to A<sub>3</sub>.

- **Carry-In**:  $C_0 = 0$ , so no additional carry is added.

- **Output**: The sum appears at outputs S<sub>0</sub> and S<sub>3</sub>.

#### 2. Subtraction Mode (ADD = 0, SUB = 1):

- Control Signal: ADD = 0 disables certain AND gates (1, 3, 5, 7), while SUB = 1 enables the other AND gates (2, 4, 6, 8) to pass B<sub>0</sub> and B<sub>3</sub> values.

- **Operation**: The B register values  $B_0$  to  $B_3$  pass through OR gates to the adder, but with  $C_0 = 1$ , effectively converting B to its 2's complement.

- **Output**: The adder performs A-B and the difference appears at outputs S<sub>0</sub> and S<sub>3</sub>.

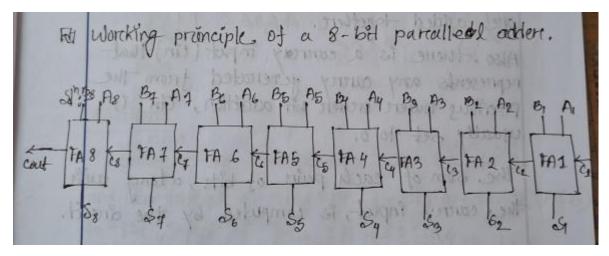

#### 10. Design and explain the working principle of an 8-bit parallel adder. (19-20) [6]

#### Answer:

An 8-bit parallel adder is a digital circuit that performs the addition of two 8-bit binary numbers in parallel. It adds each pair of corresponding bits from the two operands simultaneously, producing an 8-bit sum output.

#### **Inputs:**

The inputs to the 8-bit parallel adder are two 8-bit binary numbers, typically referred to as A and B. Each bit of A and B is represented as  $A_0$  to  $A_7$  and  $B_0$  to  $B_7$ , respectively.

#### **Addition Process:**

Each pair of corresponding bits ( $A_i$  and  $B_i$ ) is added together. Additionally, a carry-in ( $C_{i-1}$ ) from the previous bit addition is included in the calculation. The carry-in ( $C_{i-1}$ ) is usually set to 0 for the least significant bit (LSB). The sum of each pair of bits, along with the carry input, is computed by the adder circuit.

#### **Outputs:**

The outputs of the 8-bit parallel adder are the 8-bit sum ( $S_0$  to  $S_7$ ), representing the result of the binary addition.

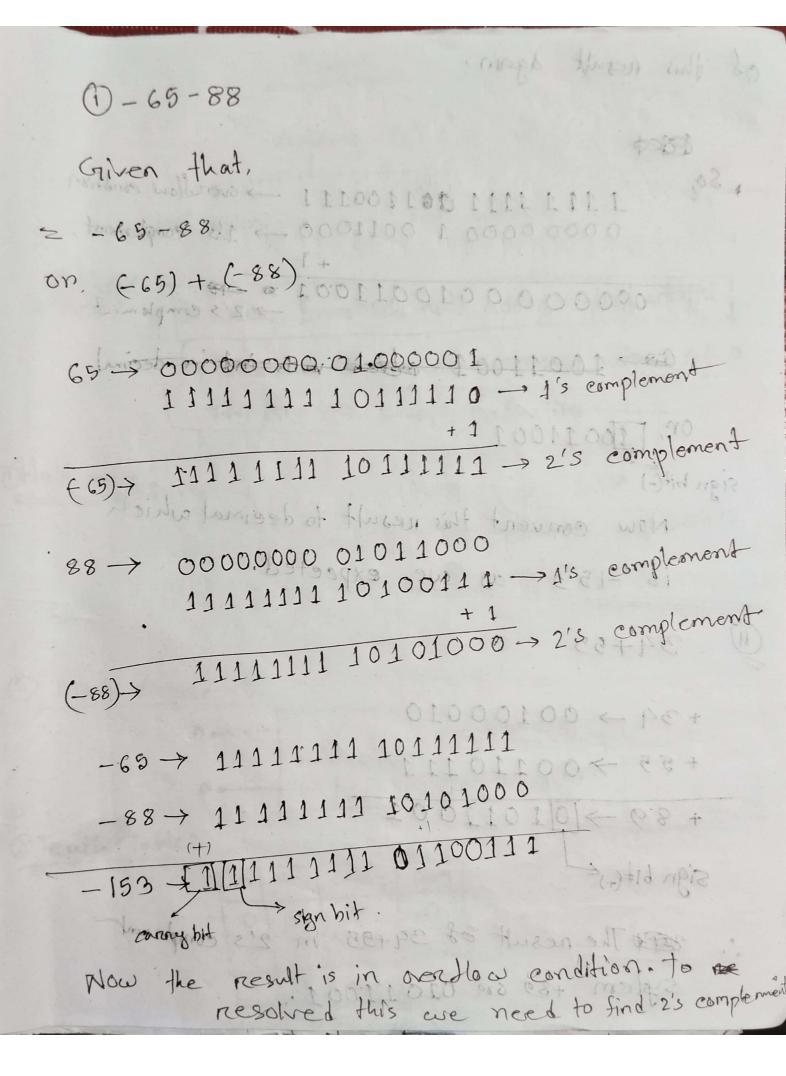

## 11. Using 2's complement system performs the following operations:(19-20) [2]i) -65-88ii) 34+55

1)-65-88 Given that, 1111001100 1111 1 11 -69-881 - 0001100 1 0000 on. (-65) + (-88) 100110010000000 1311111110111110 - 1's complement +1 1111111111 -> 2's complement F (5) >  $88 \rightarrow 00000000 01011000$  $1111111110100111 \rightarrow 1's complement$ 11111111 10101000 -> 2's complet (-88)→ -65 -> 11111111 10111111  $-88 \rightarrow 11111111 10101000$ 1111111101100111 10111111101100111 > sign bit. ant The nearly of 34,495 - 11 Now the result is in averylow condition. to me resolved this are need to find 2's complet

this result again. 03 top · So, > over How 1 11 1 1111 001100111 00000000 1 0011000 -> 1's compleme +1 1001100 or, [10011001 sign bit(-) Now convent this result 8 -153 as we expee - GCO10 34+55 +34 -> 00100010 +55 >00110111  $+ 89 \rightarrow 01011001$ sign bit (+) t 2000 The result of 394+55 in system +89 00 01011001. 1 Harrist

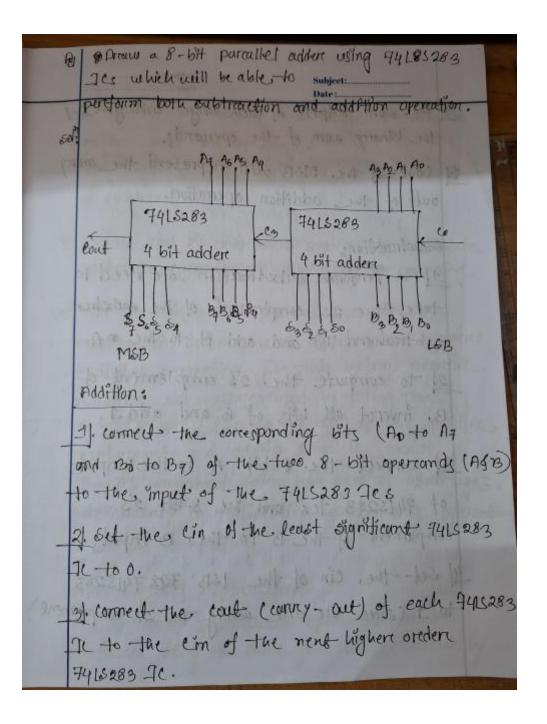

# 12. Draw an 8-bit parallel adder using 74LS83 ICs, which will be able to perform both subtraction and addition operation. (19-20) [4] Answer:

Sing and and Subjects 4. The sum adpets of each stage will give my the binarry sum of the operandy. 51 Cout of the MSB will represent the cantry out of the addition operation. Substraction. 1) To perform substitution, we need to take the a's complement of the substrea subtrahend (B) and add Pt to the onA 21 to compute the 2's complement of B, invert all bits of B and add 1. 31 connect the 8-bit A to the Ainputs of 7415283 the and the 8-bit 2's complement of the B to the B inputs Al set the cin of the LSB. 7415283 to I (since we arre adding the 2's complement) The to the can of the areas lighter ander

5] connect the cast of each stage to the cin of the new nigher stage. The sum outputs well give us the nesself of subtraction. with reality and remaine the

AVAILABLE AT: Onebyzero Edu - Organized Learning, Smooth Career The Comprehensive Academic Study Platform for University Students in Bangladesh (www.onebyzeroedu.com)