# Computer Peripheral & Interfaces

## (Introduction ) from A Sahu Deptt. of Comp. Sc. & Engg. IIT Guwahati

**PRESENTED BY: GROUP-01**

**MEMBERS:**

- Sarna Das (20CSE001)

- Nazma Akter Ani (20CSE002)

- Tanvir Ahmed (20CSE004)

- Md. Asad Mondal (20CSE006)

- Zahidul Islam Rony(20CSE030)

- Jannatul Ferdaus(20CSE025)

**PRESENTED TO:**

Dr. Tania Islam

Assistant Professor, Dept of

CSE, University of Barishal

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Outline

- Introduction

- Linux Kernel Split View

- Motivation

- Dolby Digital

- HD Cinema

- MI TECH 2010: Nvidia GPUs

- MI Tech 2010: USB 3.0

- MI Tech 2010: Bluetooth 4.0

- Peripherals Controller Migration

- Why Migration?

- Moorestown Platform

- Intel Centrino Processor

- Intel Atom Processor

# Introduction

## Computer system

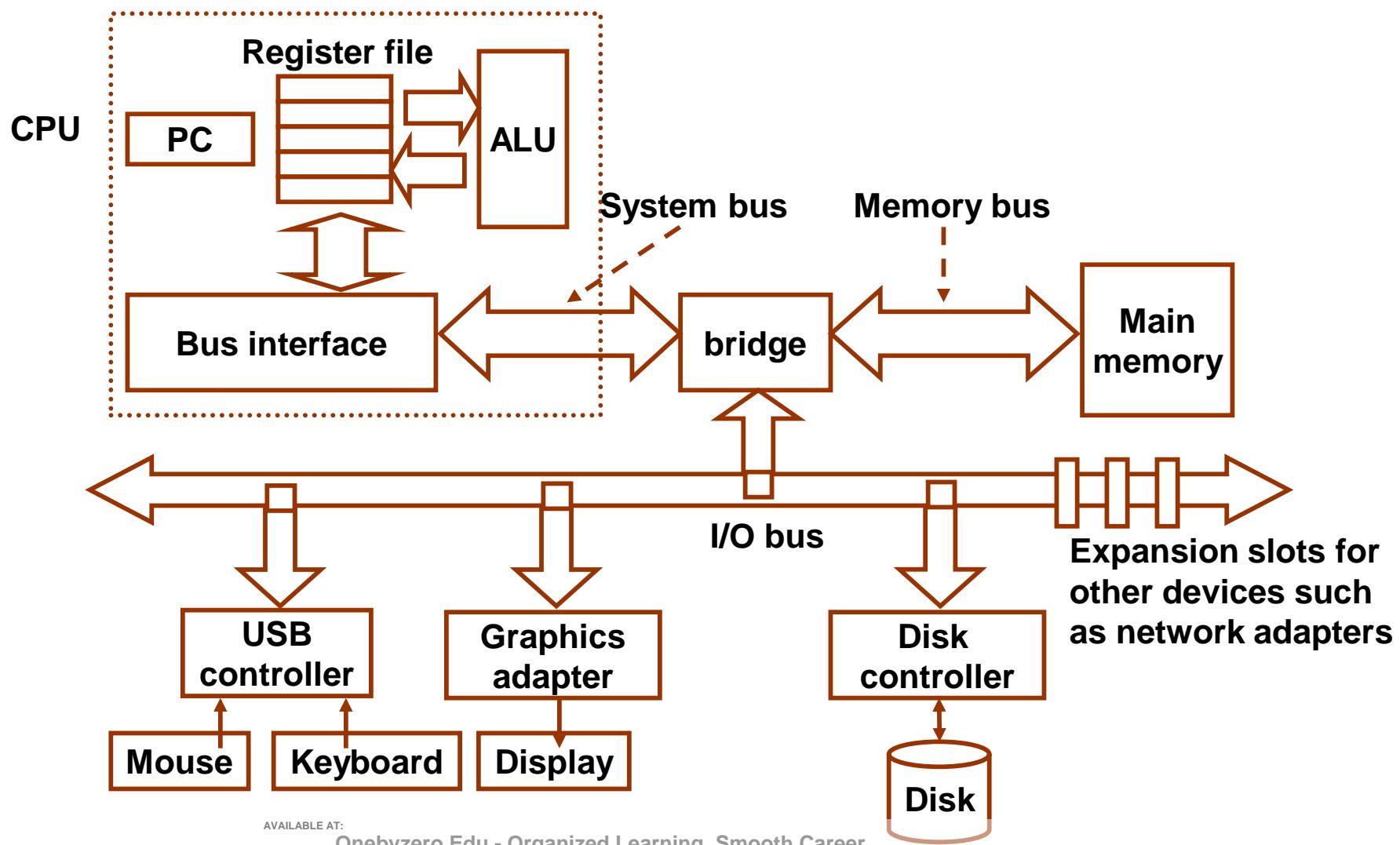

1. Internal {Processor and Memory(RAM)}

2. Peripheral ( Disk, Display, Audio System, Ethernet Card)

### Interface:

- connects Internal and peripheral devices.

- Two Types:

**Intermediate Hardware:** Nvidia GPU Card, Creative Sound Blaster

**Intermediate Software:** Nvidia GPU Driver, Sound Blaster Driver Software

# Introduction

## More Examples

### *Intermediate Hardware*

- Timer: Measures time intervals.

- Counter: Counts the number of events

- DMA (Direct Memory Access): directly access memory

- USB (Universal Serial Bus): Used for connection, communication and power supply

- UART (Universal Asynchronous Receiver/Transmitter): Handle asynchronous serial communication.

- Peripheral Controller: Manages peripheral devices.

# Introduction

## More Examples

### *Intermediate Software/Programs*

- Device Driver (Linux): A specific type of software that allows the operating system to control hardware.

- Assembly Code: Low level programming language

### **Peripheral Component Interconnect (PCI):**

- Audio card

- VGA (Video Graphic Array) card

- Ethernet Card

*Low level signal + high level C code (Combination of these two helps the interface to control hardware)*

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

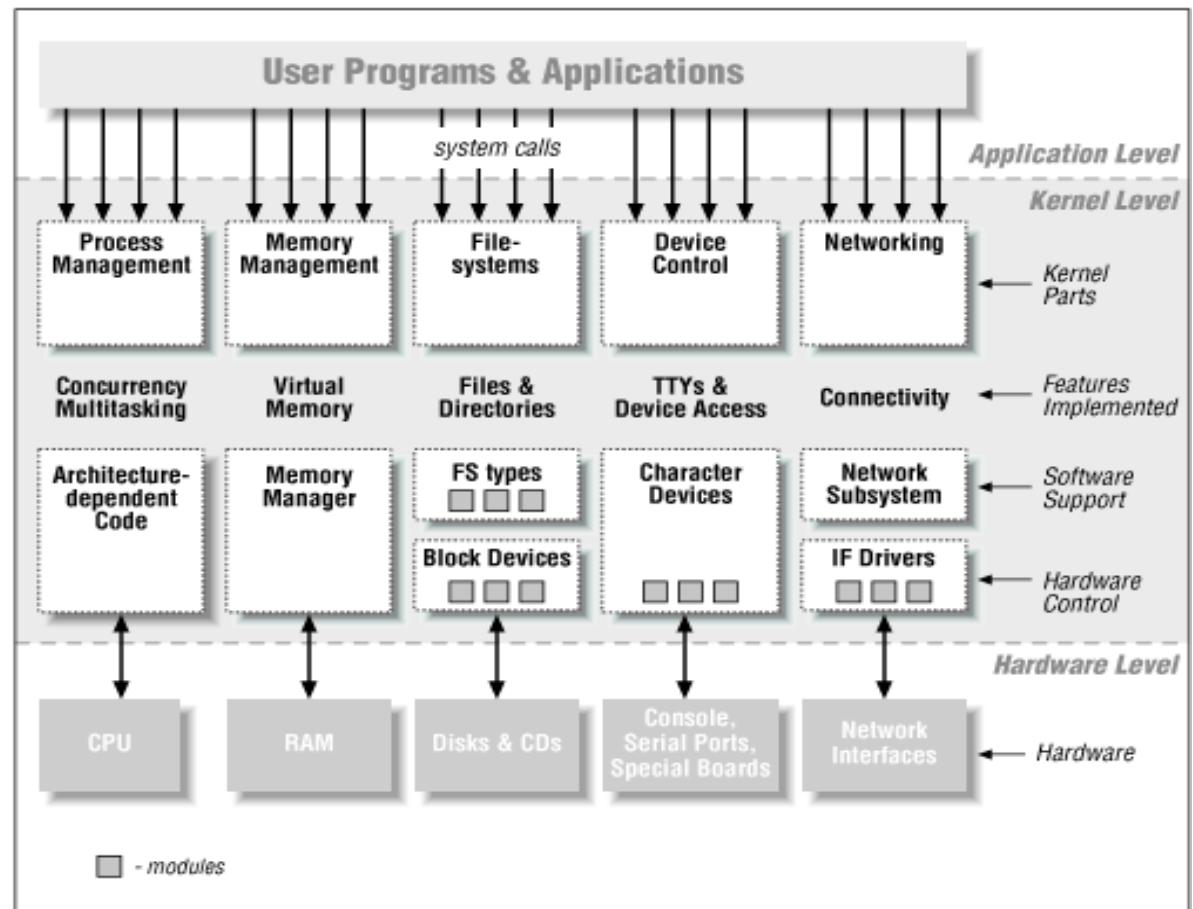

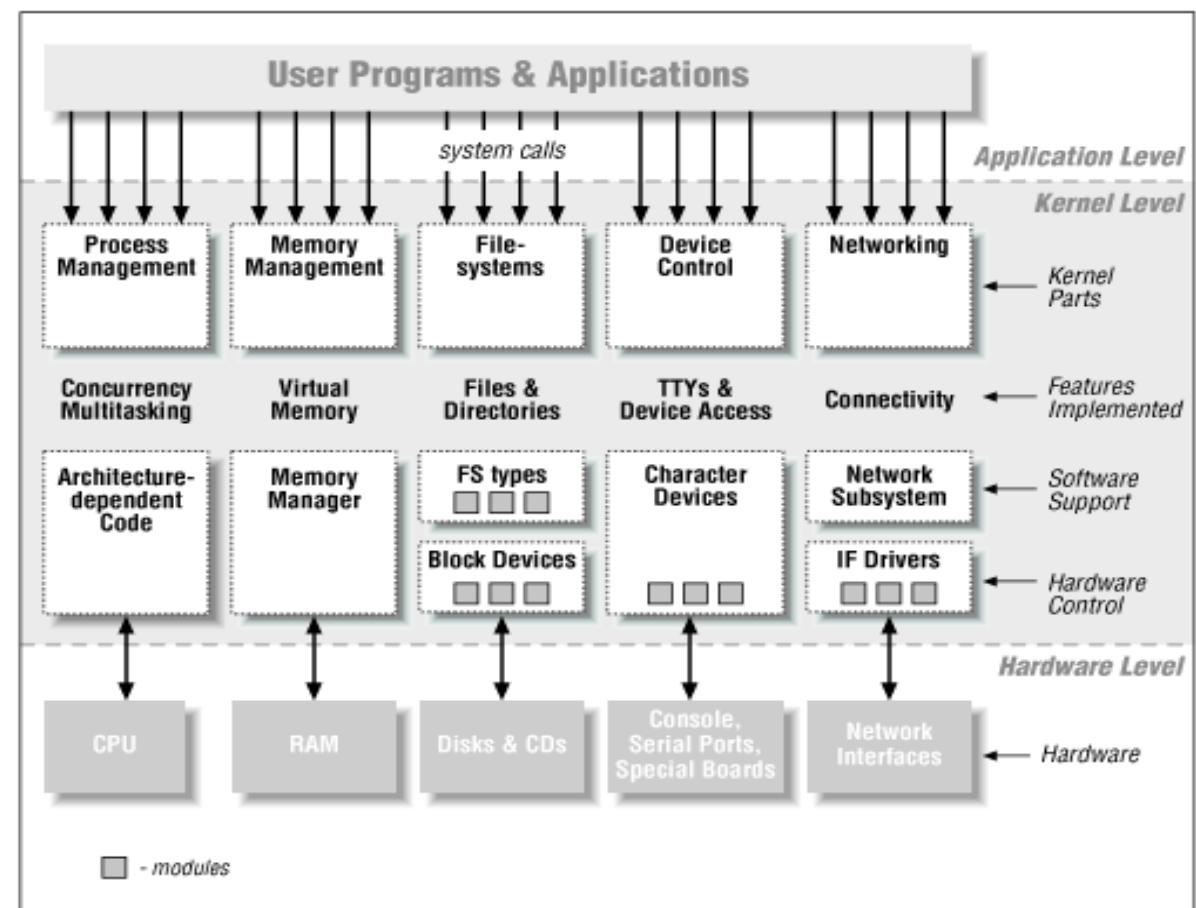

# Linux Kernel Split View

In a Unix system, several concurrent processes attend to different tasks. Each process asks for system resources, be it computing power, memory, network connectivity, or some other resource. The kernel is the big chunk of executable code in charge of handling all such requests. Though the distinction between the different kernel tasks isn't always clearly marked, the kernel's role can be split, as shown in Figure

A split view of the kernel

# Linux Kernel Split View

These 5 parts of Kernel split execute various roles.

1. Process management

2. Memory management

3. Filesystems

4. Device control

5. Networking

A split view of the kernel

# Motivation

## 1. Knowledge: both hardware & software

| Hardware                          |                             | Software                                            |                                      |

|-----------------------------------|-----------------------------|-----------------------------------------------------|--------------------------------------|

| Internal                          | External(Peripheral)        | System                                              | Application                          |

| Motherboard, CPU, RAM, Hard Drive | Mouse, Keyboard, Microphone | Operating System, Language Processor, Device Driver | Web browser, facebook, Instagram etc |

## 2. Exact interface: Architecture & OS

| Architecture                                                                                                                                     | OS                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| <ul style="list-style-type: none"><li>• Von-Neumann Architecture</li><li>• Harvard Architecture</li><li>• Instruction Set Architecture</li></ul> | Windows, linux , macOS, Unix, Android etc |

# Motivation

## 3. Used in many places (Computer + Embedded System)

- An embedded system

A specialized computer designed to perform specific tasks within a larger device or system, like controlling a washing machine or a car's engine.

## 4. Highly paid job in industries

Intel

NVIDIA

IBM

## 5. Low level signal + Device drivers

| Low level signal                     | Device drivers                                                                |

|--------------------------------------|-------------------------------------------------------------------------------|

| directly control hardware components | enable the operating system to communicate with and control hardware devices. |

| 0 or 1, High voltage or Low voltage  |                                                                               |

# Motivation

## 6. Knowledge of simple peripherals

(Display, Audio, Disk drives, Ethernet) In connection with 8085/8086

| Display                                | Audio                                   | Disk Drivers                    | Ethernet                                                               |

|----------------------------------------|-----------------------------------------|---------------------------------|------------------------------------------------------------------------|

| memory-mapped I/O ,<br>port-mapped I/O | PWM (Pulse Width<br>Modulation) signals | programmed I/O or<br>DMA        | transmitted/received<br>via I/O ports or<br>memory-mapped<br>registers |

| 7-segment displays or<br>CRTs          |                                         | floppy disk controller<br>(FDC) | Intel 82586                                                            |

## 7. Peripheral are powerful than main computing

### *Advanced Peripherals & Technologies*

- Linux/Windows Device Drivers.

- Dolby Digital Stereo, HD Cinema, Dolby Atmos (present), USB 3.0, USB 4.0 (present).

- Graphics cards (Nvidia with 480 core) , RTX (Ray Tracing eXtreme)- 40 series, GTX (Giga Texel Shader eXtreme)-16 series by NVIDIA (present).

# Motivation

## 8. Use of old technology in newer devices

- Intel Atom processor (PII technology with modification)

- Use of winXP in mobile; may be obsolete for PC in very short

## 9. Combining peripheral controller in main computing for low power

1. Intel Centrino have wireless controller functionality inside processor chip

2. Intel atom 45x have DDR2 memory controller + Graphics controller in inside processor chip in very short

# Dolby Digital

Dolby digital audio placement technology can deliver high-quality audio even at lower bitrates and realistic surround sound compared to plain audio

## Dolby Stereo:

- It is a unified brand for two completely different basic systems: the Dolby SVA (stereo variable-area) 1976 system used with optical sound tracks on 35mm film, and Dolby Stereo 70mm noise reduction on 6-channel magnetic soundtracks on 70mm prints.

- Humans have two eyes to measure the depth of image which can be called a stereo image.

Stereo Ear Phone

# Dolby Digital

## Dolby Lab:

- It supports up to 5.1 channels of surround sound.

- It can deliver more directional sound effects than stereo audio.

- 5 ear-level speakers & 1 subwoofer. 5 channels have 20 Hz - 20,000 Hz. 1 channel have 20 Hz - 120 Hz.

- 5 ear-level channels are 3 front channel (Left, Center, Right) provide clean dialogue & accurate placement of on-screen sounds & the 2 surround channels (Left surround, Right surround)

- Low Frequency channel (LFE) called ".1 channel," delivers deep, powerful bass effects that can be felt as well as heard.

- Max bit rate: 560 bit/s

# Dolby Digital

## Dolby HD:

- It supports up to 7.1 channels of surround sound.

- 7 ear-level speakers & 1 subwoofer.

- Max bit rate:18MB/s

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# HD Cinema

## Video specification:

- Frame rate . 30 frames/sec

- 1 Hour video size (Based on resolution) .

- VGA (Video Graphic Array) (640 x 480) pixels: Uncompressed size: 199 GB, Compressed size: 450 MB

- 720P (1280 x 720) pixels Uncompressed size: 597 GB Compressed size: 1.2 GB

- 1080P/i(1920 x 1080) pixels Uncompressed size: 1.35 TB Compressed size: 2.4 GB

## File formats:

- MP2: Typically used for DVD & broadcasting. It is an older but reliable format.

- MP4: One of the most common video formats, ideal for streaming.

- MKV: It can contain multiple audio, video, subtitle tracks, all within a single file. It's often referred to as a 'Matryoshka' or 'Nested doll'.

# HD Cinema

## **Cinema resolution:**

- Old 2k(2048×1080): It is used in digital cinema, specially for older or low budget production.

- New 4k(4096×2160): It is standard for high end digital cinema offering extremely high video quality.

## **Projection technologies :**

- Digital Light Processing (DLP): It is developed by Texas Instruments. This technology uses micro-mirrors to project images. It is widely used in projectors, including cinema projectors for bright & vivid images.

# HD Cinema

## Projection technologies :

- **Liquid Crystal on Silicon (LCOS):** It is a reflective display technology that allows rapid switching of light for display projection purposes. It is a better version than LCD & DLP technology. It produces very bright & high resolution images used in large high definition screens.

- **Silicon X-tal Reflective Display (SXRD):** It is the evolution of LCOS technology, developed by Sony. It offers high resolution & contrast, used in high end projectors & cinema display

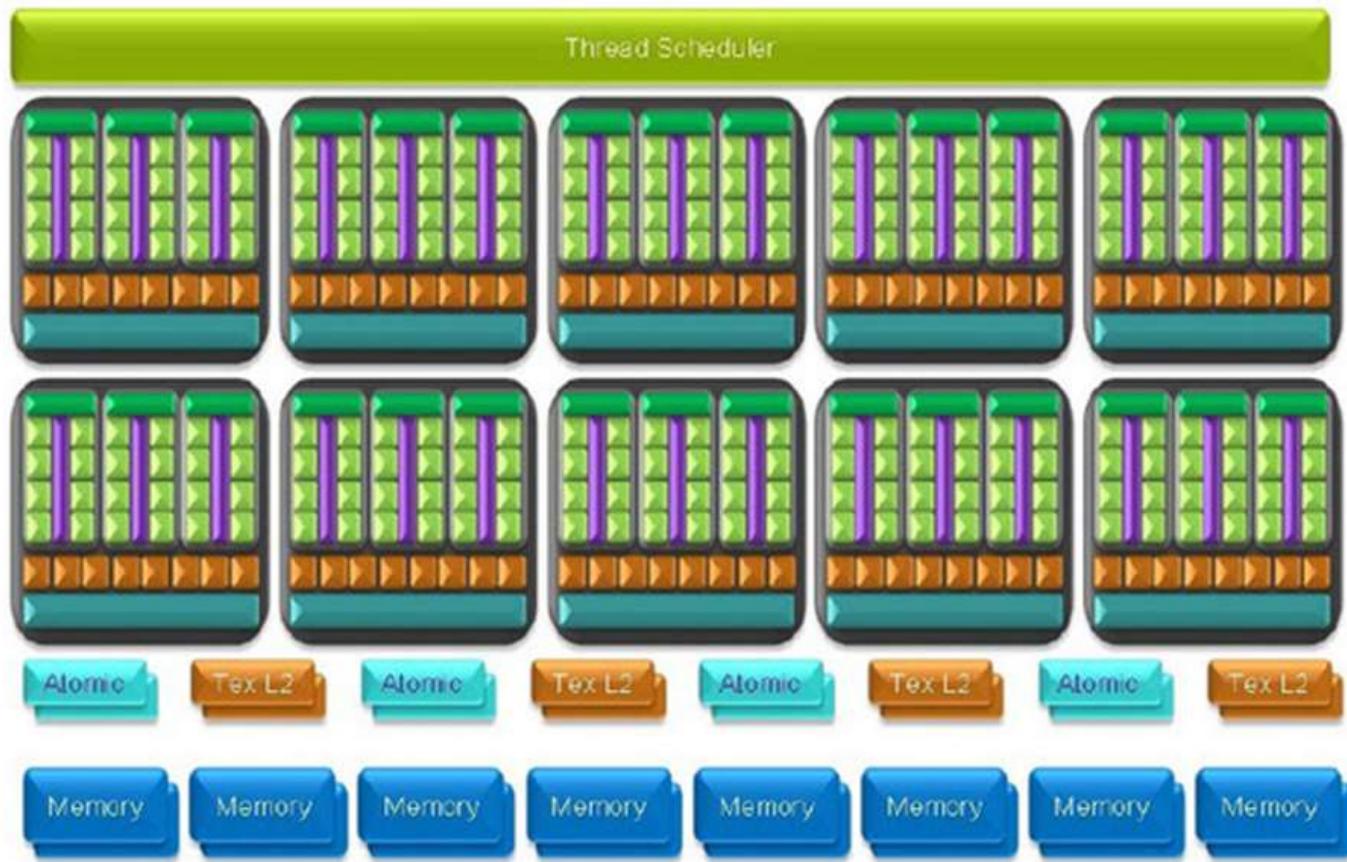

# MI TECH 2010: Nvidia GPUs

Nvidia GPUs are powerful graphics processing units designed primarily for rendering images, videos, and animations for display

## Structure:

- **CUDA (Compute Unified Device Architecture) Cores:** The grid-like structure in the diagram represents CUDA cores, which are parallel processing units within the GPU.

# MI TECH 2010: Nvidia GPUs

- **Thread Scheduler:** The green bar at the top labeled "Thread Scheduler" is responsible for managing and dispatching tasks (threads) to the CUDA cores.

- **Atomic Units** (in light blue) are responsible for managing operations that require access to shared memory without interference from other processing threads, ensuring data consistency.

- **Tex L2** (Texture Level 2) units (in orange) handle texture data, which is used in rendering images and graphics.

- **Memory:** The blocks labeled "Memory" (in blue) represent the GPU's memory,

# MI TECH 2010: Nvidia GPUs

## Key Features:

- ❖ **Nvidia GTX295:** Equipped with 480 CUDA cores, which are parallel processors used for tasks such as rendering graphics, computational simulations, and other data-intensive tasks.

- ❖ **VGA (Video Graphics Array):** Capable of supporting resolutions up to 2048x1536. Supports dual-monitor setup, providing flexibility for multiple displays.

- ❖ **HD Cinema & MKV File Playback:** Supports high-definition cinema viewing and can play MKV files, which are commonly used for high-quality video storage.

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# MI Tech 2010: USB 3.0

USB 3.0 is a major upgrade over previous USB versions, offering significantly faster data transfer speeds and better efficiency in handling devices connected to computers.

## Key Features:

- ❖ **SuperSpeed Bus:** USB 3.0 introduced the "SuperSpeed" mode, which allows for much faster data transfer compared to USB 2.0..

- ❖ **Enhanced Host Controller Interface (EHCI):** With USB 3.0, the EHCI was enhanced to support higher speeds and better performance.

**Register-level Interface:** Maintains compatibility with older USB 2.0 devices while also supporting the new features of USB 3.0.

**SATA HDD Integration:** USB 3.0 could work with SATA hard drives, allowing for faster data transfers, particularly for external storage devices.

- ❖ **Transfer Mode:** USB 3.0 supports transfer speeds up to **5.0 Gbit/s**, which is roughly **400 MB/s**. The previous version speed was 480 Mbit/s.

# MI Tech 2010: USB 3.0

## Technical Aspects:

- **8B/10B Encoding:** A method of encoding data to ensure reliable transmission by balancing the number of 1s and 0s sent over the cable.

- **Linear Feedback Shift Register (LFSR) Scrambling:** This technique helps in reducing electromagnetic interference, which can affect the quality of data transmission.

- **Spread Spectrum:** This is used to spread the signal over a wider bandwidth, which also helps in reducing interference and improves signal integrity.

- **Receivers and Equalization:** Advanced receivers in USB 3.0 include mechanisms for periodic signaling and dynamic equalization, ensuring that data is accurately received and processed, even in challenging conditions.

# MI Tech 2010: Bluetooth 4.0

Bluetooth 4.0, introduced in 2010, marked a significant advancement in wireless communication technology, offering improved features like higher data transfer rates, lower power consumption, and enhanced connectivity options.

## Key Features:

- 1. Classic Bluetooth:** Operates at a frequency of 2.4 GHz using Frequency Hop Spread Spectrum (FHSS). Offers a typical range of about 1 meter and data transfer rates of up to 3 MB/s.

- 2. Bluetooth High Speed:** This feature is based on Wi-Fi technology, allowing for much faster data transfer rates than previous versions of Bluetooth. Ideal for applications requiring quick data exchange.

- 3. Bluetooth Low Energy (BLE):** A major addition in Bluetooth 4.0, BLE is designed for devices that need to operate on very low power.

# Peripherals Controller Migration

## Overview

- What do meant by peripherals controller migration

- Why is the Peripherals Controller Migration necessary

- Architecture of the Moorestown platform

- Intel Centrino Processor and Intel Atom Processor with functionality

# Peripherals Controller Migration

## ✓ Cards on motherboard

- ❖ Graphics

- ❖ Audio

- ❖ Modem

## ✓ Onboard

## ✓ Inside Processor

- ❖ Graphics

- ❖ Memory Controller

# Why Migration?

## Key Aspects :

- ✓ Hardware Upgrade

- ✓ Platform or Architecture Shift like x86-based system to ARM based system

- ✓ Consolidation

## Why Important?

- ✓ Performance Improvement: Offer better performance, more features, or support for newer peripherals.

- ✓ Cost Efficiency: Can more efficient use of system resources.

- ✓ Compatibility: Older controllers may no longer support new peripherals, necessitating a migration to maintain compatibility.

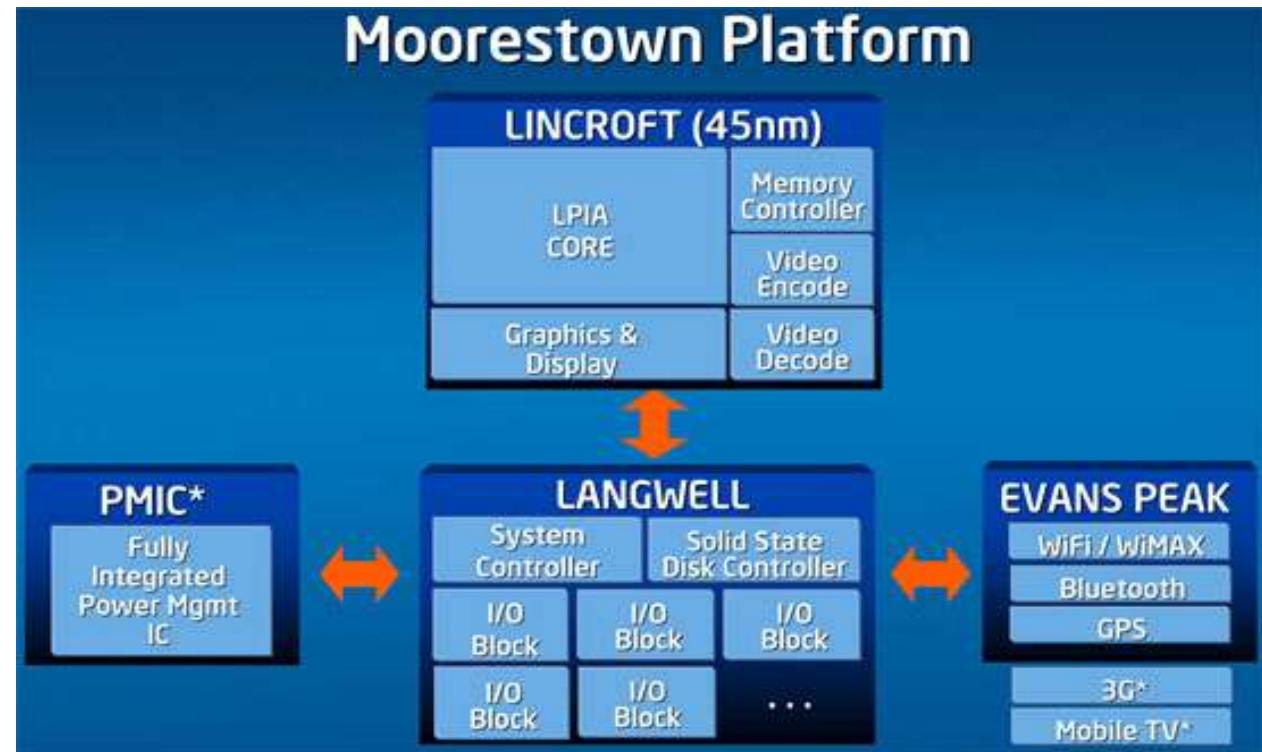

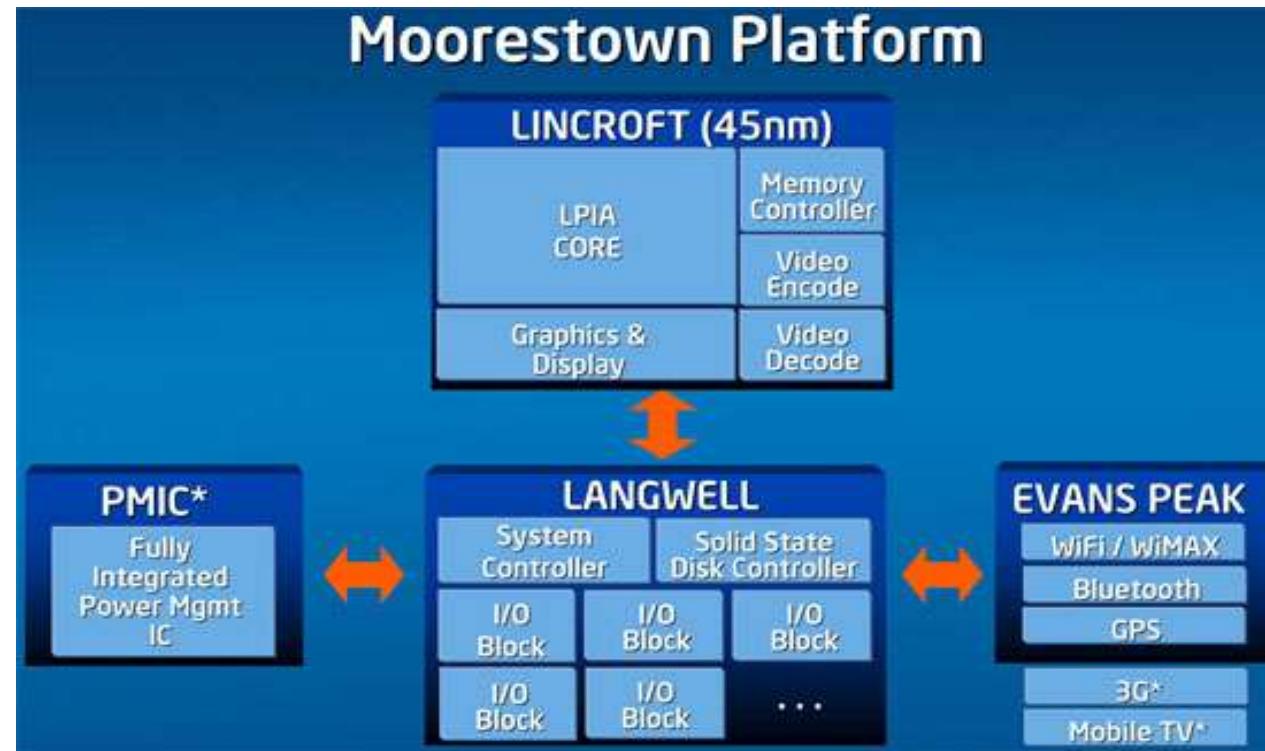

# Moorestown Platform

- **Lincroft System on a Chip (SoC):** It features a LPIA (Low Power Intel Architecture) CPU core (Silverthorne derivative), on-die graphics and on-die memory controller.

- **Langwell South Hub :** Langwell is composed of a system controller, solid state disk controller and I/O blocks for things like USB or audio.

# Moorestown Platform

- **PMIC** : The Power Management IC (PMIC) plays a mystery role at this point. Intel is just revealing that it handles power management for the platform yet not fully detailing its active roles.

- **Evans Peak Networking**: The final component of Moorestown is the Evans Peak networking hub, which is made up of Intel and non-Intel silicon.

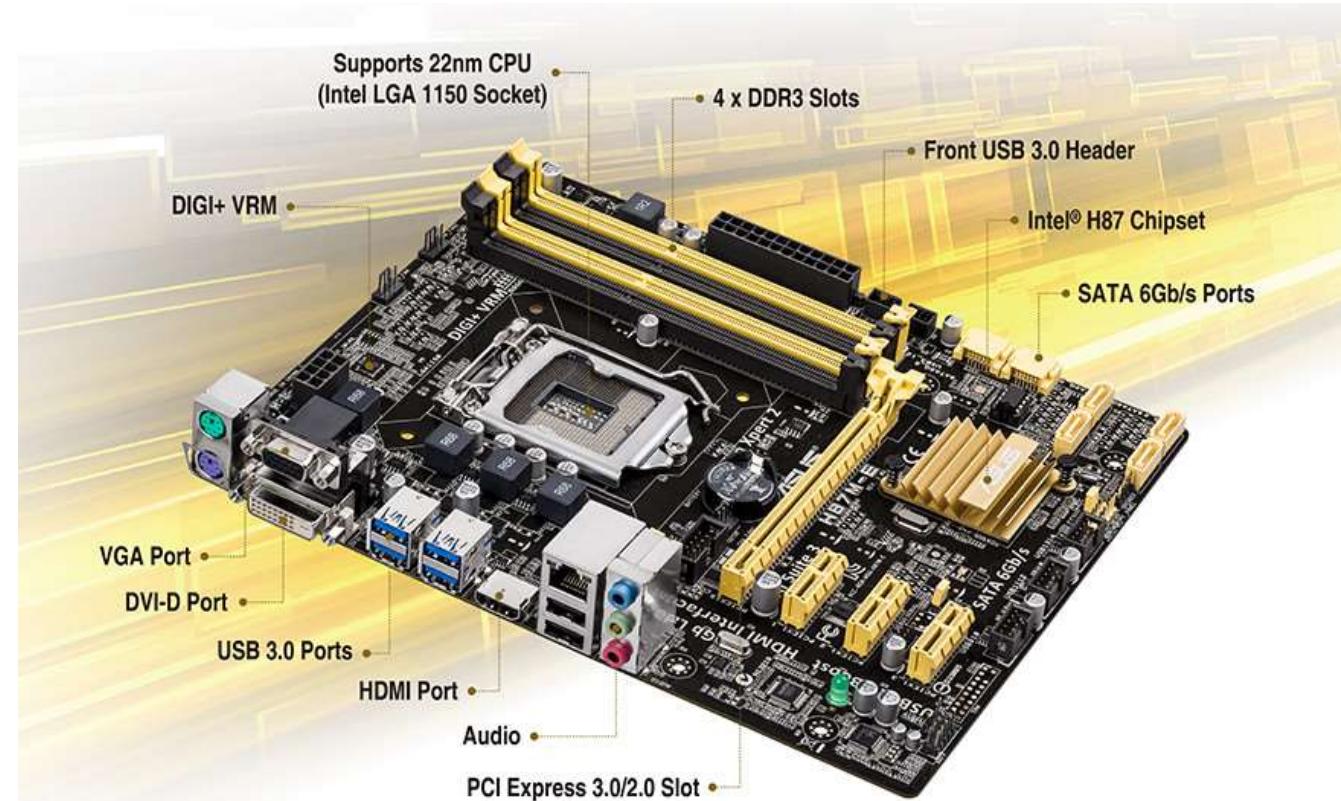

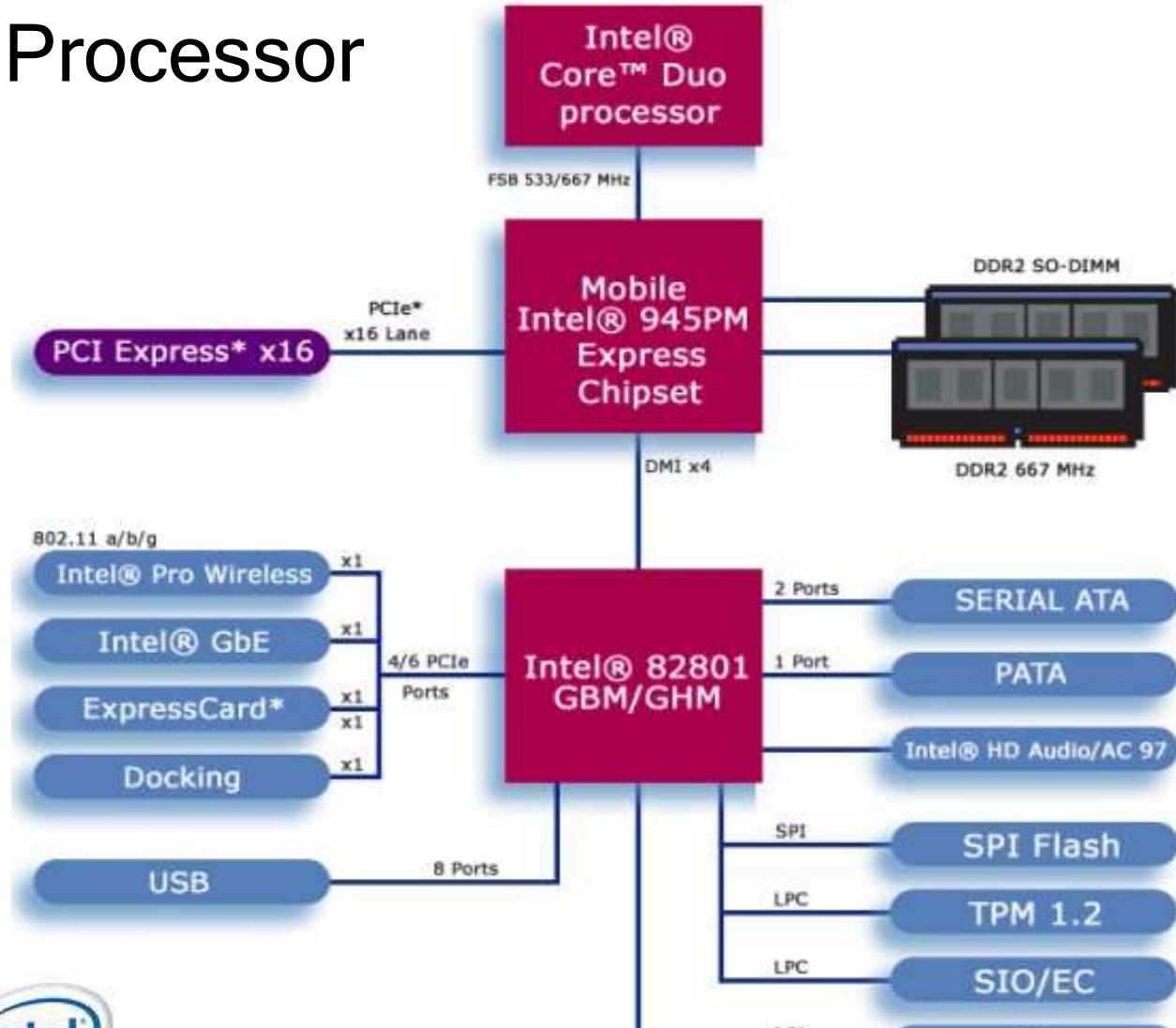

# Intel Centrino Processor

## PCI Express\* x16 Interface:

Supports the latest high-performance graphics cards.

## Intel High Definition (HD) Audio:

Integrated audio support enables premium sound and delivers advanced features such as multiple audio streams.

- ✓ 5X better wireless performance

- ✓ Longer Battery Life

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Intel Atom Processor

- ✓ Old Pentium architecture with modification (Low power addition) : 10Watt

- ✓ Inside processor chip

- Graphics processor, Memory controller

- Wireless controller (Centrino Atom)

# Thank You!!

## We Are Looking For Questions.

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Review of Computer Architecture

A Sahu

Dept. of Comp. Sc. & Engg.

IIT Guwahati

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Outline

- Computer organization Vs Architecture

- Processor architecture

- Pipeline architecture

- Data, resource and branch hazards

- Superscalar & VLIW architecture

- Memory hierarchy

- Reference

# Computer organization Vs Architecture

Comp Organization => Digital Logic Module

Logic and Low level

---

Comp Architecture => ISA Design, MicroArch Design

Algorithm for

- Designing best micro architecture,

- Pipeline model,

- Branch prediction strategy, memory management

- Etc.....

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

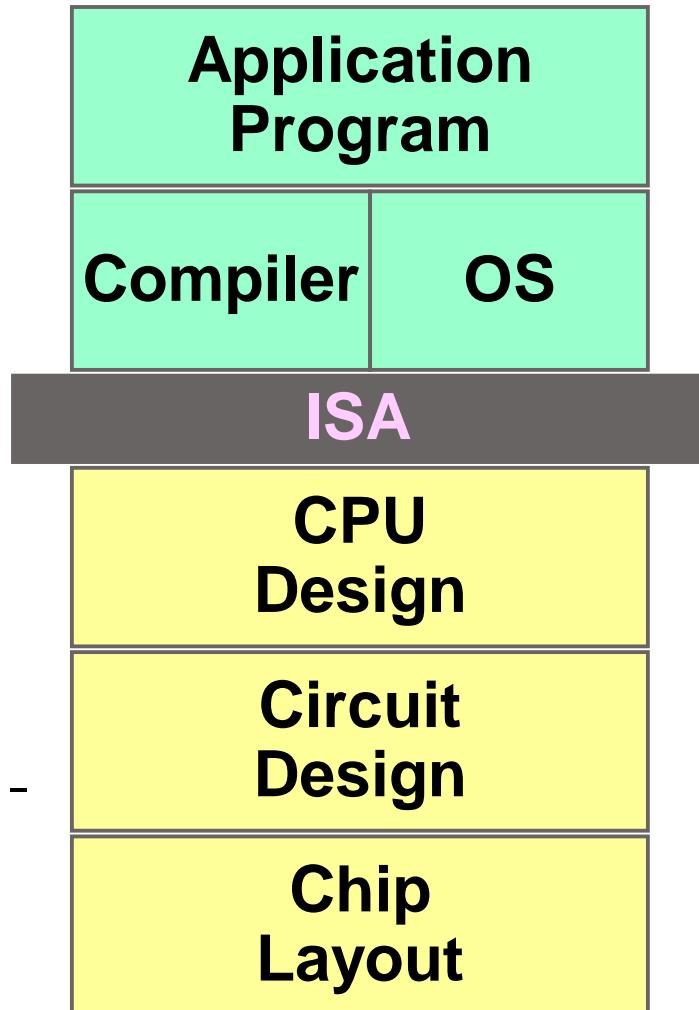

# Hardware abstraction

# Hardware/software interface

software

C++

m/c instr

reg, adder

transistors

hardware

} Arch. focus

- Instruction set architecture

- Lowest level visible to a programmer

- Micro architecture

- Fills the gap between instructions and logic modules

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Instruction Set Architecture

- Assembly Language View

- Processor state (RF, mem)

- Instruction set and encoding

- Layer of Abstraction

- Above: how to program machine - HLL, OS

- Below: what needs to be built - tricks to make it run fast

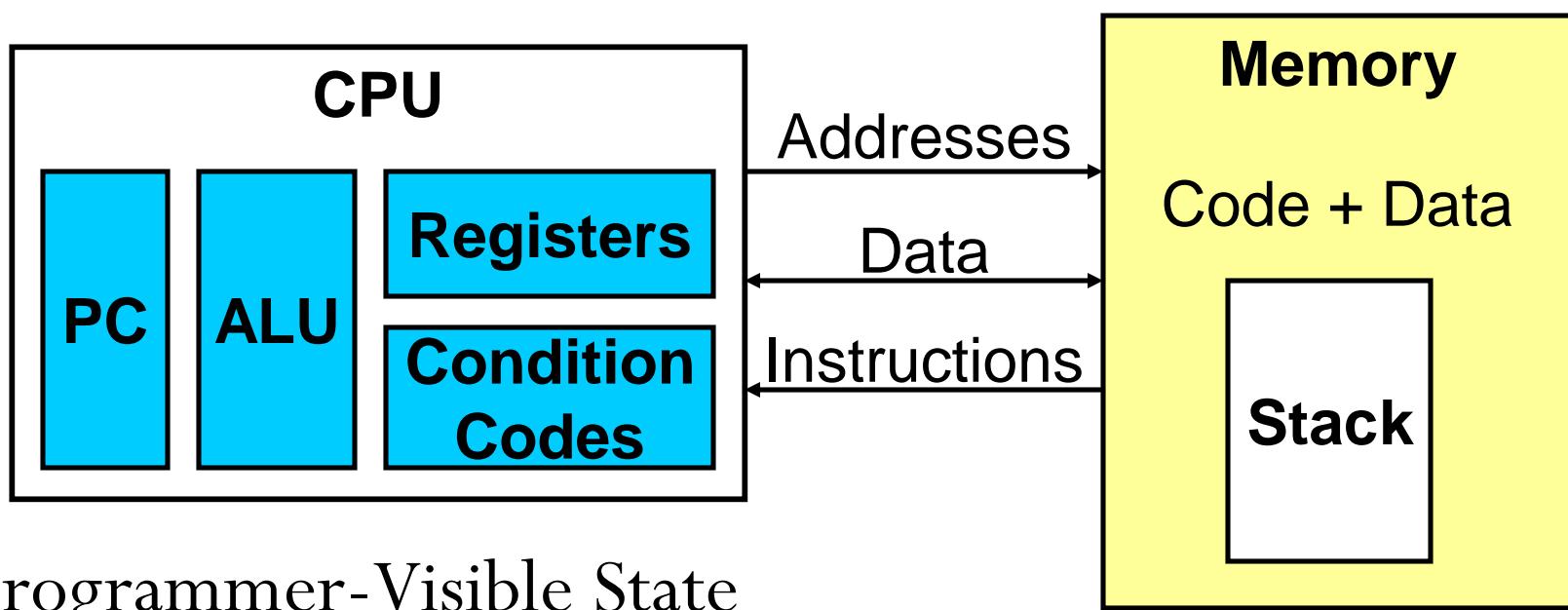

# The Abstract Machine

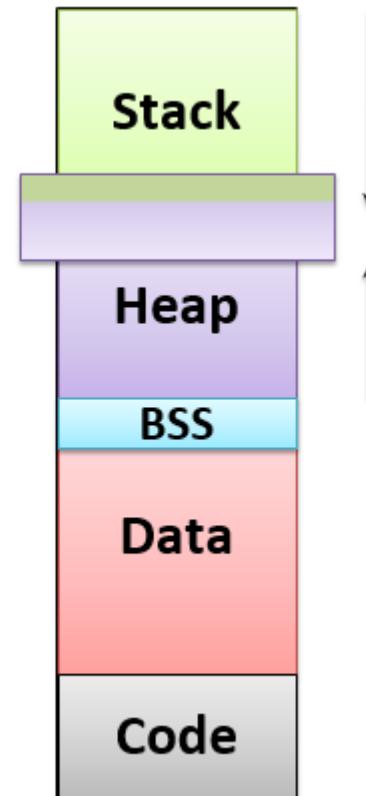

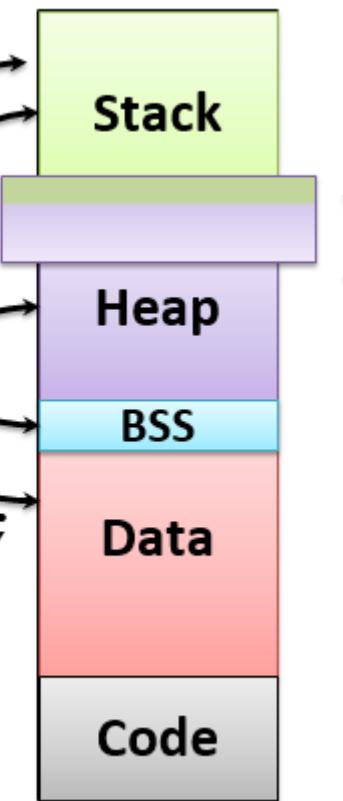

- Programmer-Visible State

- PC Program Counter

- Register File

- heavily used data

- Condition Codes

- **Memory**

- Byte array

- Code + data

- stack

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Instructions

- Language of Machine

- Easily interpreted

- primitive compared to HLLs

- Instruction set design goals

- maximize performance,

- minimize cost,

- reduce design time

# Instructions

- All MIPS Instructions: 32 bit long, have 3 operands

- Operand order is fixed (destination first)

Example:

C code:

$A = B + C$

MIPS code:

add \$s0, \$s1, \$s2

(associated with variables by compiler)

- Registers numbers 0 .. 31, e.g.,

$\$t0=8, \$t1=9, \$s0=16, \$s1=17$  etc.

- 000000 10001 10010 01000 00000 100000

| op | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

|----|----|----|----|-------|-------|

AVAILABLE AT:

# Instructions LD/ST & Control

- Load and store instructions

- Example:

*C code:*  $A[8] = h + A[8];$

*MIPS code:* lw \$t0, 32(\$s3)

add \$t0, \$s2, \$t0

sw \$t0, 32(\$s3)

- Example: lw \$t0, 32(\$s2)

|    |    |    |               |

|----|----|----|---------------|

| 35 | 18 | 9  | 32            |

| op | rs | rt | 16 bit number |

- Example:

if (i != j) beq \$s4, \$s5, Lab1

h = i + j; add \$s3, \$s4, \$s5

else j Lab2

h = i - j; Lab1: sub \$s3, \$s4, \$s5

Lab2:

...

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# What constitutes ISA?

- **Set of basic/primitive operations**

- Arithmetic, Logical, Relational, Branch/jump, Data movement

- **Storage structure – registers/memory**

- Register-less machine, ACC based machine, A few special purpose registers, Several Gen purpose registers, Large number of registers

- **How addresses are specified**

- Direct, Indirect, Base vs. Index, Auto incr and auto decr, Pre (post) incr/decr, Stack

- **How operand are specified**

- 3 address machine  $r1 = r2 + r3$ , 2 address machine  $r1 = r1 + r2$

- 1 address machine  $Acc = Acc + x$  (Acc is implicit)

- 0 address machine add values on (top of stack)

- **How instructions are encoded**

# RISC vs. CISC

- **RISC**

- Uniformity of instructions,

- Simple set of operations and addressing modes,

- Register based architecture with 3 address instructions

- **RISC: Virtually all new ISA since 1982**

- ARM, MIPS, SPARC, HP's PA-RISC, PowerPC, Alpha, CDC 6600

- **CISC** : Minimize code size, make assembly language easy

- VAX: instructions from 1 to 54 bytes long!*

- Motorola 680x0, Intel 80x86

# MIPS subset for implementation

- Arithmetic - logic instructions

- add, sub, and, or, slt

- Memory reference instructions

- lw, sw

- Control flow instructions

- beq, j

Incremental changes in the design to include other instructions will be discussed later

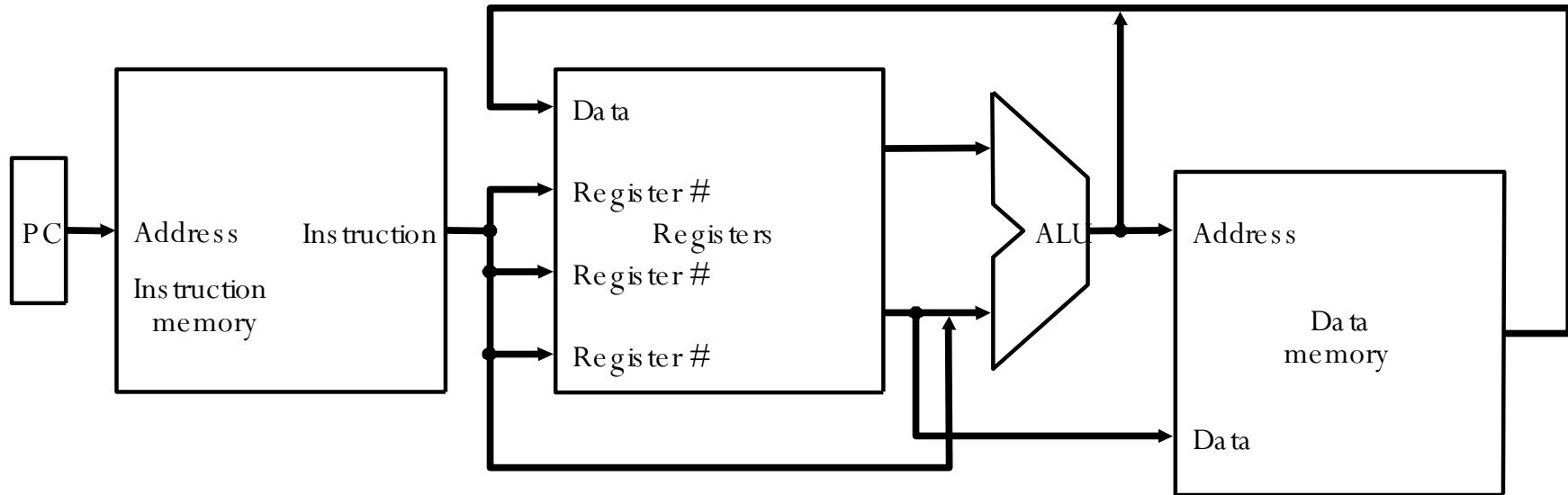

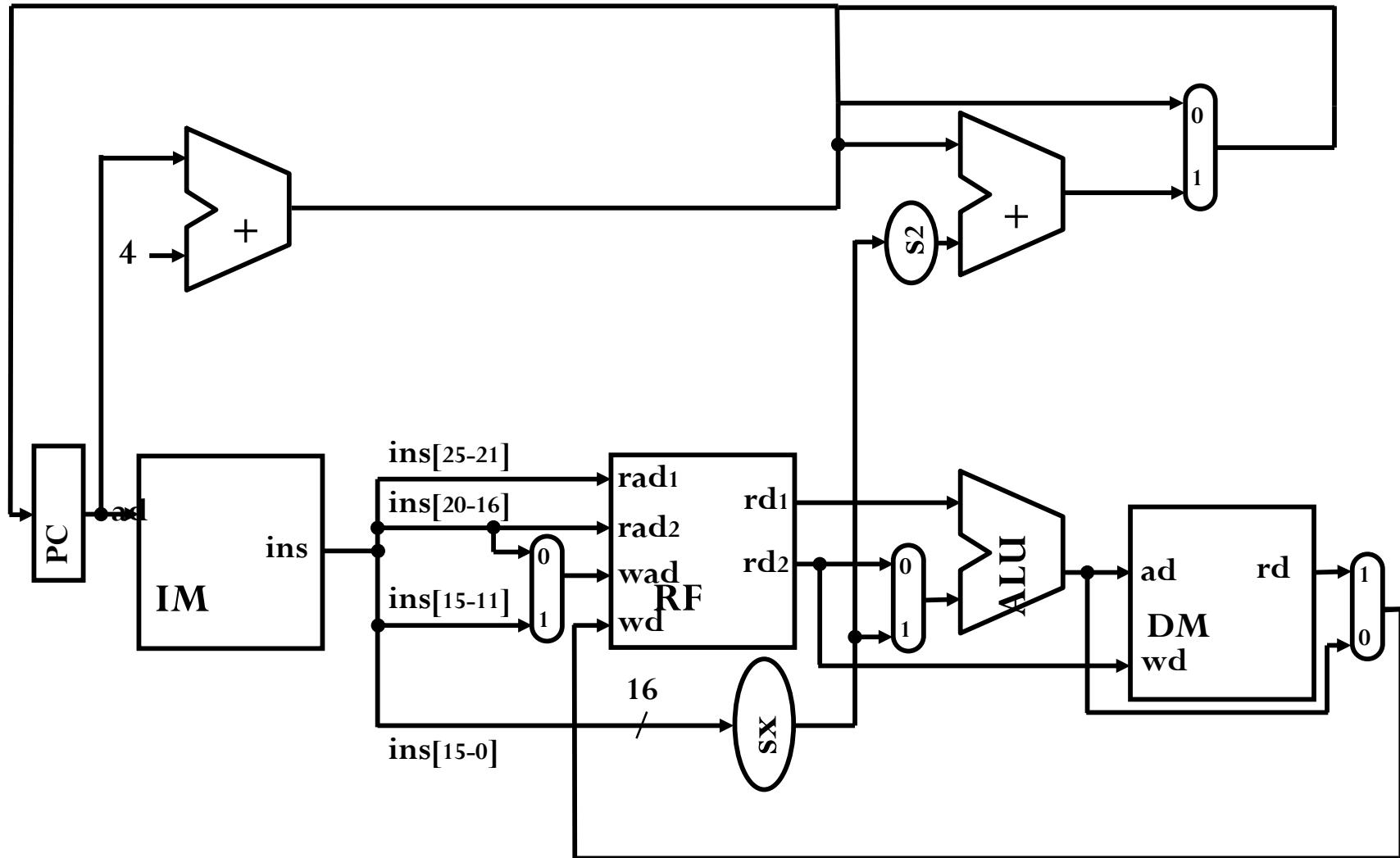

# Design overview

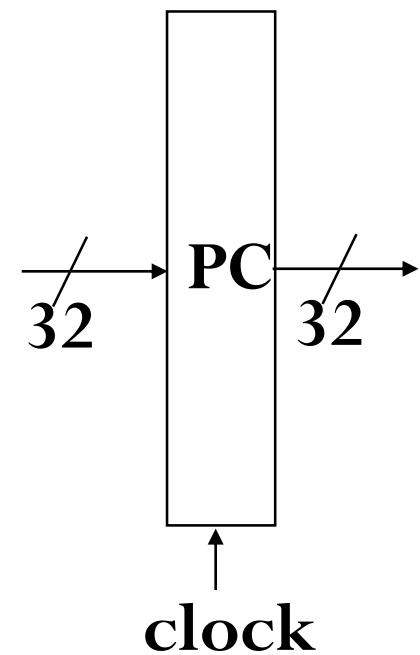

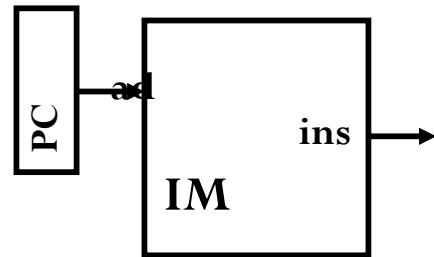

- Use the program counter (PC) to supply instruction address

- Get the instruction from memory

- Read registers

- Use the instruction to decide exactly what to do

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

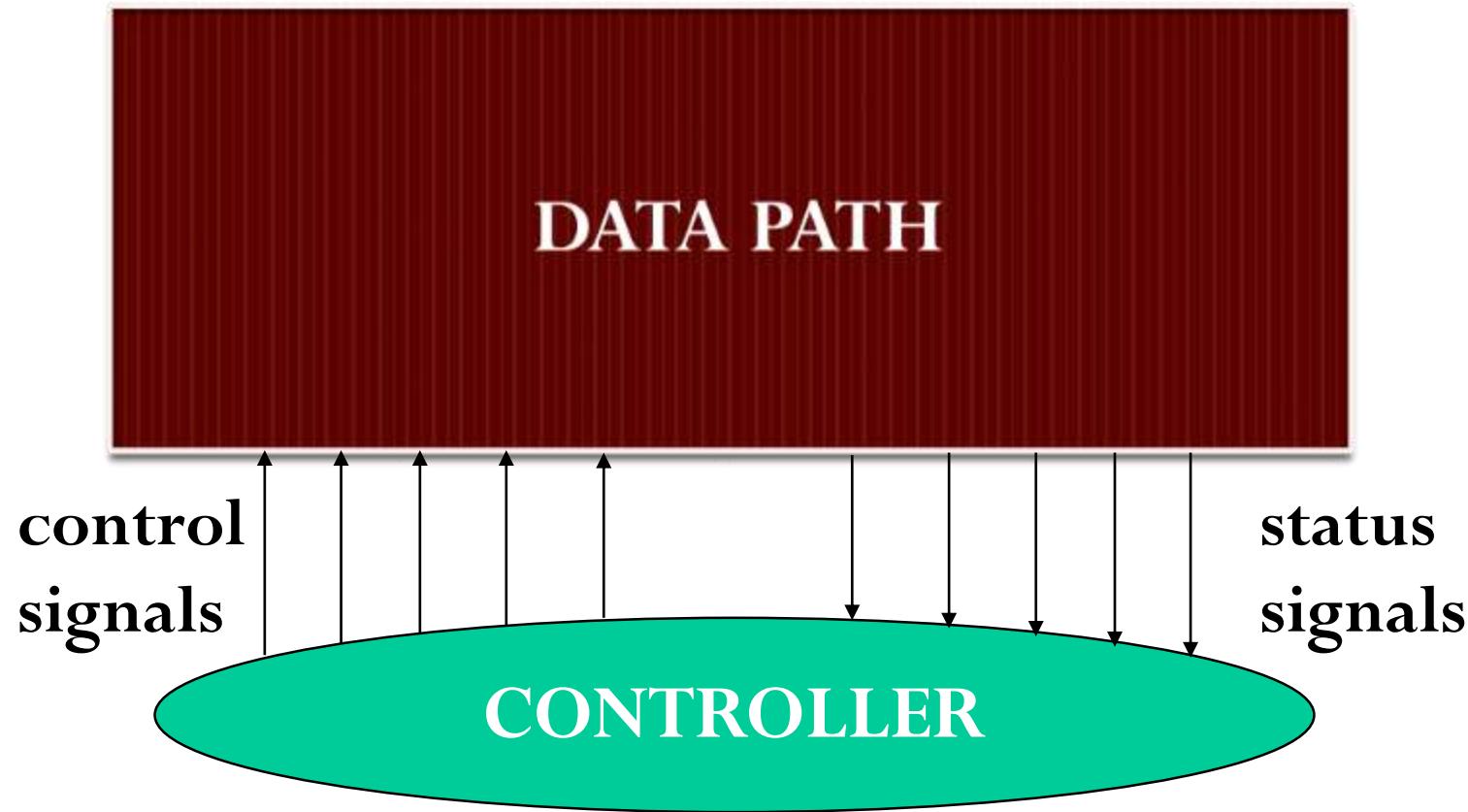

# Division into data path and control

# Building block types

Two types of functional units:

- elements that operate on data values (combinational)

- output is function of current input, no memory

- Examples

- gates: and, or, nand, nor, xor, inverter ,Multiplexer, decoder, adder, subtractor, comparator, ALU, array multipliers

- elements that contain state (sequential)

- output is function of current and previous inputs

- state = memory

- Examples:

- flip-flops, counters, registers, register files, memories

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Components for MIPS subset

- Register,

- Adder

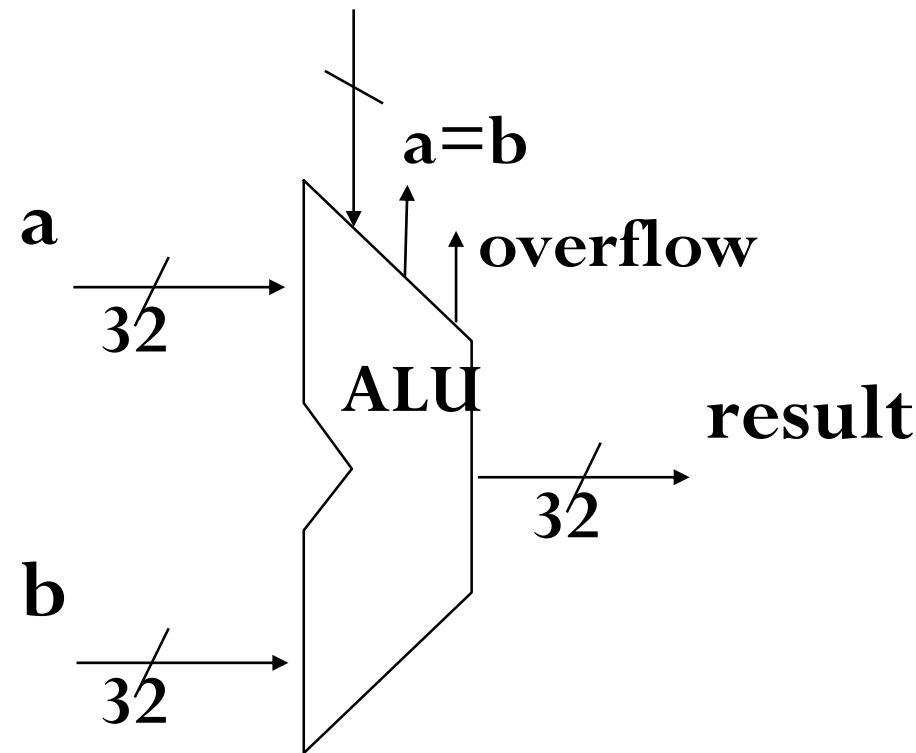

- ALU

- Multiplexer

- Register file

- Program memory

- Data memory

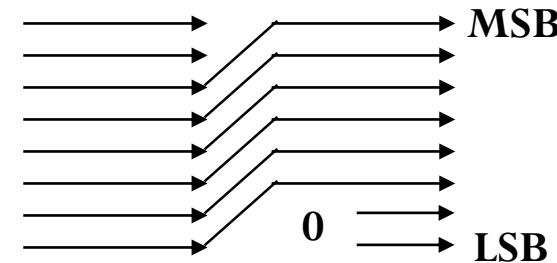

- Bit manipulation components

# Components - register

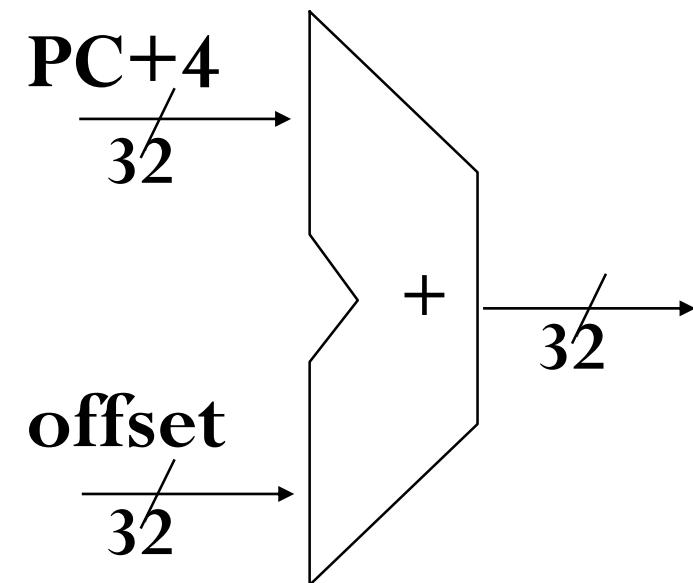

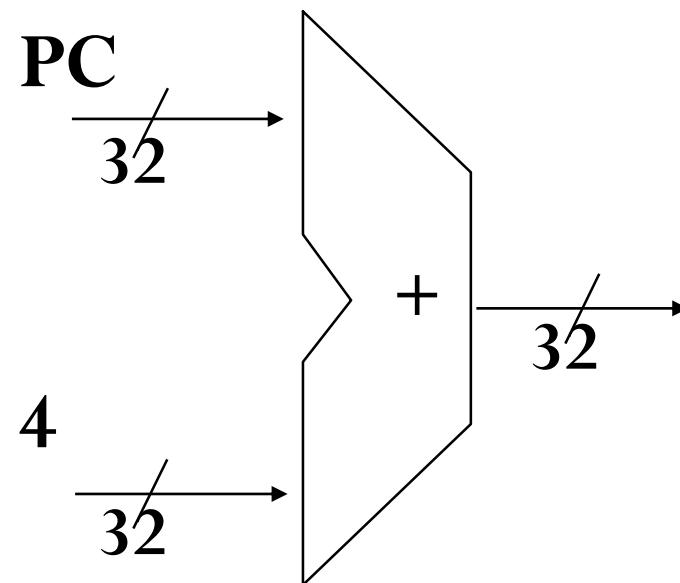

# Components - adder

# Components - ALU

## operation

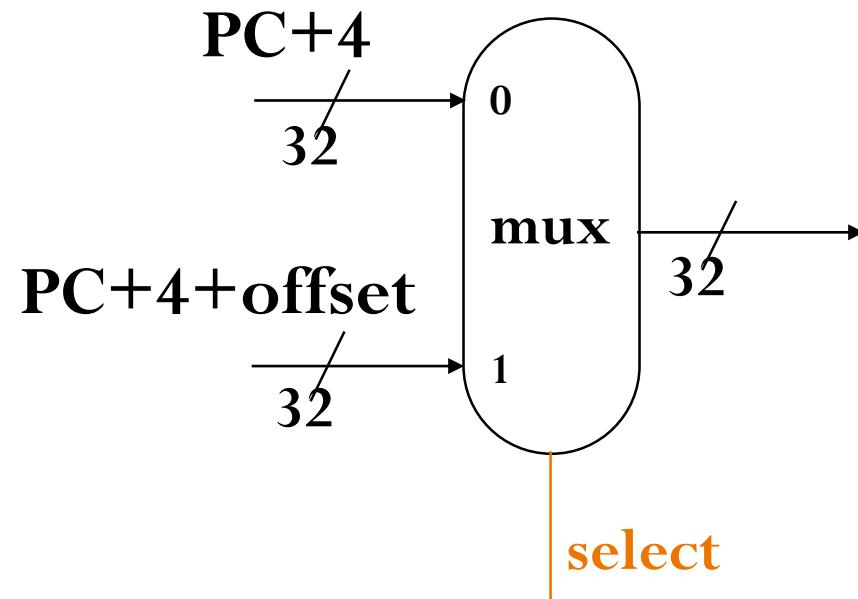

# Components - multiplexers

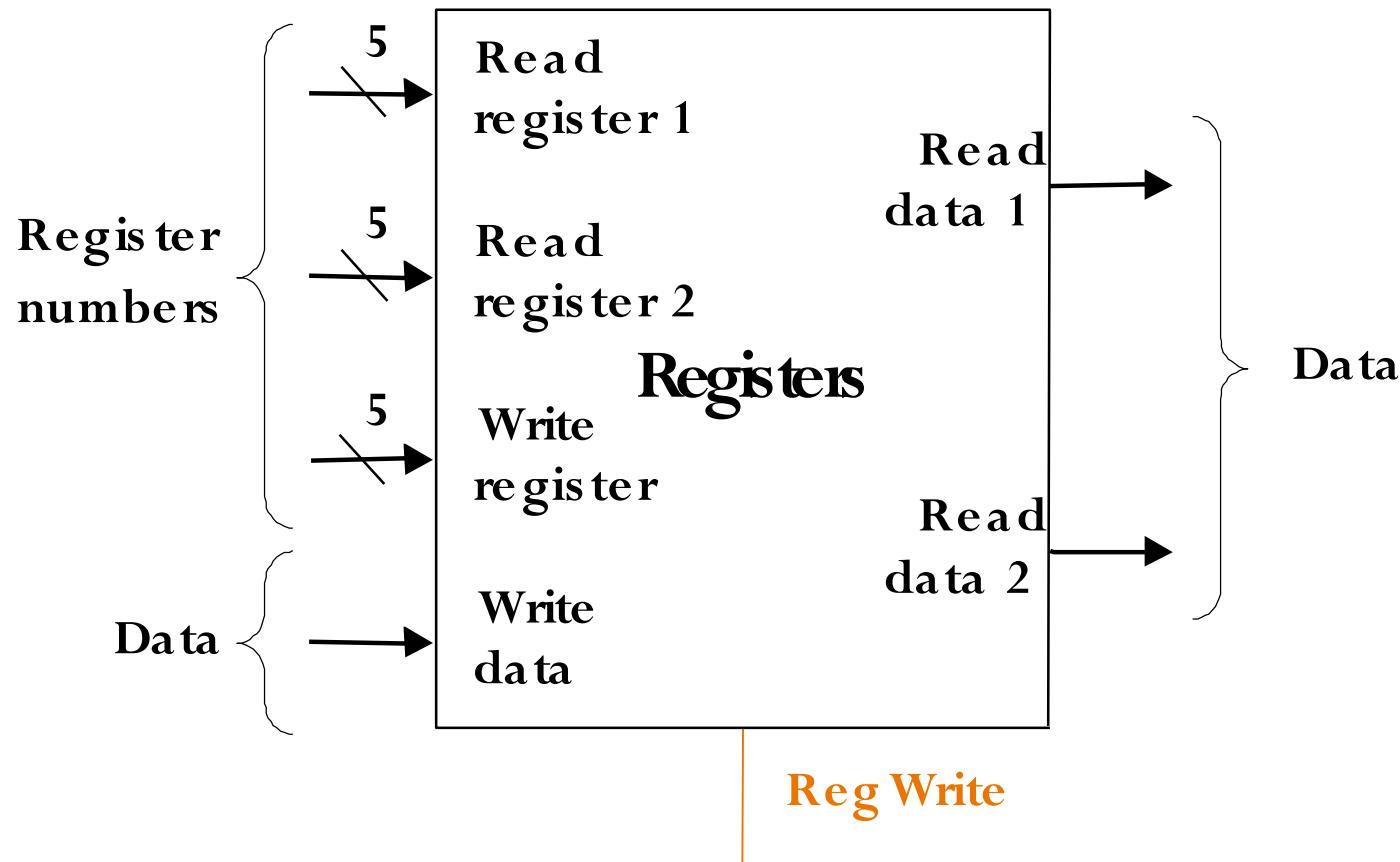

# Components - register file

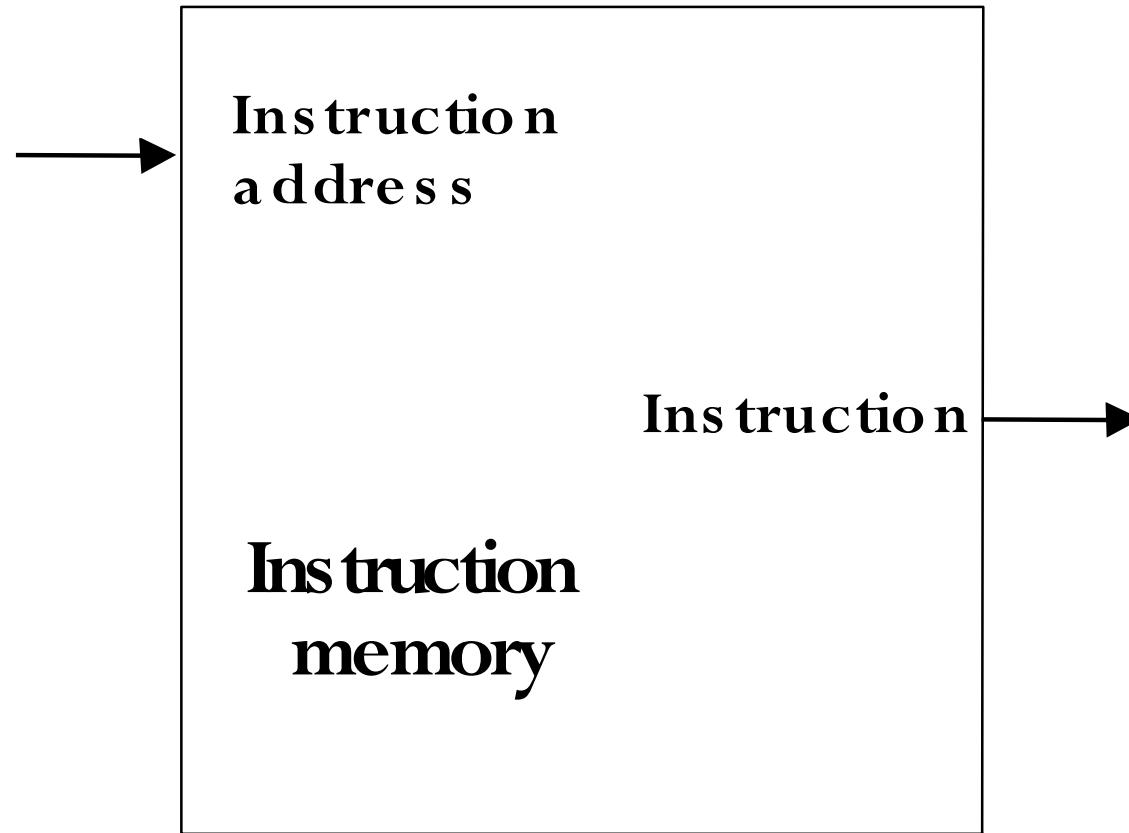

# Components - program memory

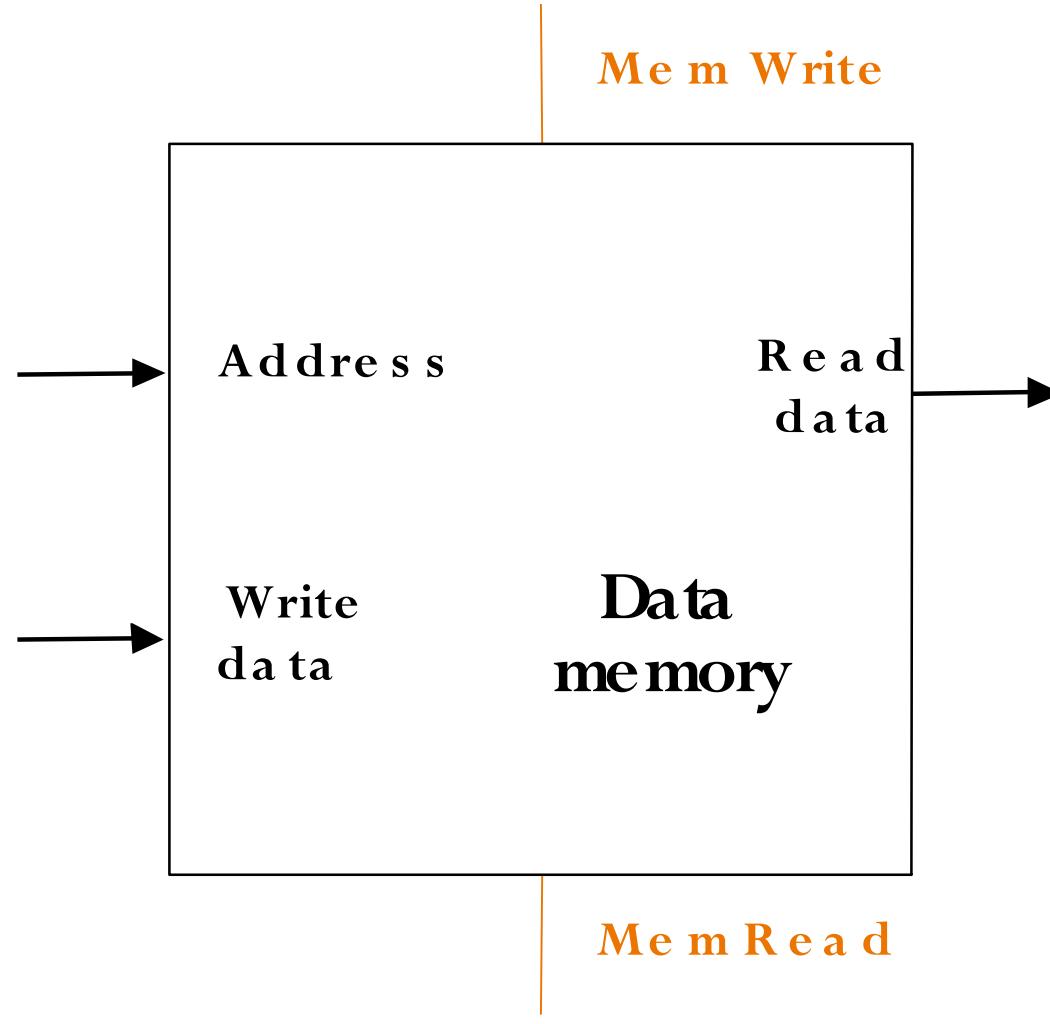

# MIPS components - data memory

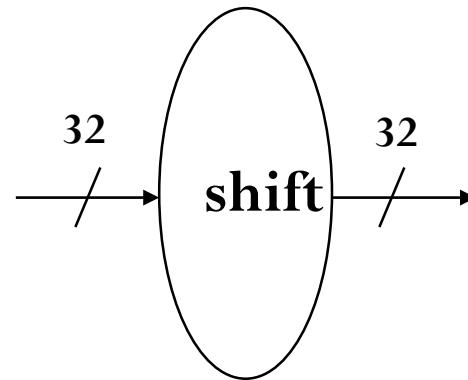

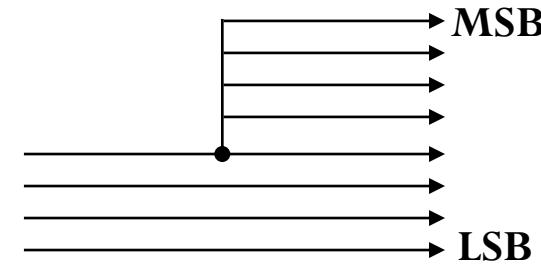

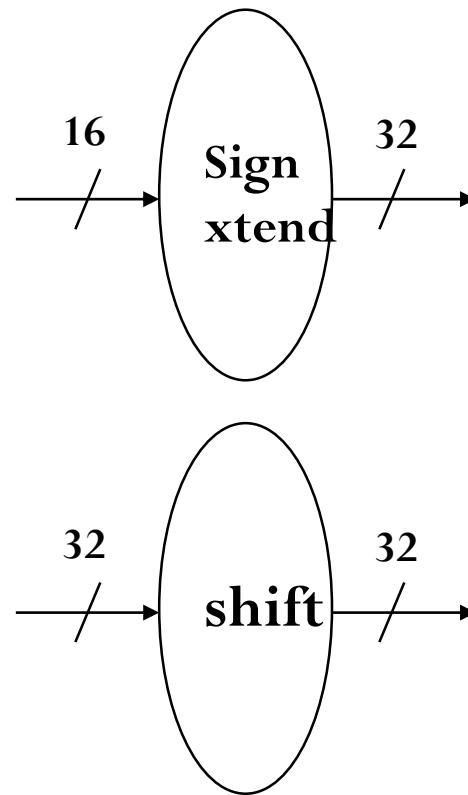

# Components - bit manipulation circuits

# MIPS subset for implementation

- Arithmetic - logic instructions

- add, sub, and, or, slt

- Memory reference instructions

- lw, sw

- Control flow instructions

- beq, j

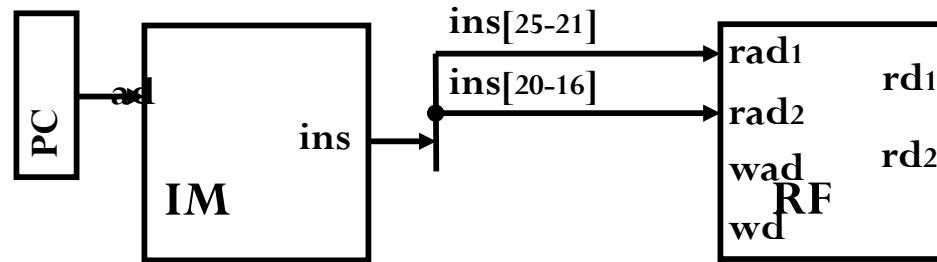

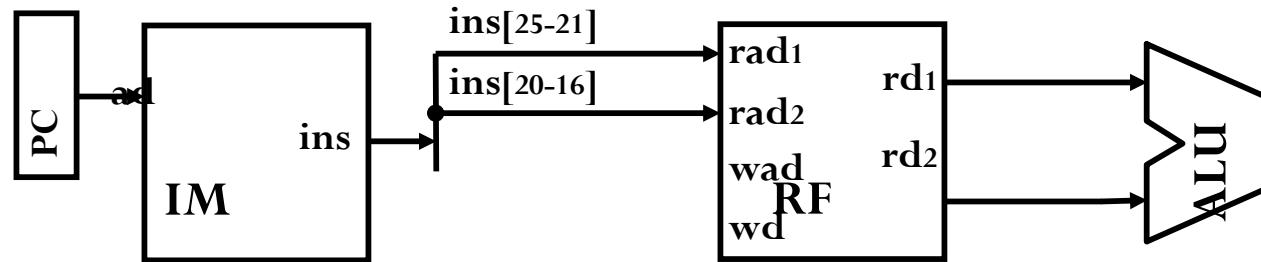

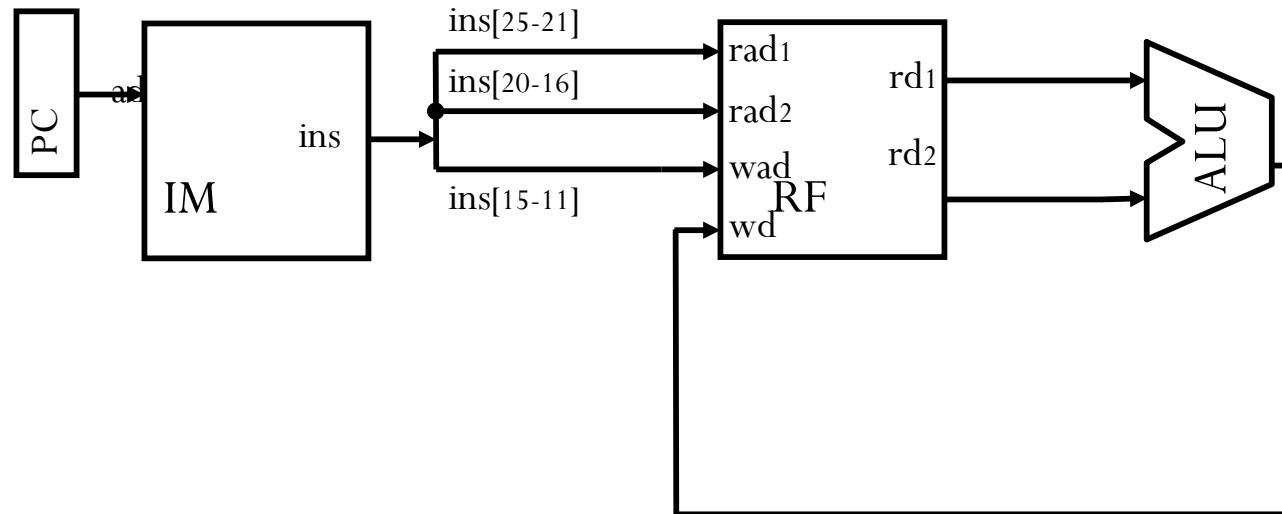

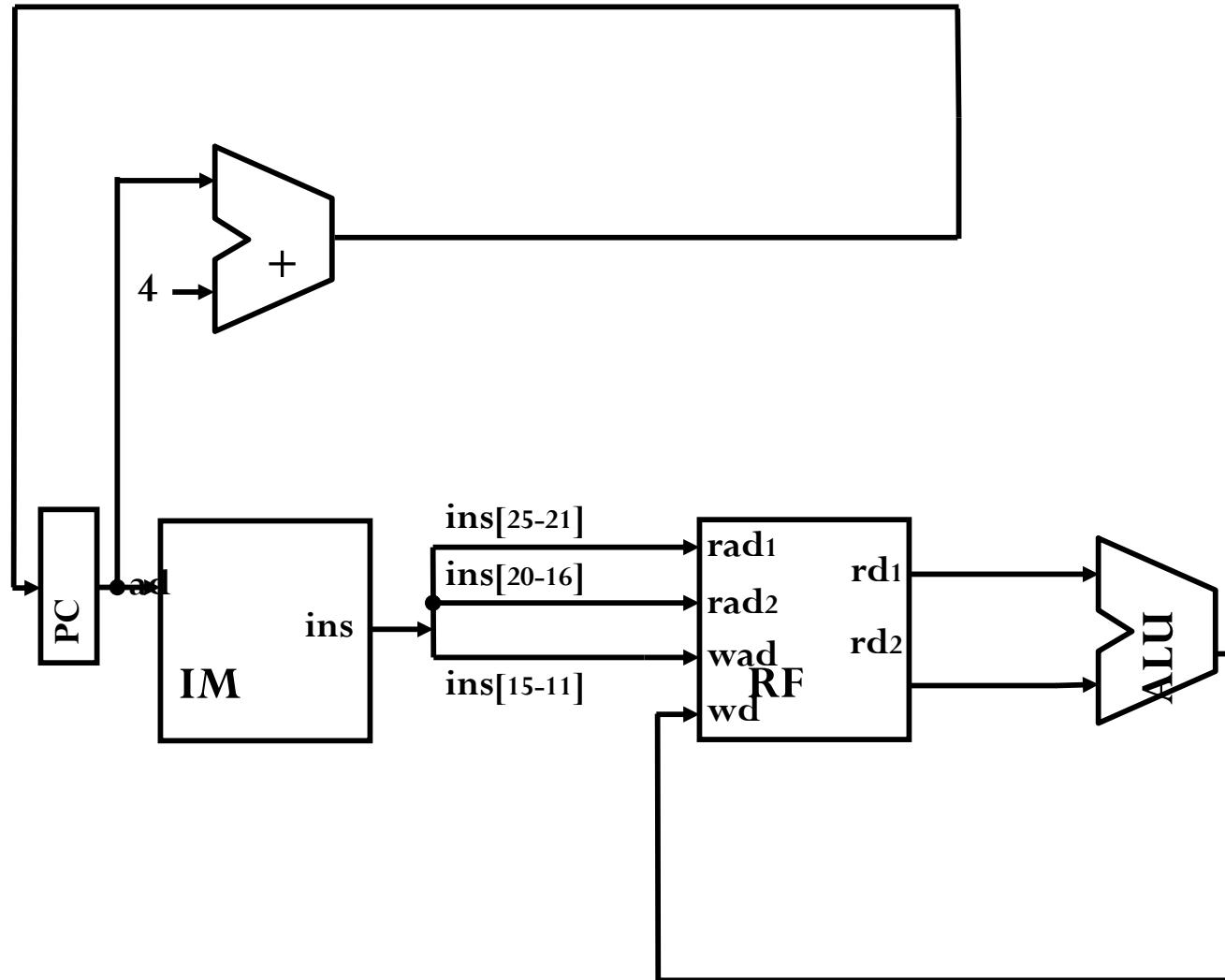

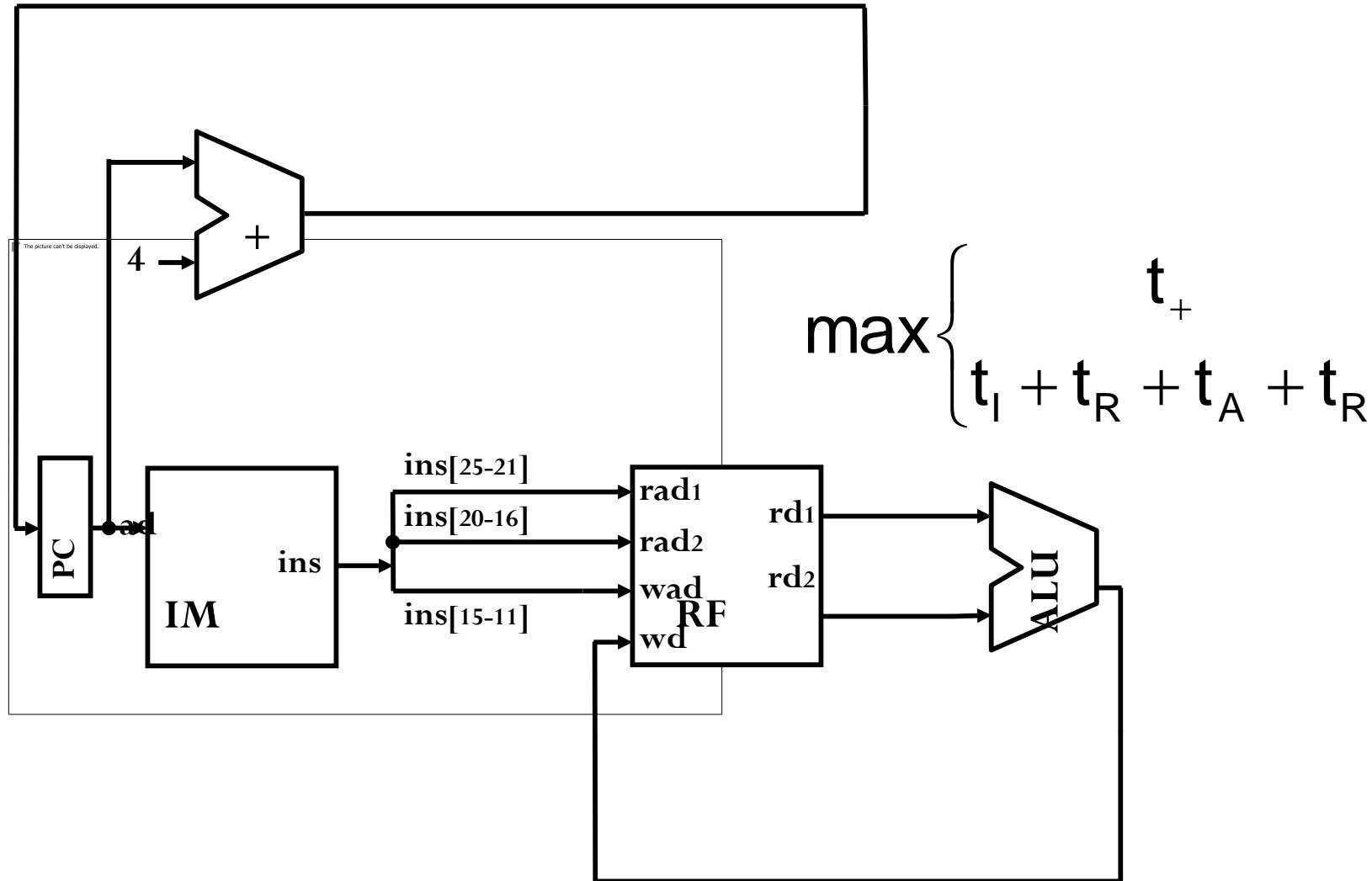

## Datapath for add, sub, and, or, slt

- Fetch instruction

- Address the register file

- Pass operands to ALU

- Pass result to register file

- Increment PC

actions required

Format: add \$t0, \$s1, \$s2

000000 10001 10010 01000 00000 100000

| op | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

|    |    |    |    |       |       |

AVAILABLE AT:

# Fetching instruction

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Addressing RF

# Passing operands to ALU

# Passing the result to RF

# Incrementing PC

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

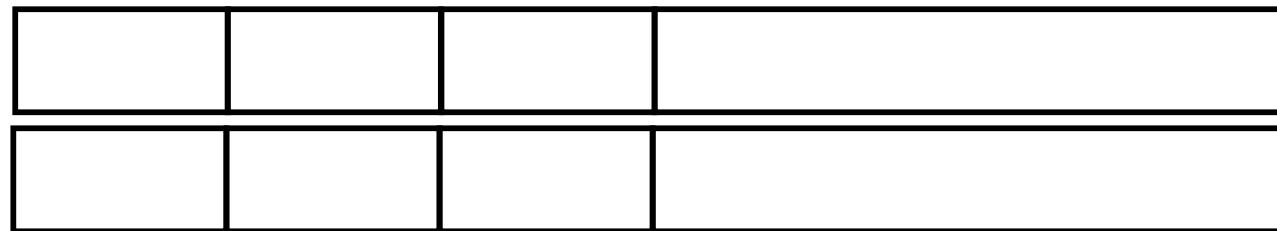

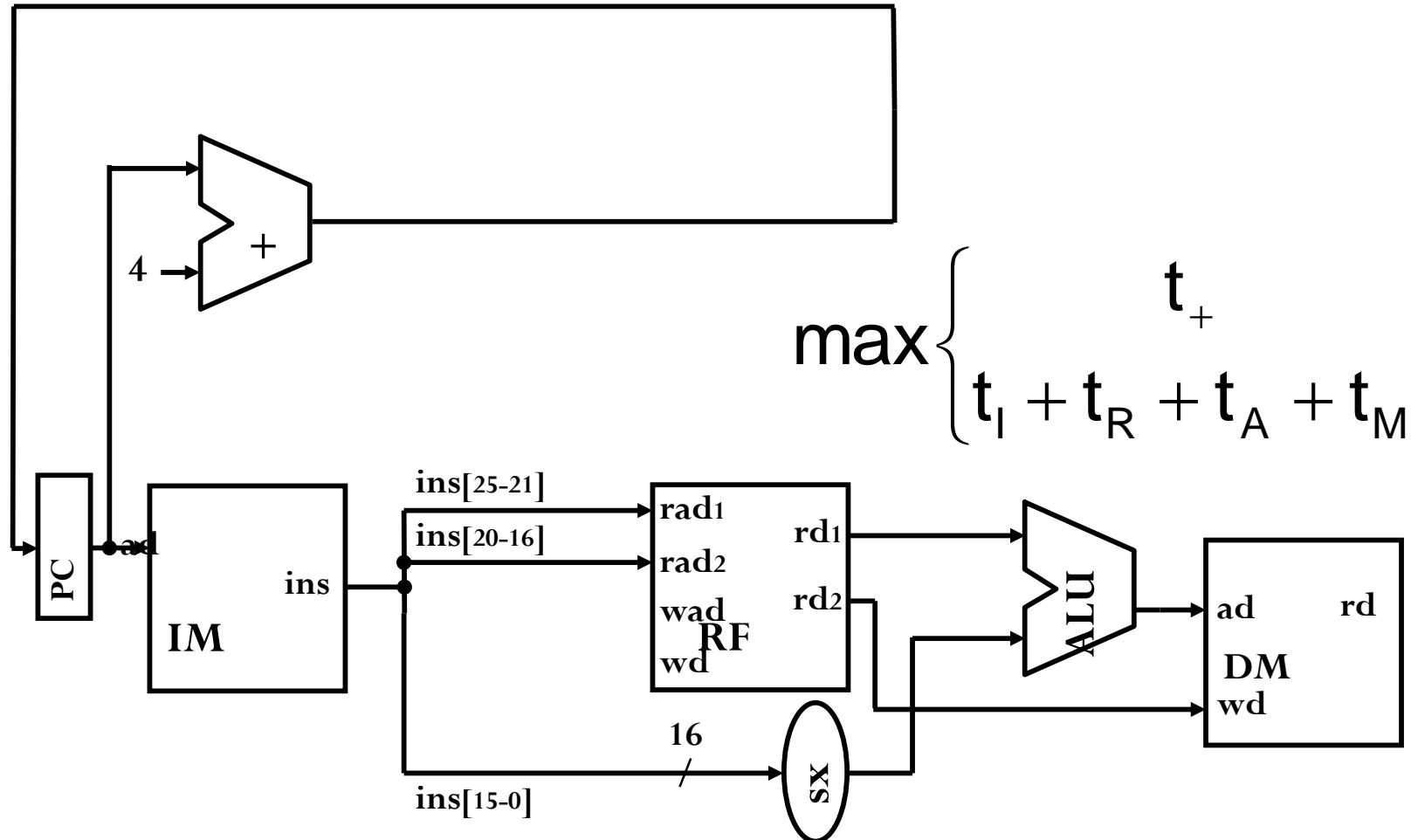

# Load and Store instructions

- format : I

- Example: lw \$t0, 32(\$s2)

35      18      9      32

op      rs      rt      16 bit number

# Adding “sw” instruction

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Adding “lw” instruction

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

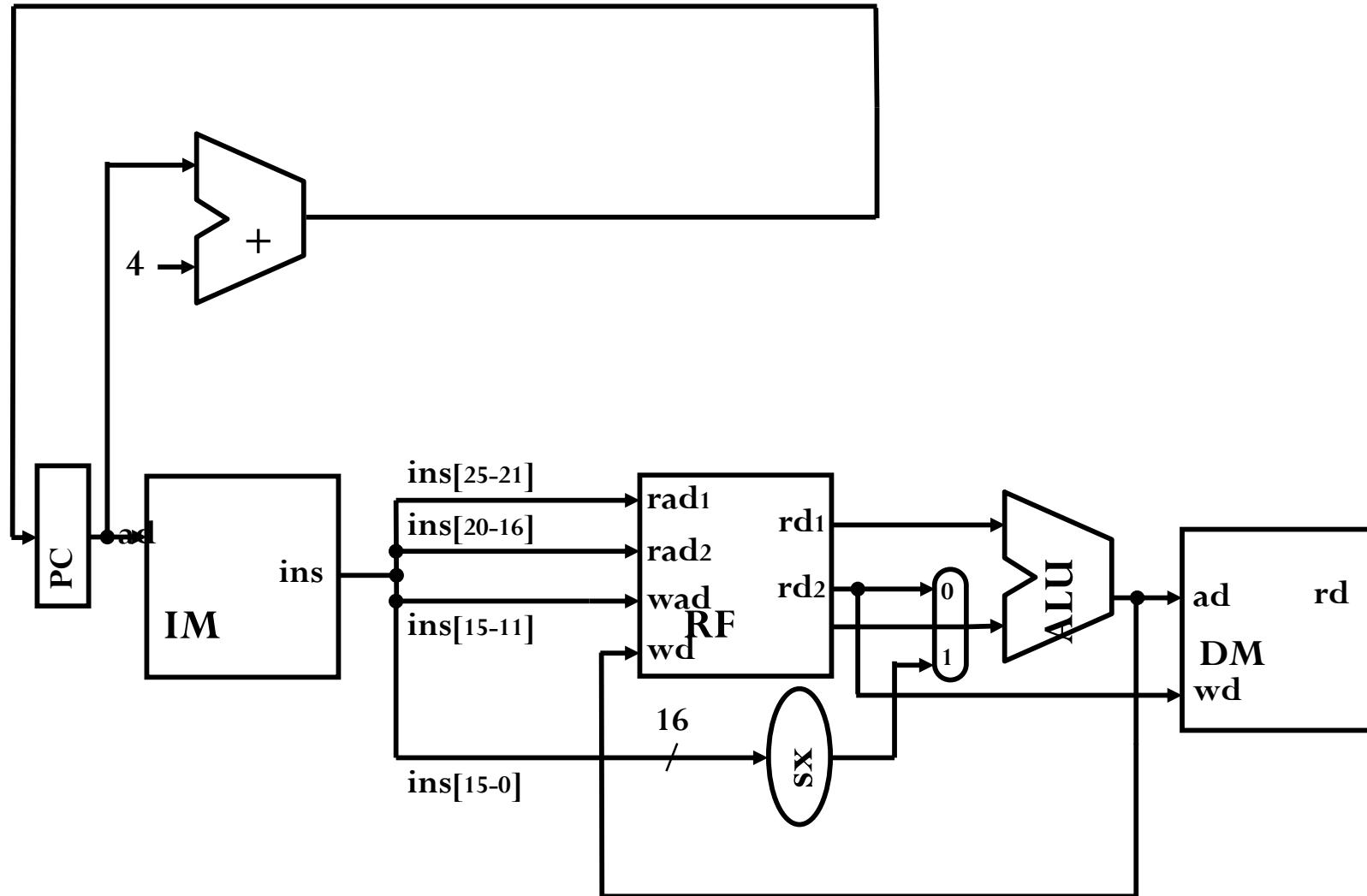

# Adding “beq” instruction

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

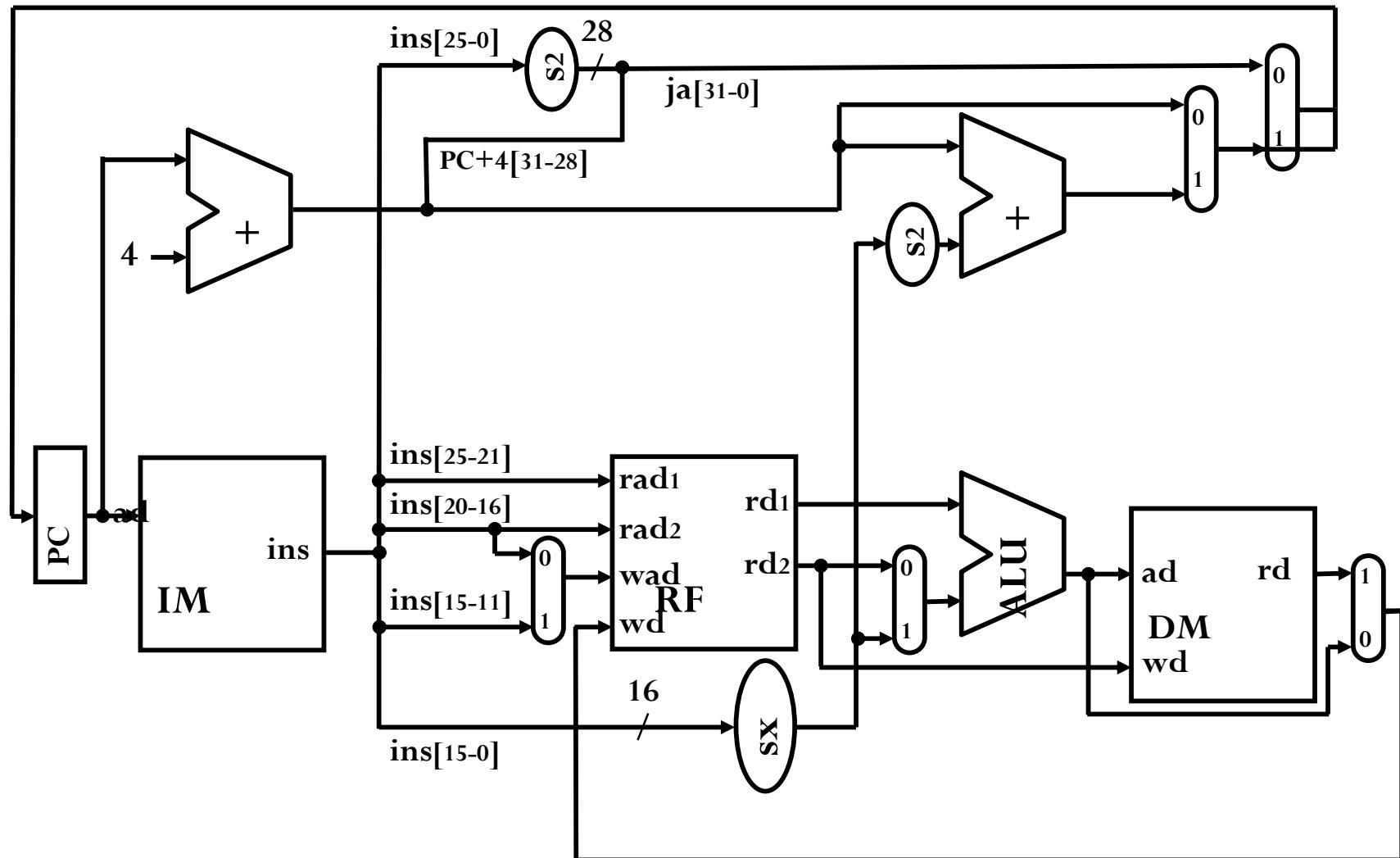

# Adding “j” instruction

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

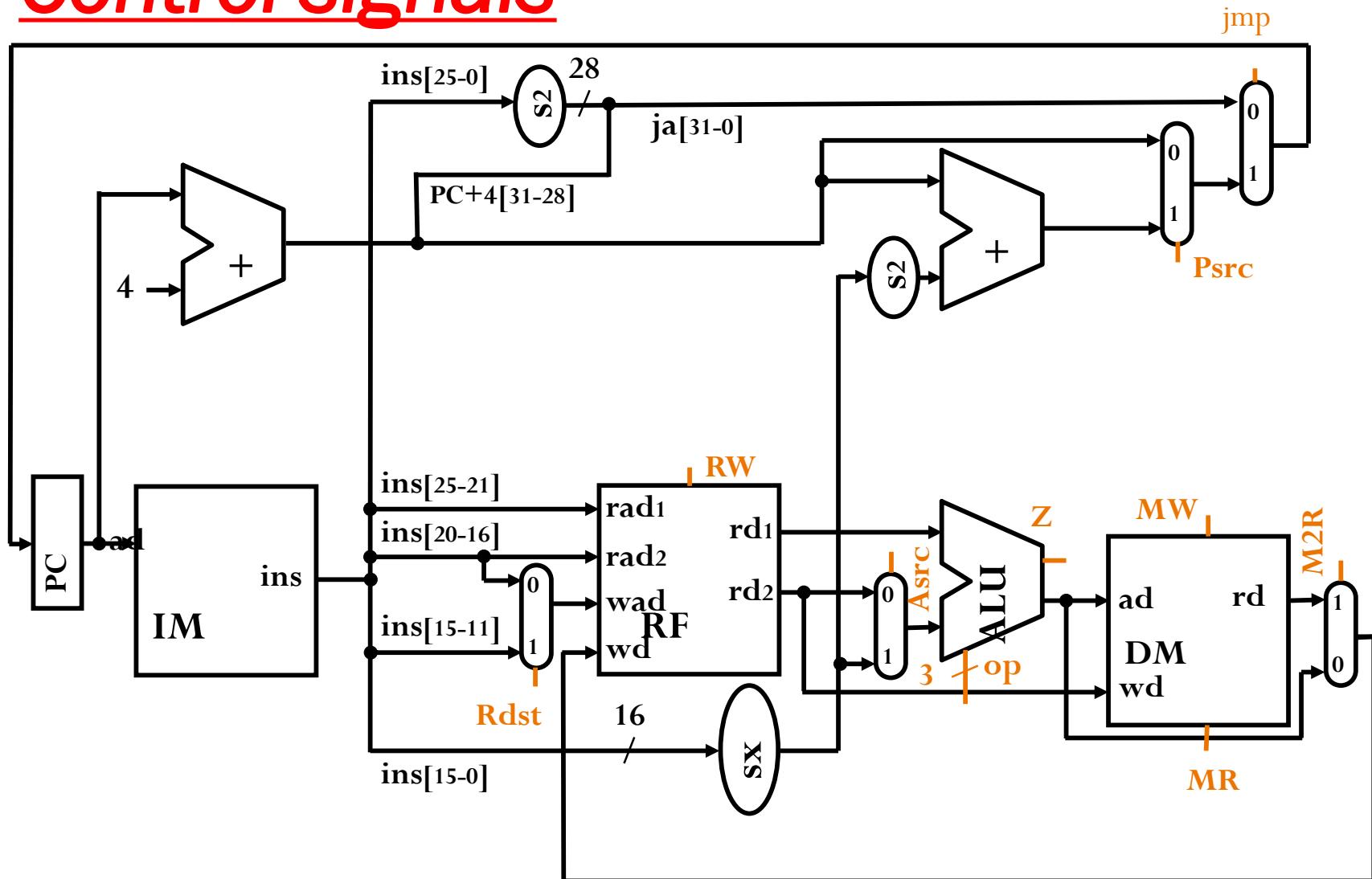

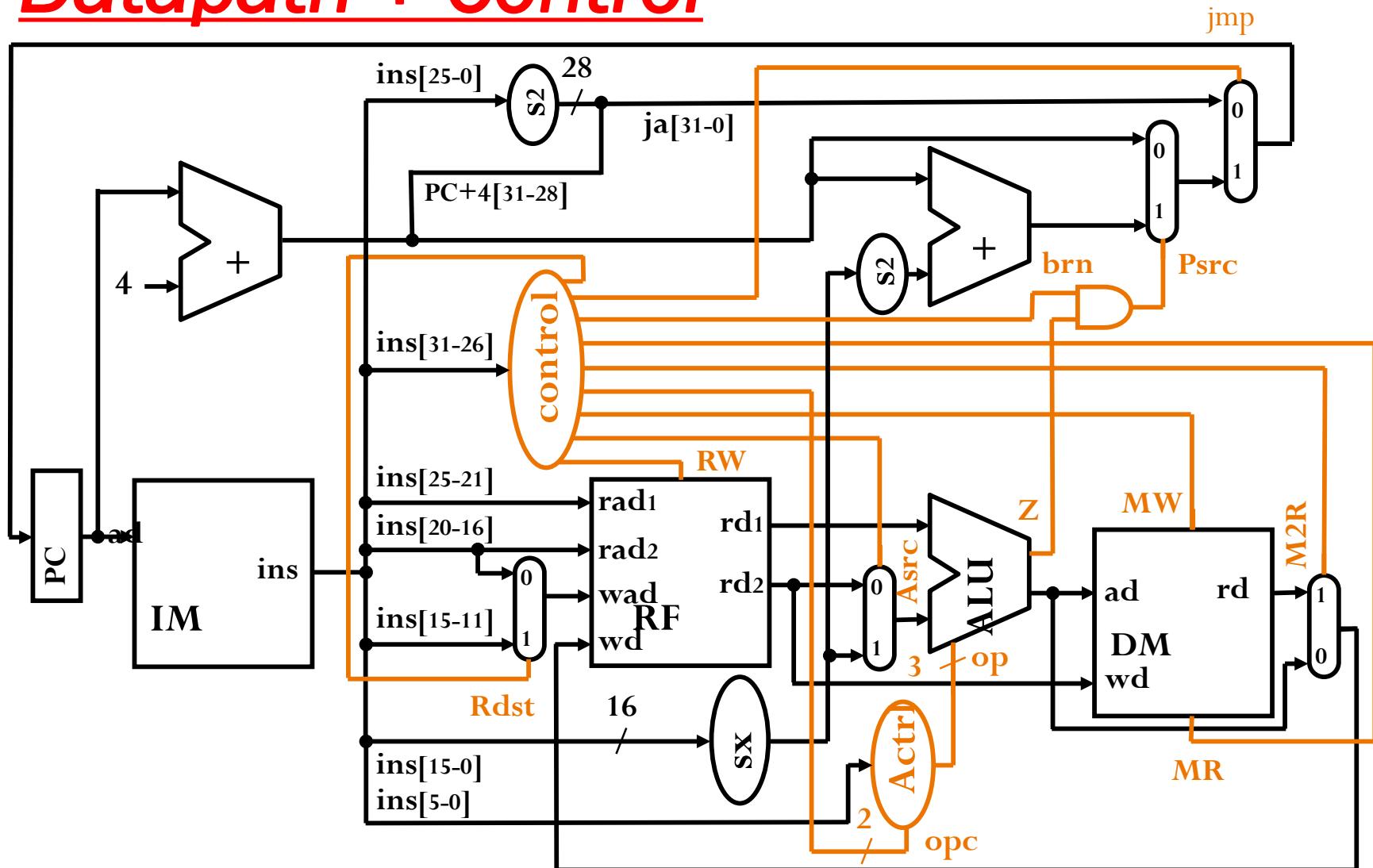

# Control signals

# Datapath + Control

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

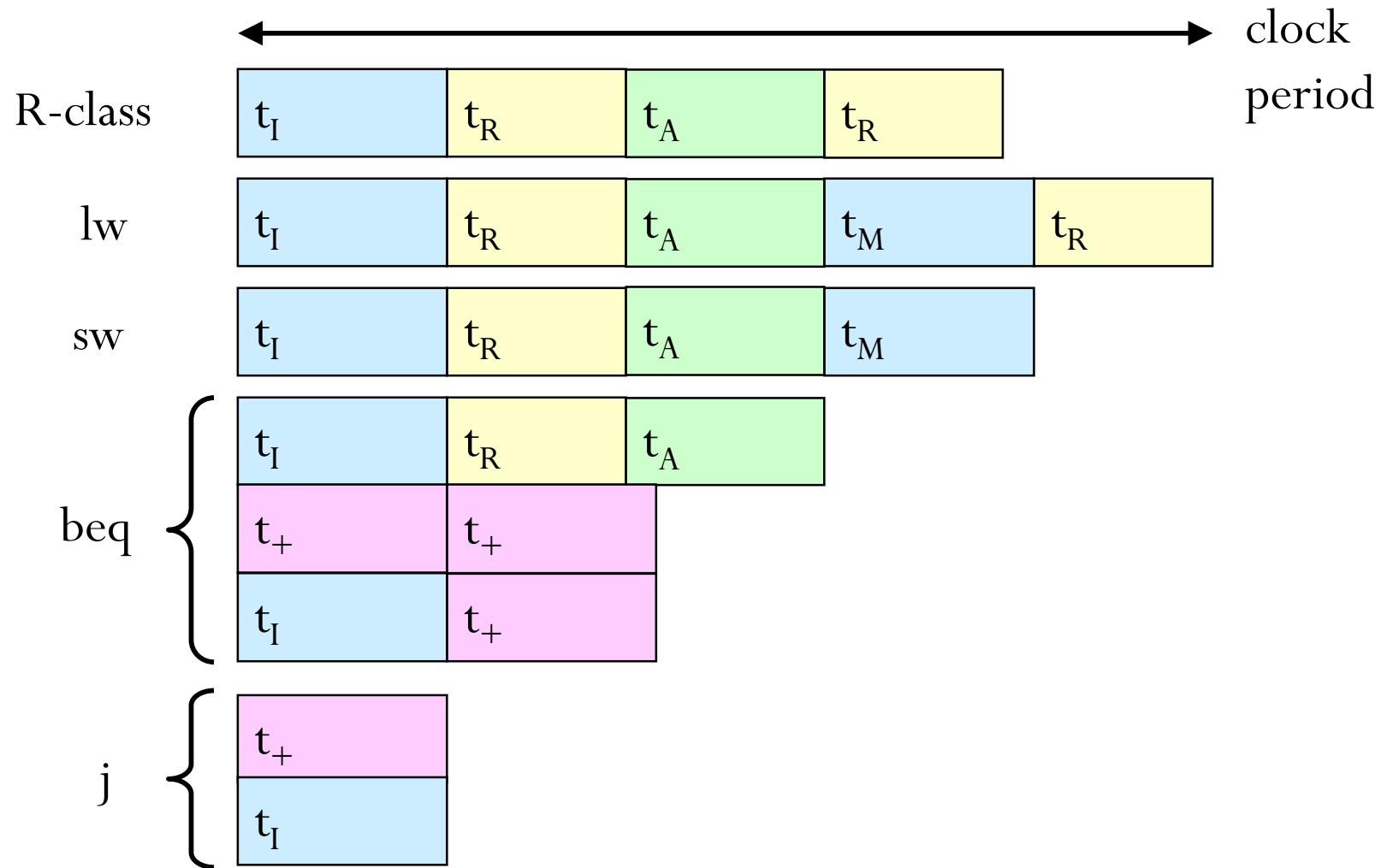

# Analyzing performance

## Component delays

- Register 0

- Adder  $t_+$

- ALU  $t_A$

- Multiplexer 0

- Register file  $t_R$

- Program memory  $t_I$

- Data memory  $t_M$

- Bit manipulation components 0

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Delay for {add, sub, and, or, slt}

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Delay for {sw}

# Clock period in single cycle design

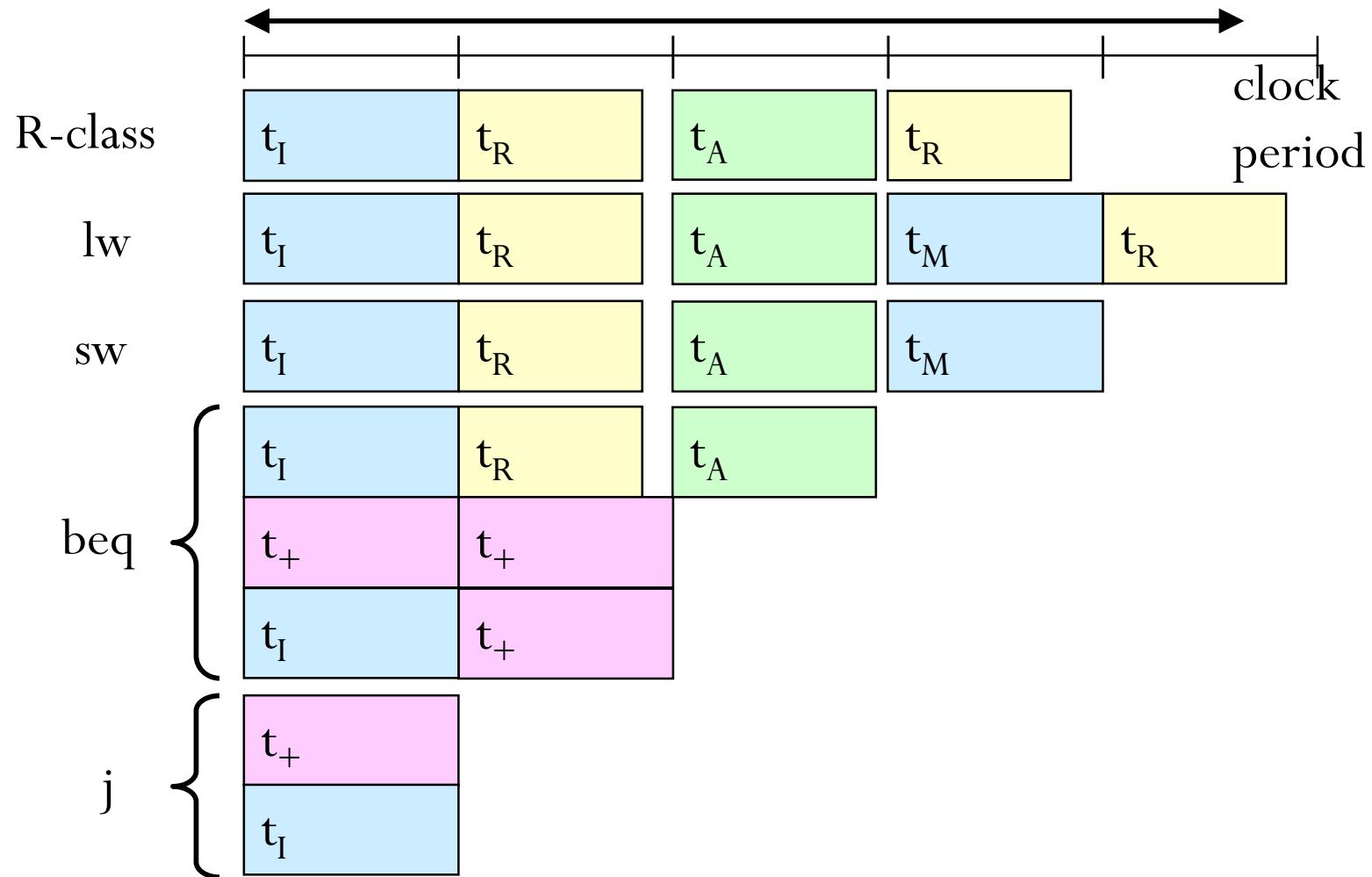

# Clock period in multi-cycle design

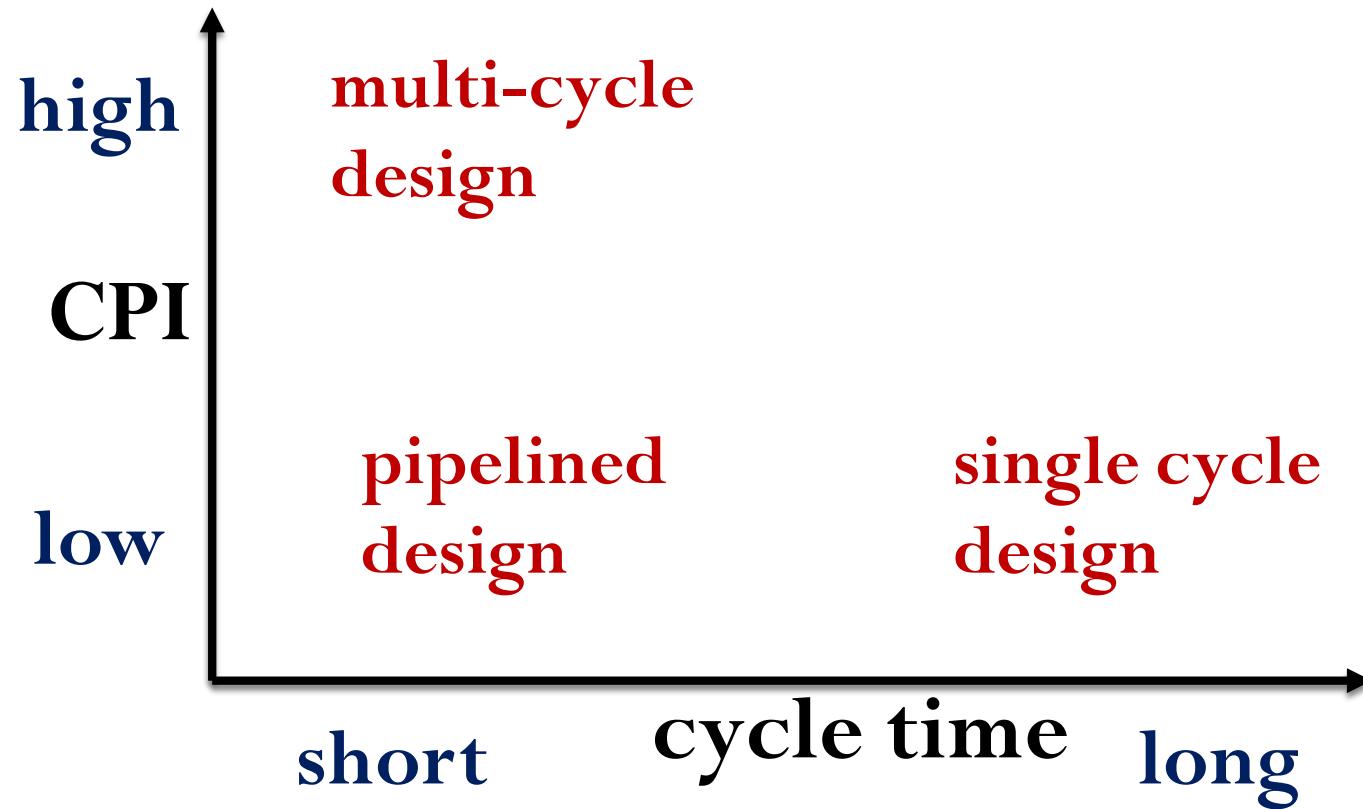

# Cycle time and CPI

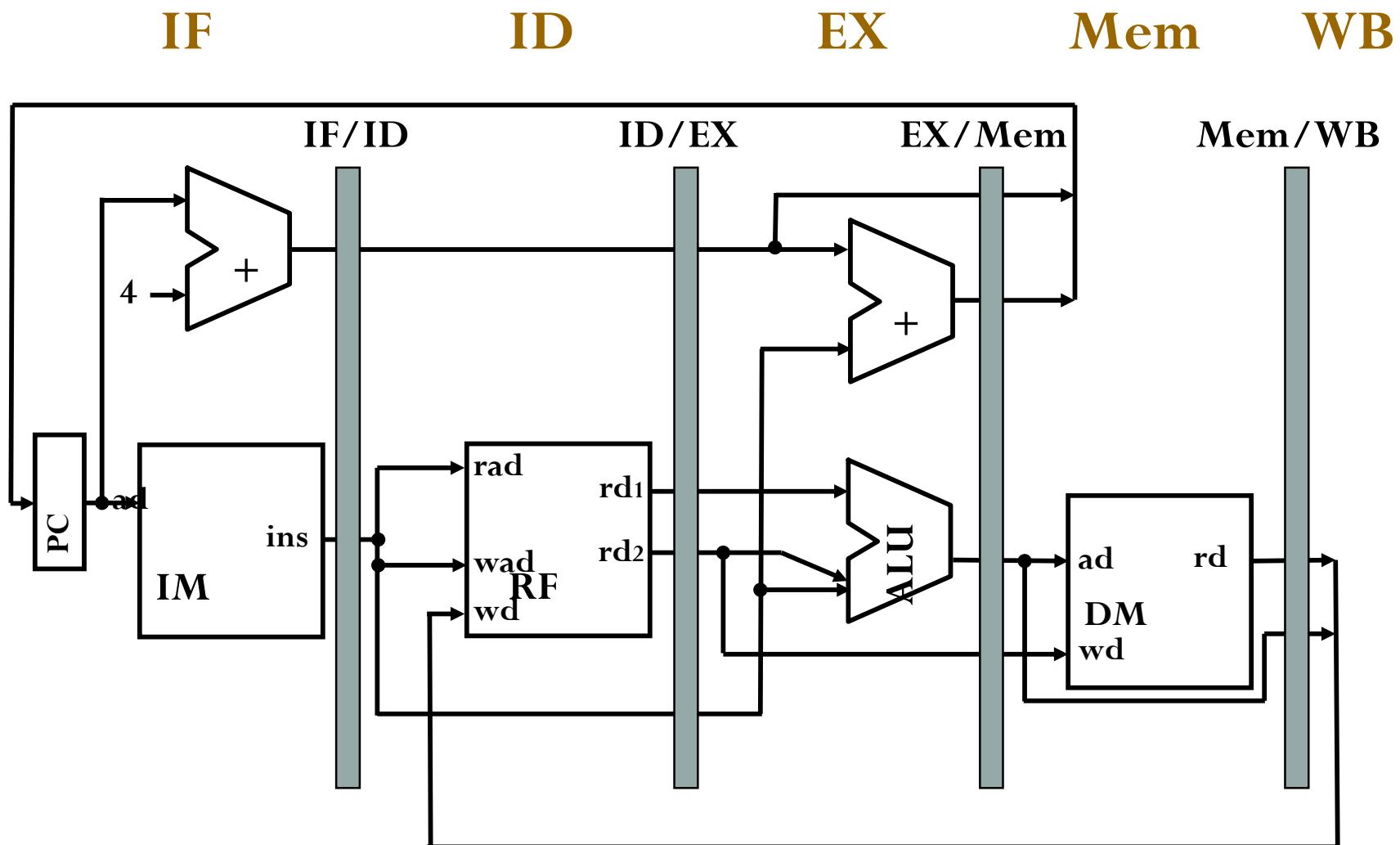

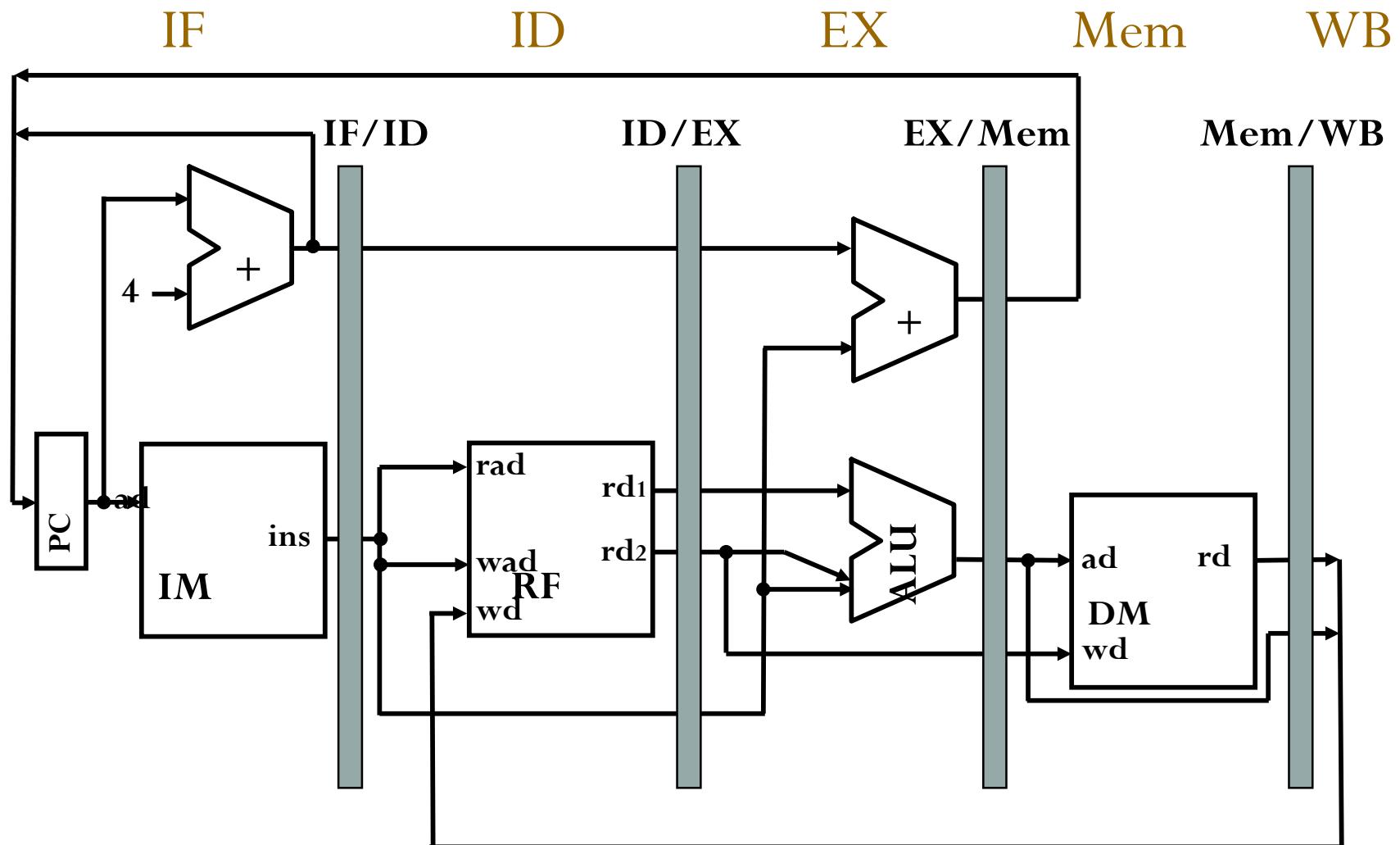

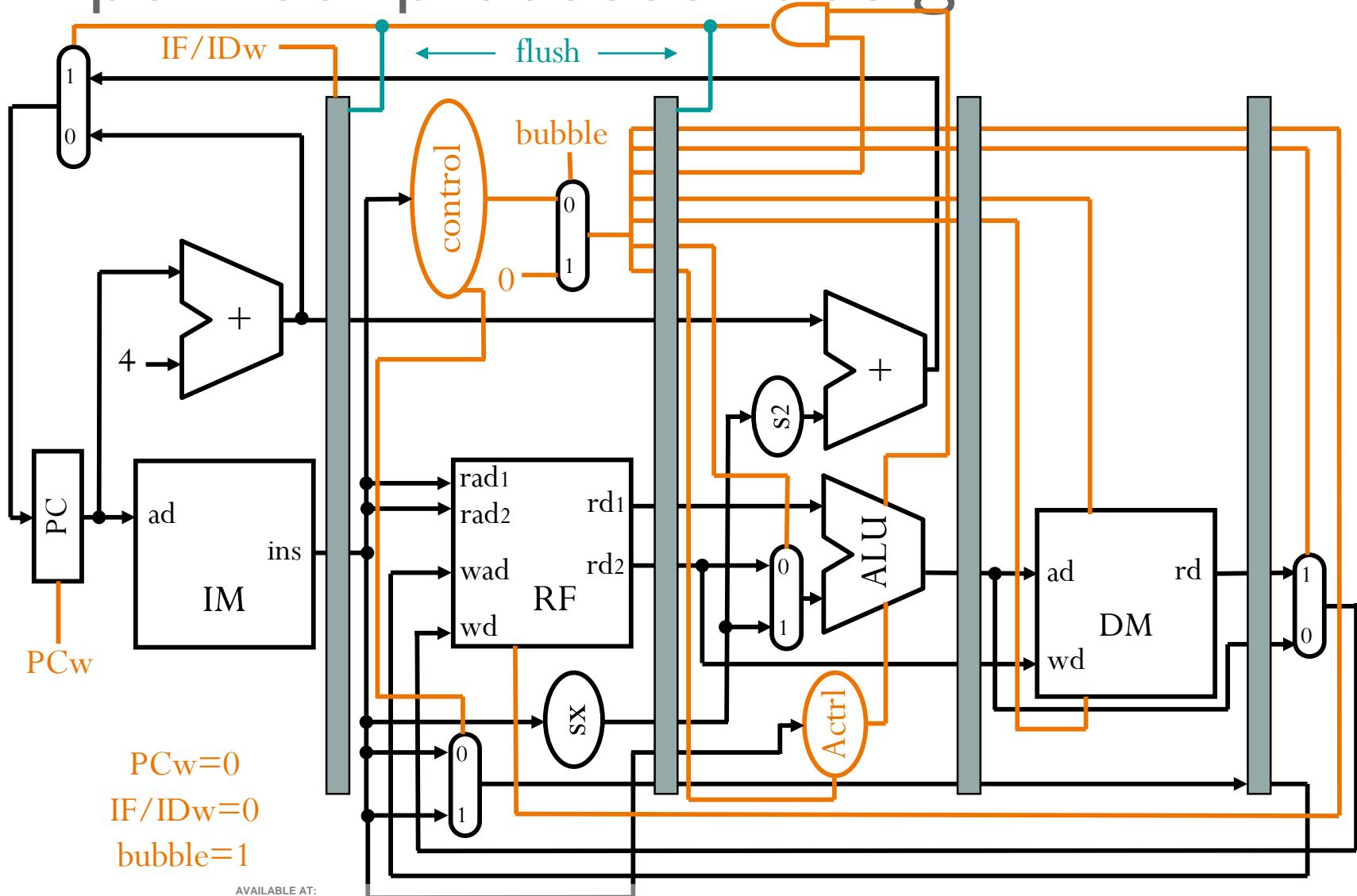

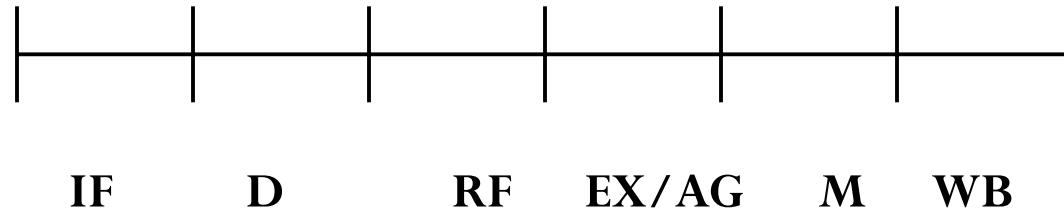

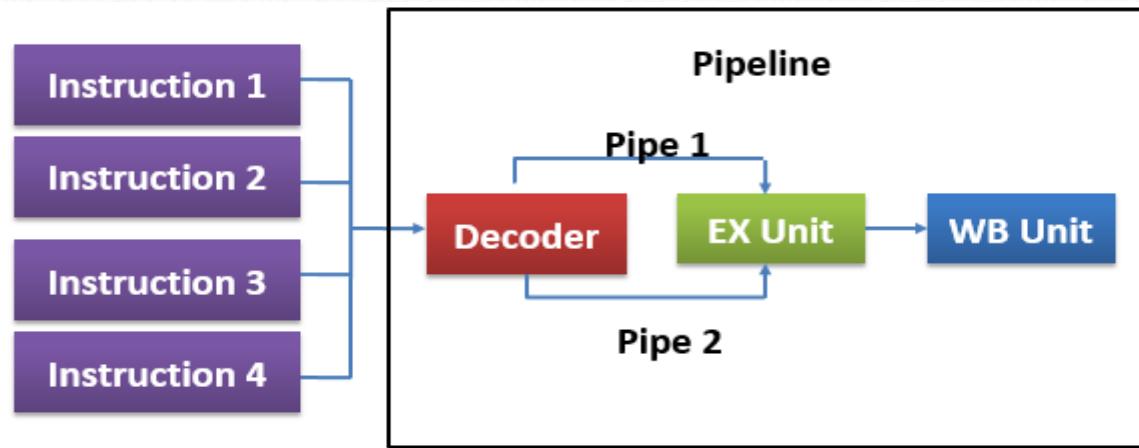

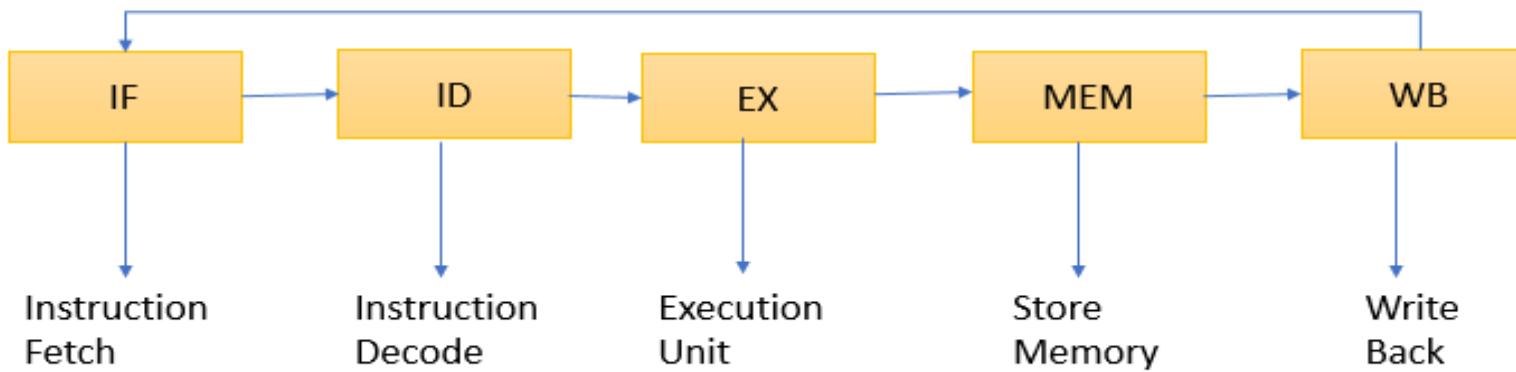

# Pipelined datapath (abstract)

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Fetch new instruction every cycle

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Pipelined processor design

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

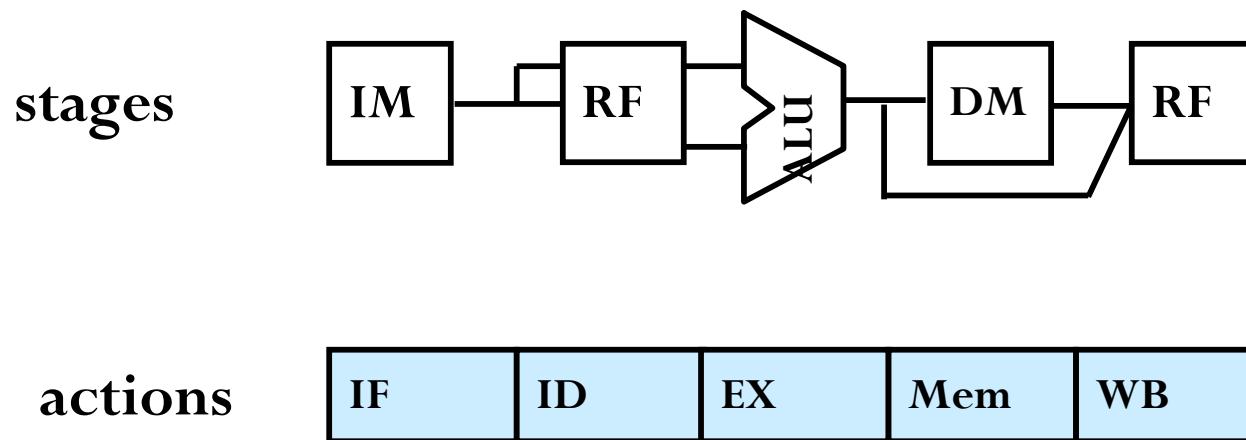

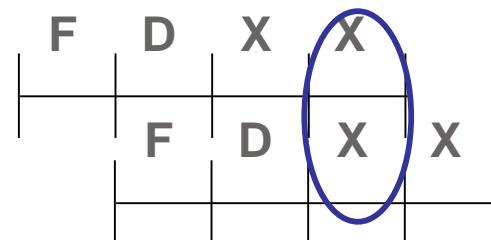

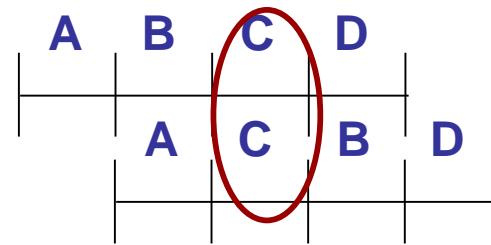

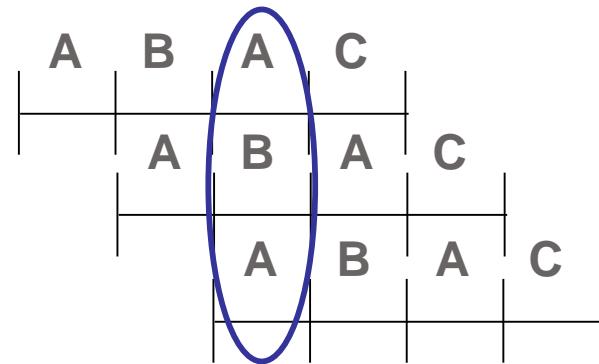

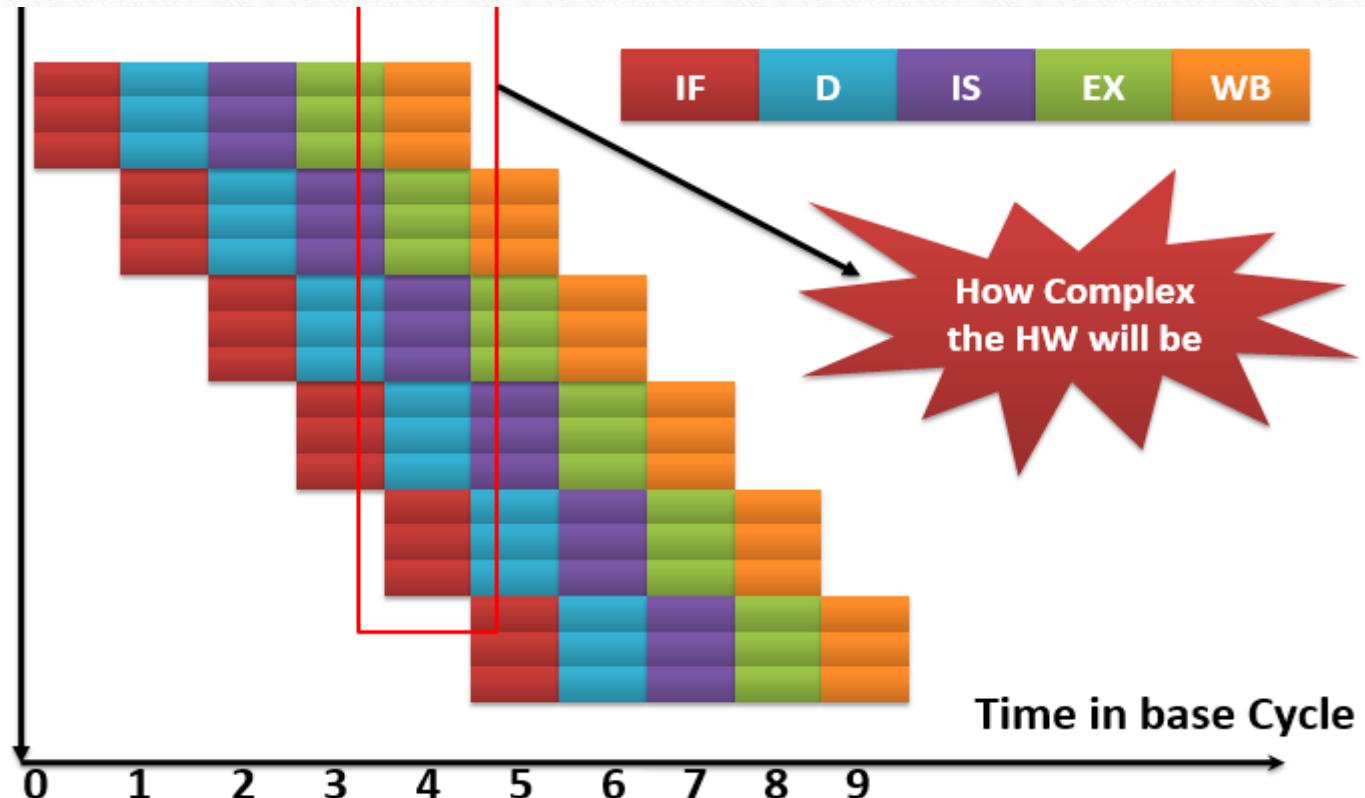

# Graphical representation

## 5 stage pipeline

# Usage of stages by instructions

# Pipelining

Simple multicycle design :

- Resource sharing across cycles

- All instructions may not take same cycles

- Faster throughput with pipelining

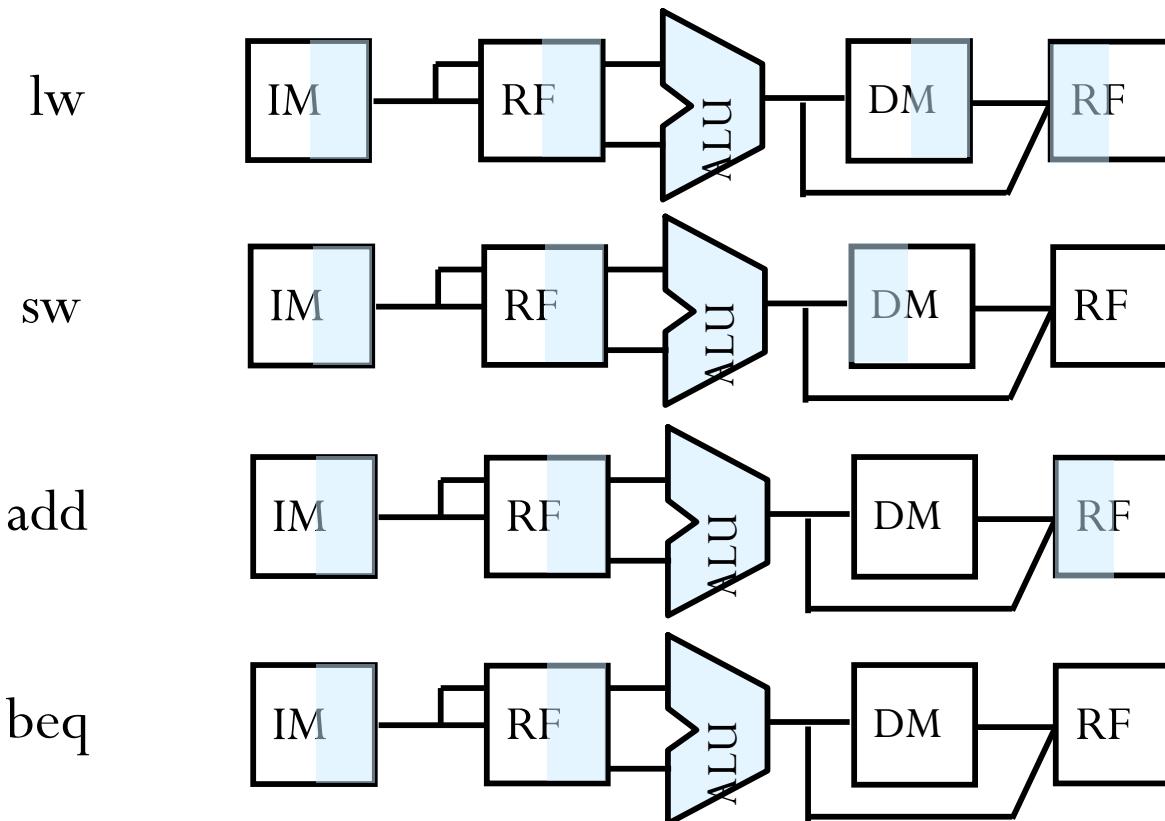

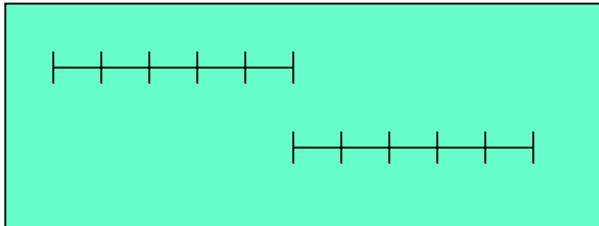

# Degree of overlap

**Serial**

**Overlapped**

**Pipelined**

# Depth

**Shallow**

**Deep**

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

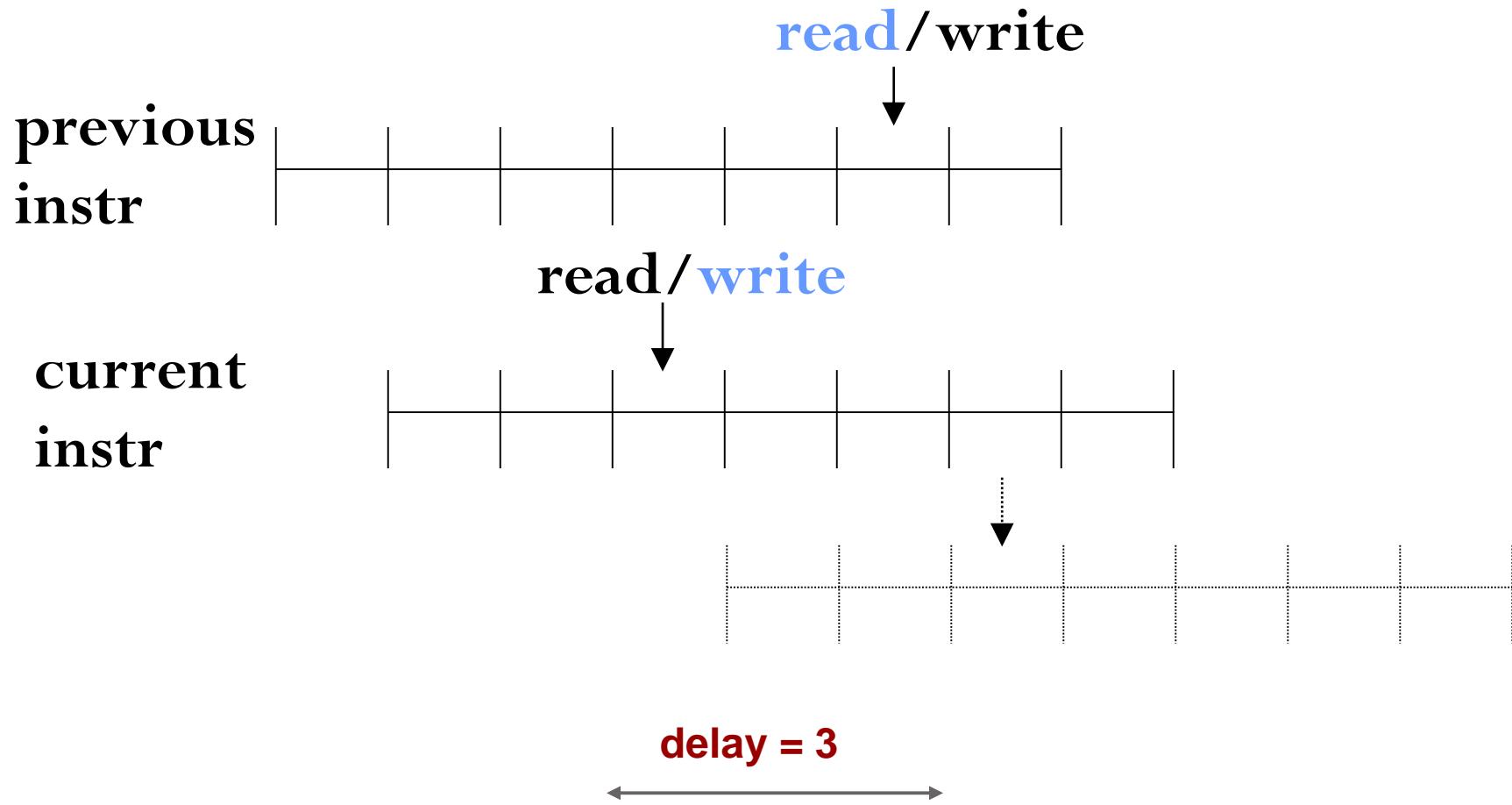

# *Hazards in Pipelining*

- Procedural dependencies => Control hazards

- cond and uncond branches, calls/returns

- Data dependencies => Data hazards

- RAW (read after write)

- WAR (write after read)

- WAW (write after write)

- Resource conflicts => Structural hazards

- use of same resource in different stages

# Data Hazards

# Structural Hazards

## Caused by Resource Conflicts

- Use of a hardware resource in more than one cycle

- Different sequences of resource usage by different instructions

- Non-pipelined multi-cycle resources

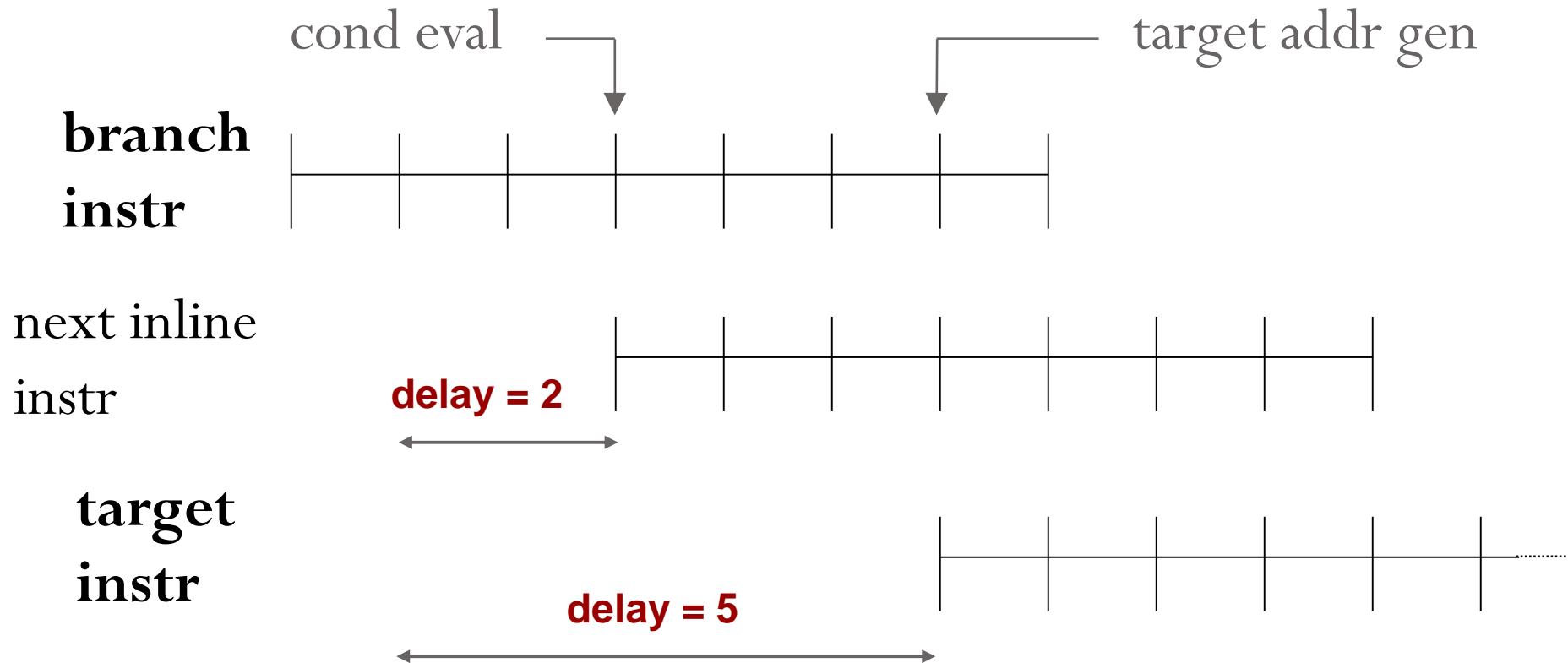

# Control Hazards

- the order of *cond eval* and *target addr gen* may be different

- *cond eval* may be done in previous instruction

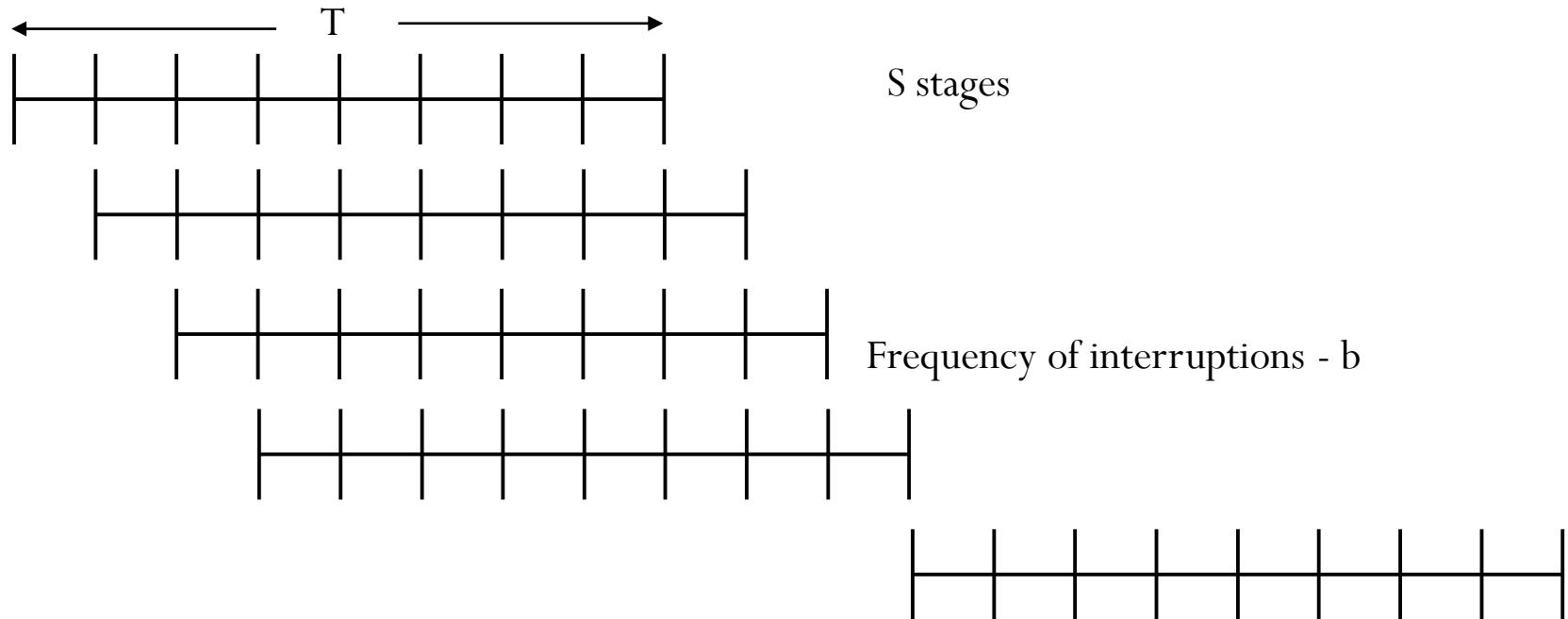

# Pipeline Performance

$$CPI = 1 + (S - 1) * b$$

$$\text{Time} = CPI * T / S$$

# Improving Branch Performance

- **Branch Elimination**

- Replace branch with other instructions

- **Branch Speed Up**

- Reduce time for computing CC and TIF

- **Branch Prediction**

- Guess the outcome and proceed, undo if necessary

- **Branch Target Capture**

- Make use of history

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Branch Elimination

Use conditional instructions

(predicated execution)

OP1

BC CC = Z, \* + 2

ADD R3, R2, R1

OP2

OP1

ADD R3, R2, R1, NZ

OP2

## Branch Speed Up :

Early target address generation

- Assume each instruction is Branch

- Generate target address while decoding

- If target in same page omit translation

- After decoding discard target address if not Branch

# Branch Prediction

- Treat conditional branches as unconditional branches / NOP

- Undo if necessary

## Strategies:

- Fixed (*always guess inline*)

- Static (*guess on the basis of instruction type*)

- Dynamic (*guess based on recent history*)

# Static Branch Prediction

| Instr    | %    | Guess  | Branch | Correct     |

|----------|------|--------|--------|-------------|

| uncond   | 14.5 | always | 100%   | 14.5%       |

| cond     | 58   | never  | 54%    | 27%         |

| loop     | 9.8  | always | 91%    | 9%          |

| call/ret | 17.7 | always | 100%   | 17.7%       |

|          |      |        |        | Total 68.2% |

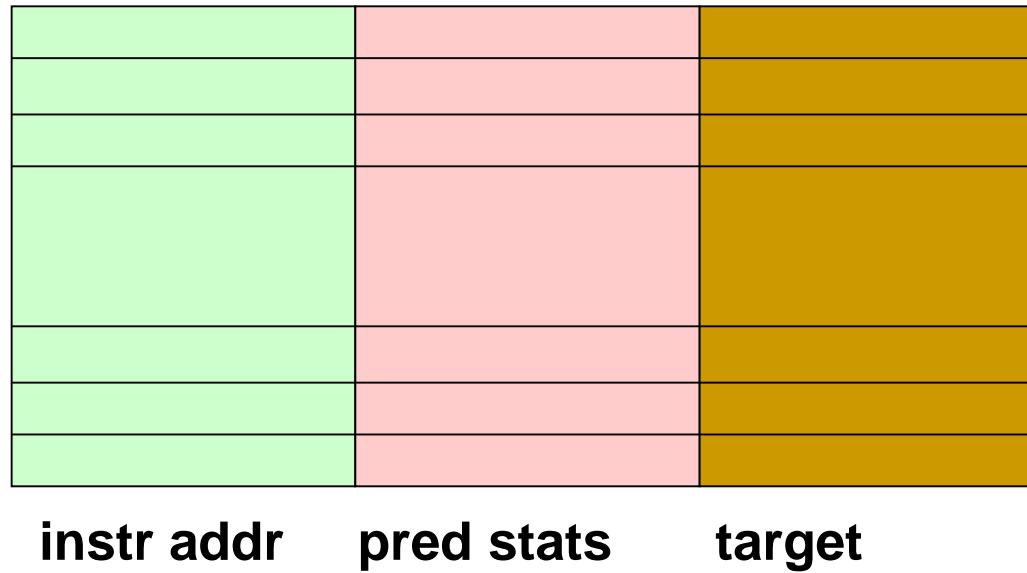

# Branch Target Capture

- Branch Target Buffer (BTB)

- Target Instruction Buffer (TIB)

**prob of target change < 5%**

**target addr**

**target instr**

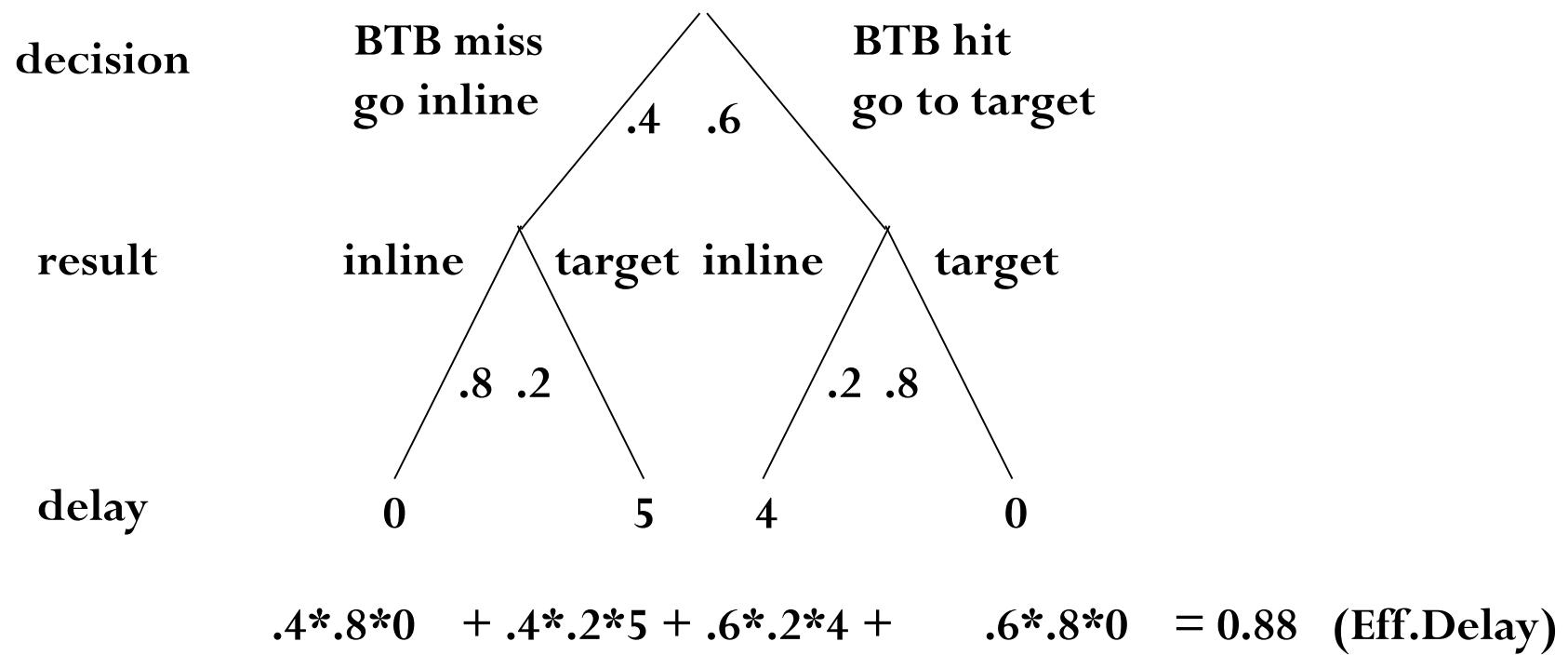

# BTB Performance

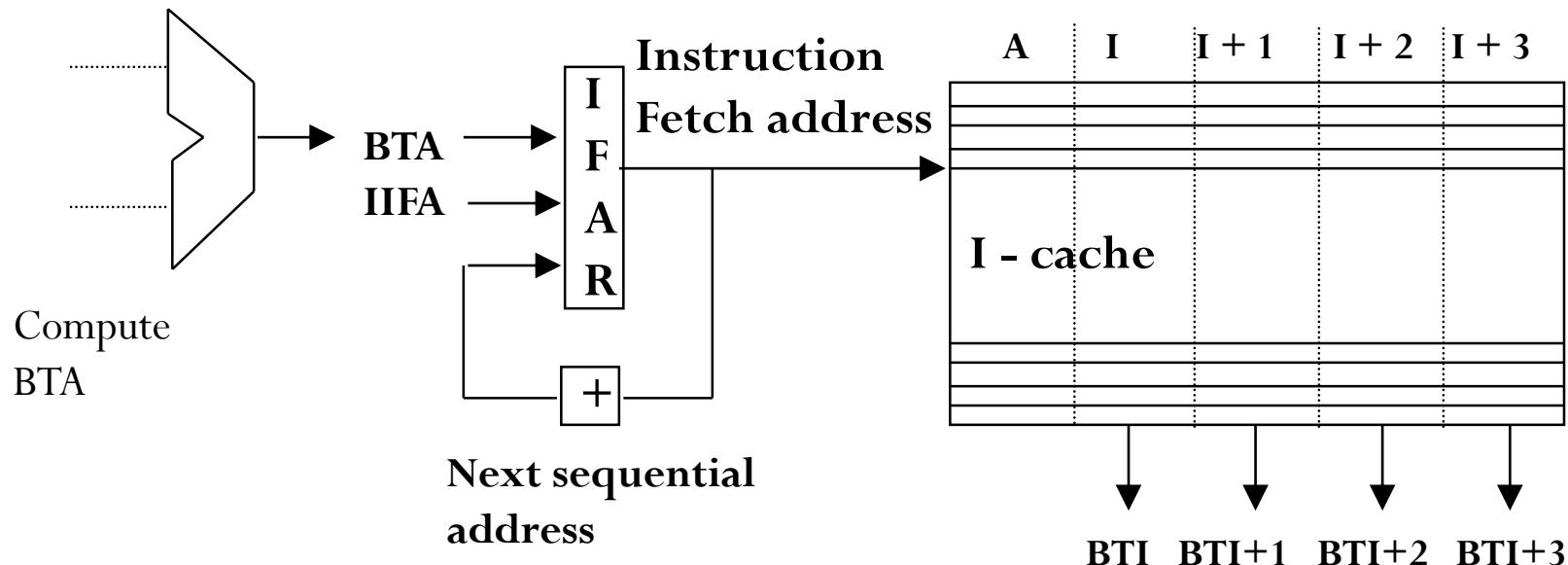

# Compute/fetch scheme

(no dynamic branch prediction)

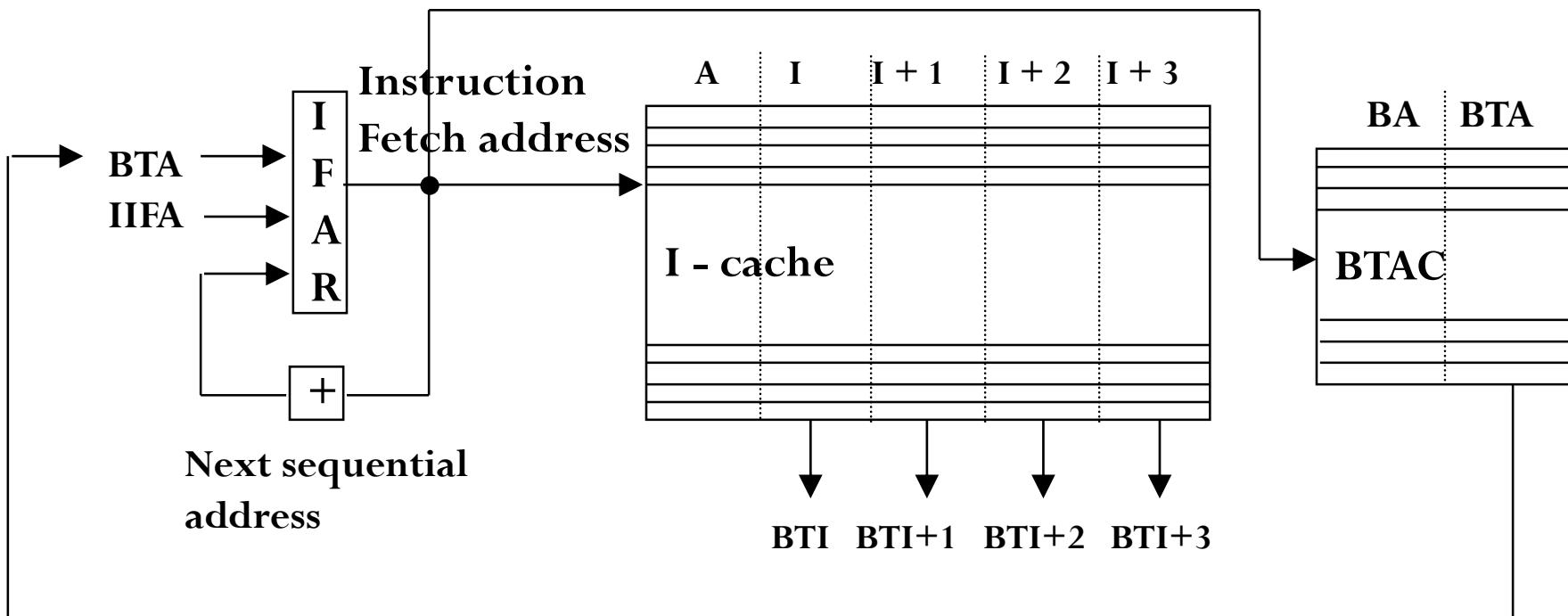

# BTAC scheme

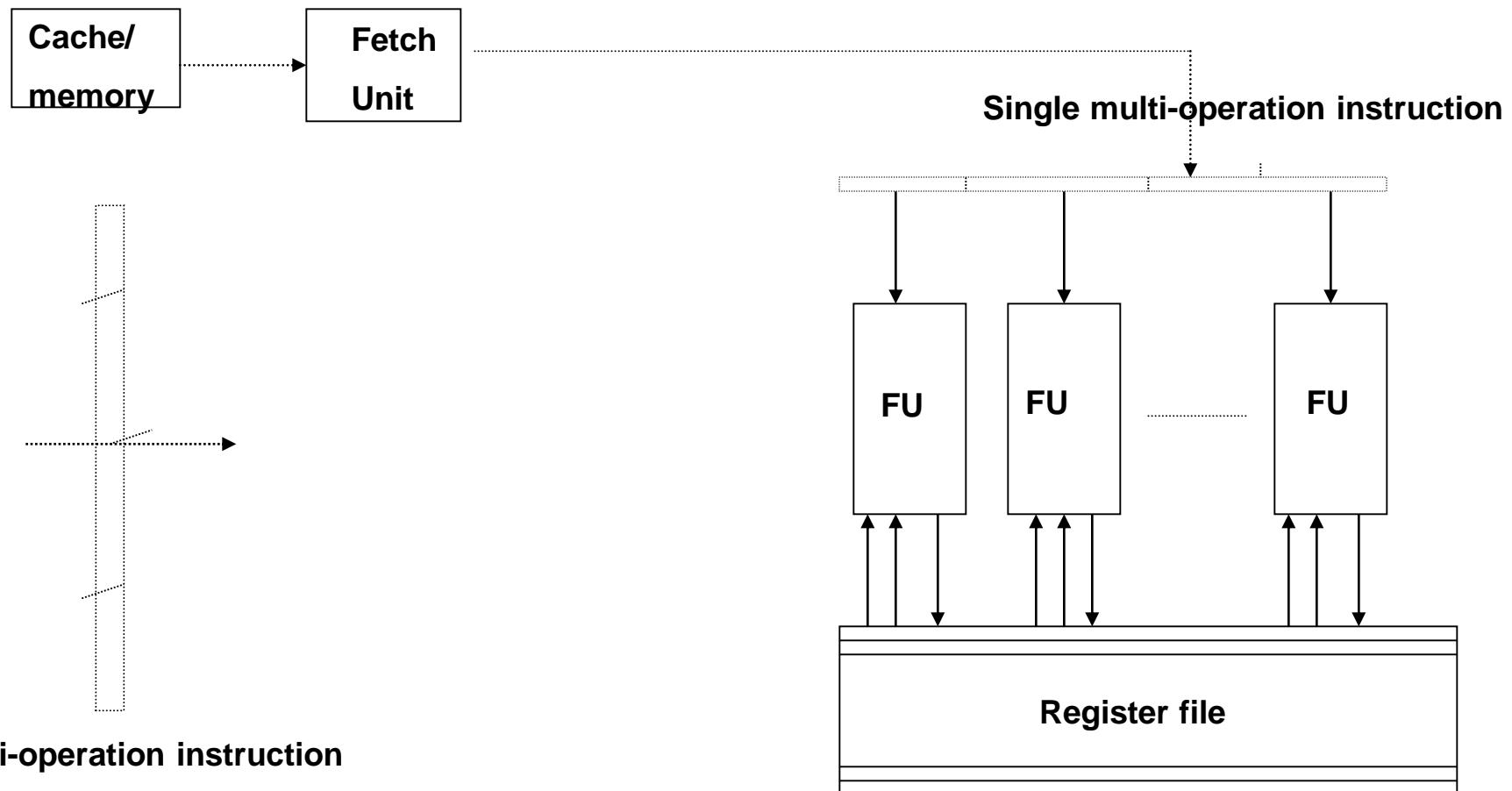

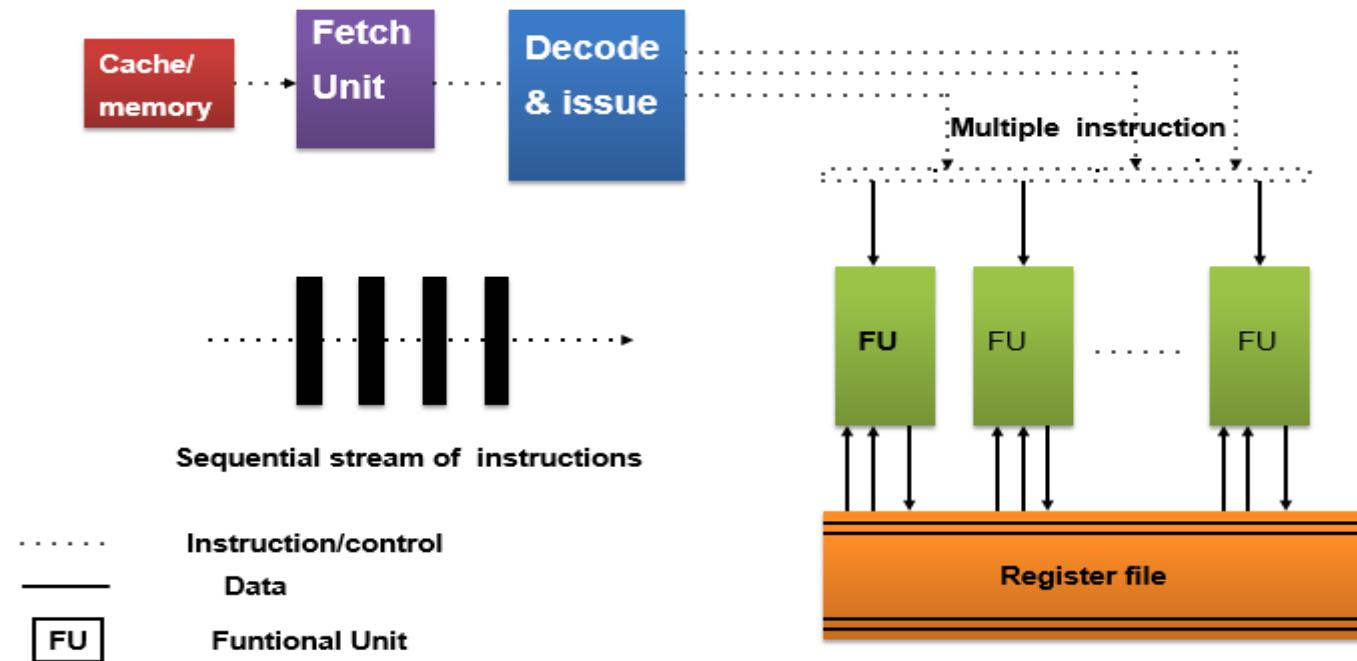

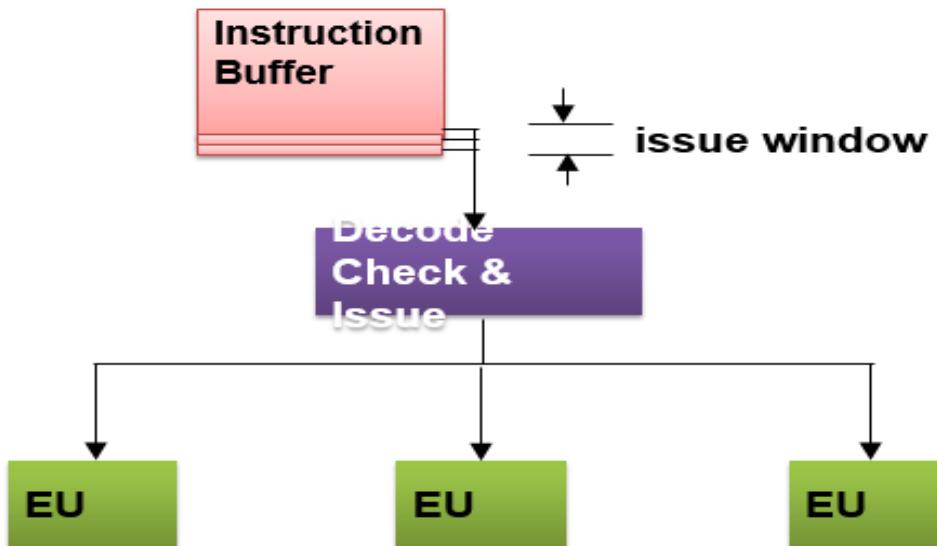

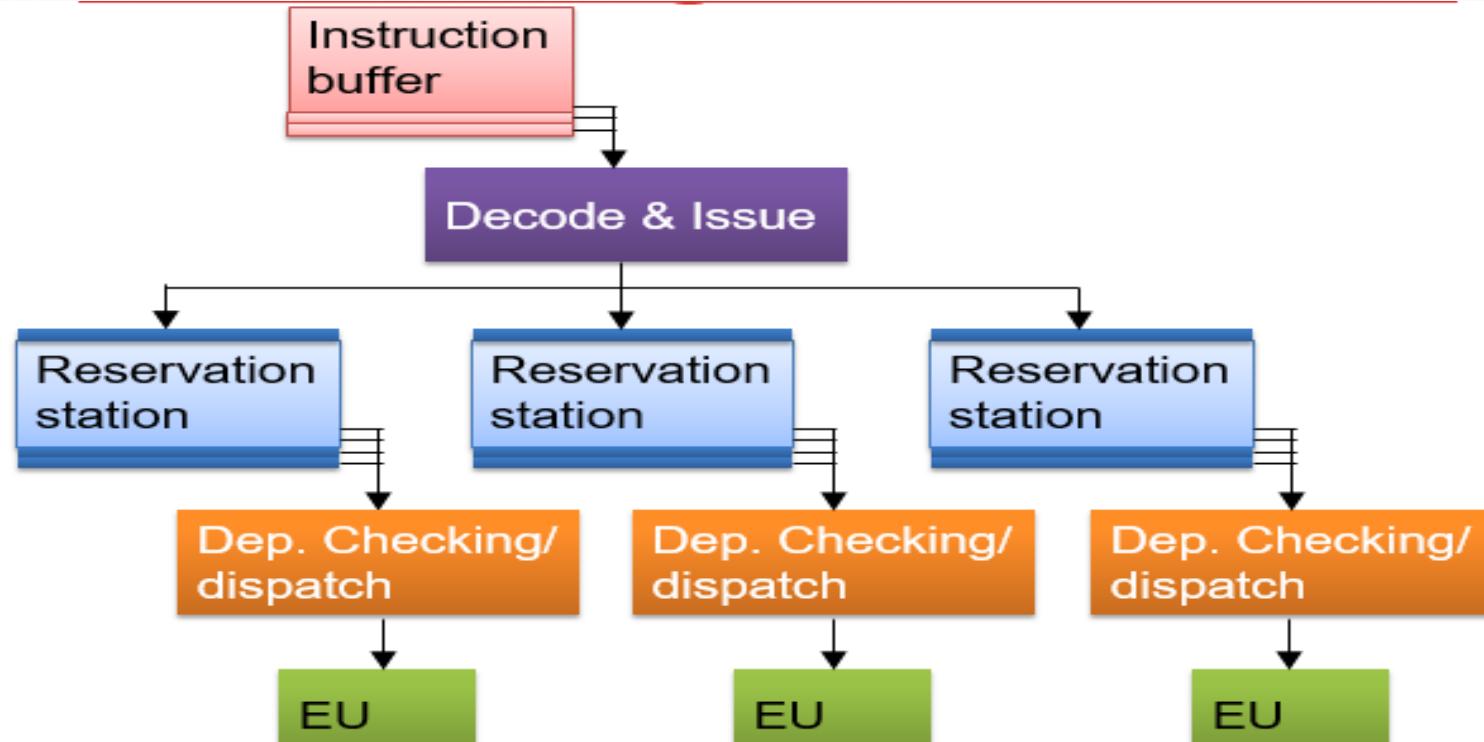

# ILP in VLIW processors

**multi-operation instruction**

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

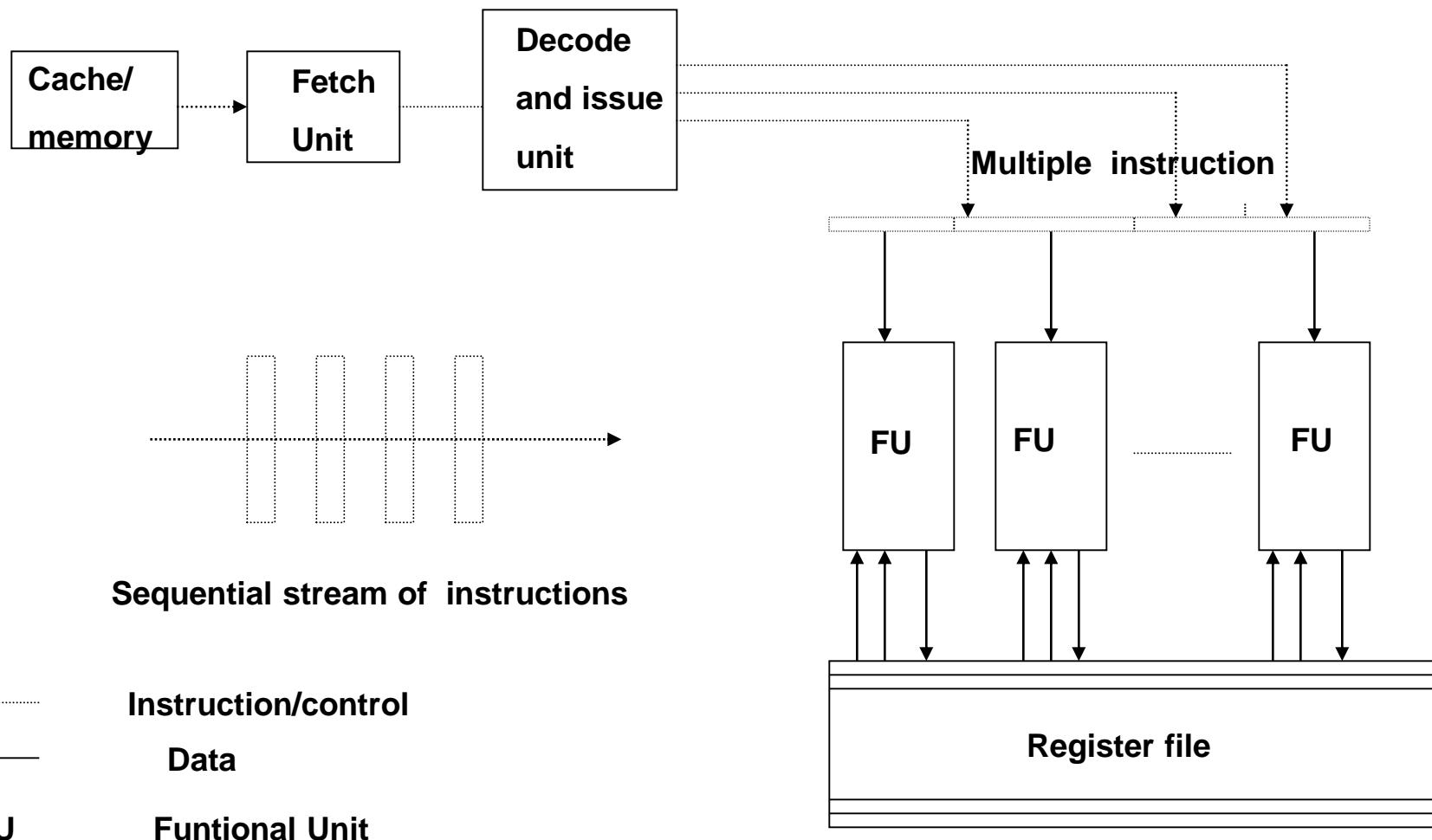

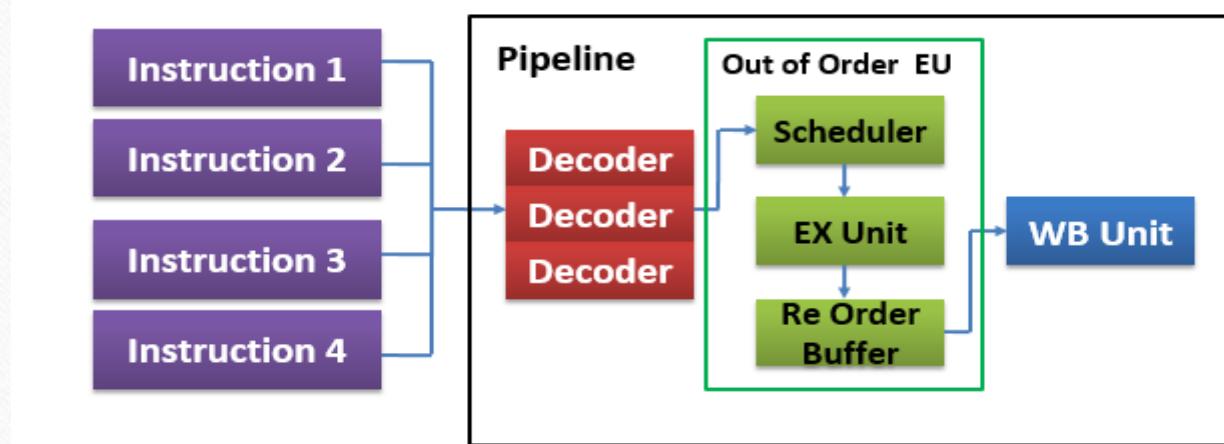

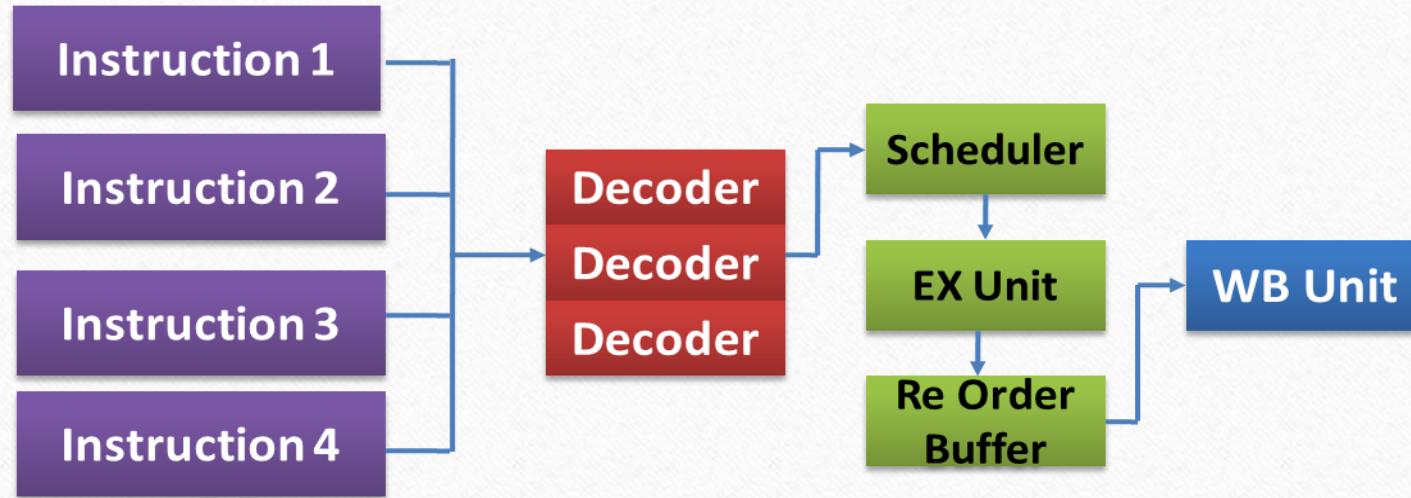

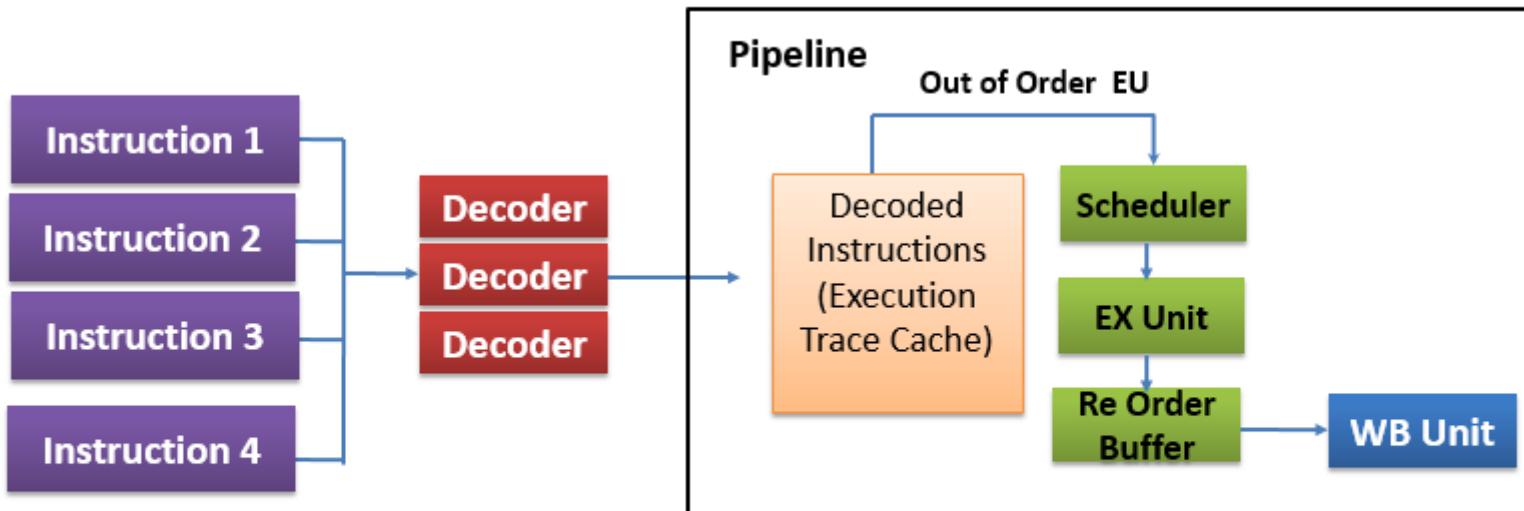

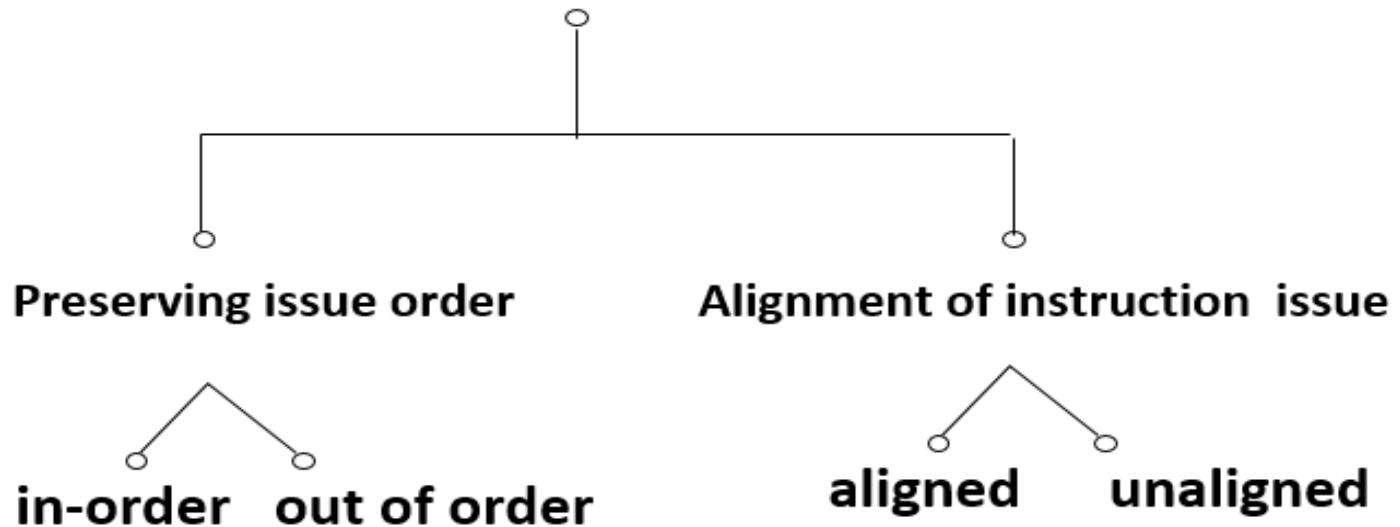

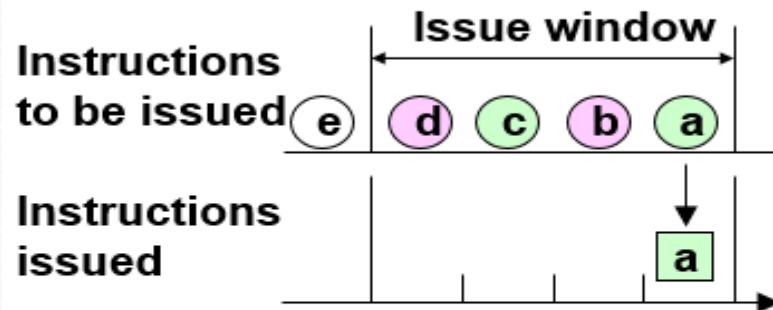

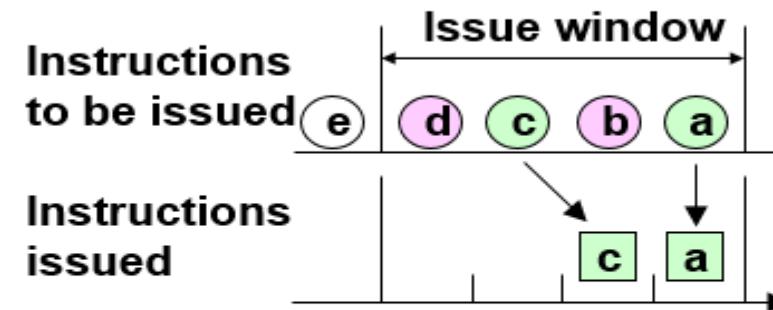

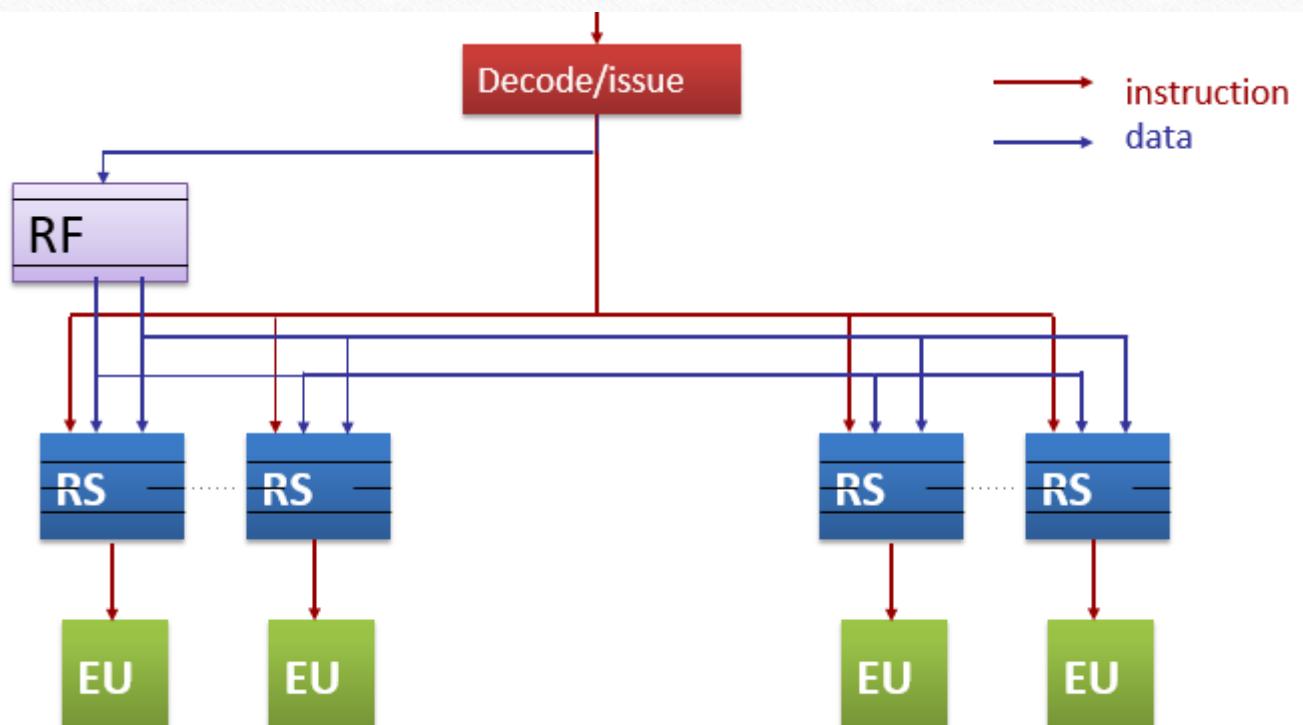

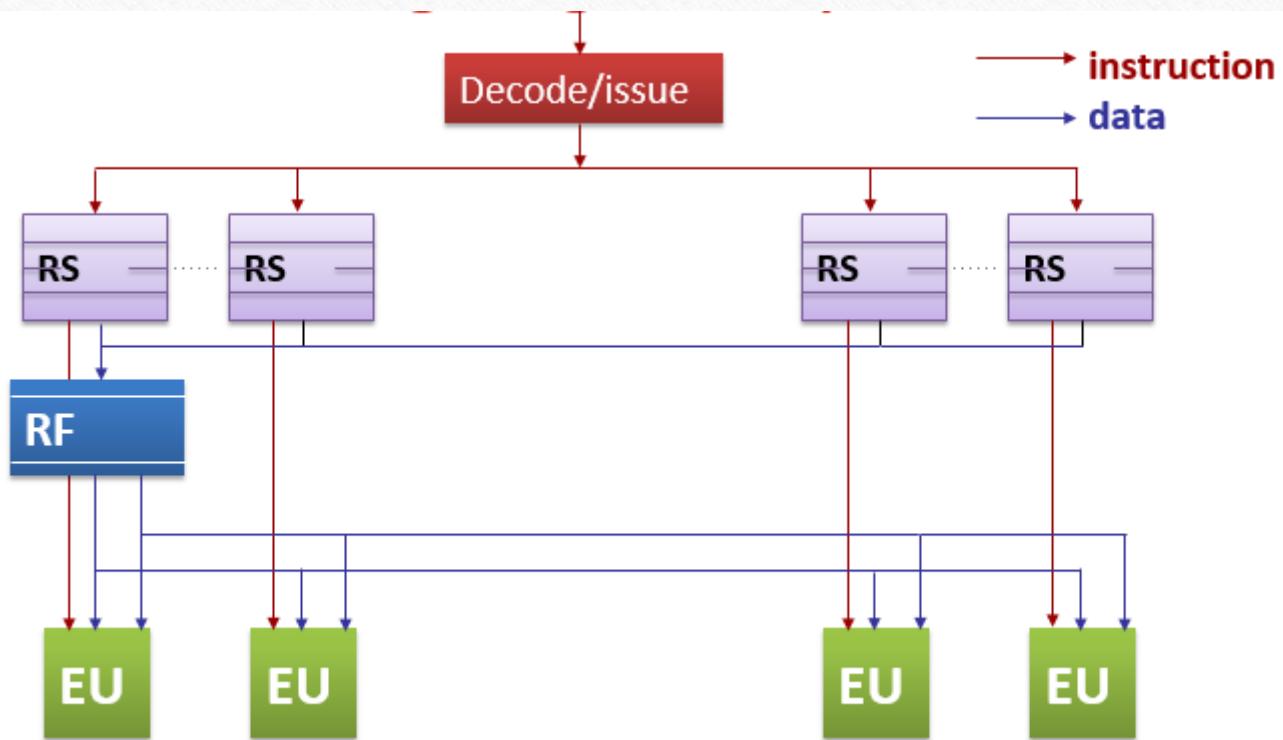

# ILP in Superscalar processors

# Why Superscalars are popular ?

- Binary code compatibility among scalar & superscalar processors of same family

- Same compiler works for all processors (scalars and superscalars) of same family

- Assembly programming of VLIWs is tedious

- Code density in VLIWs is very poor - Instruction encoding schemes

# Hierarchical structure

Speed

Size

Cost / bit

Fastest

Smallest

Highest

Memory

Slowest

Biggest

Lowest

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

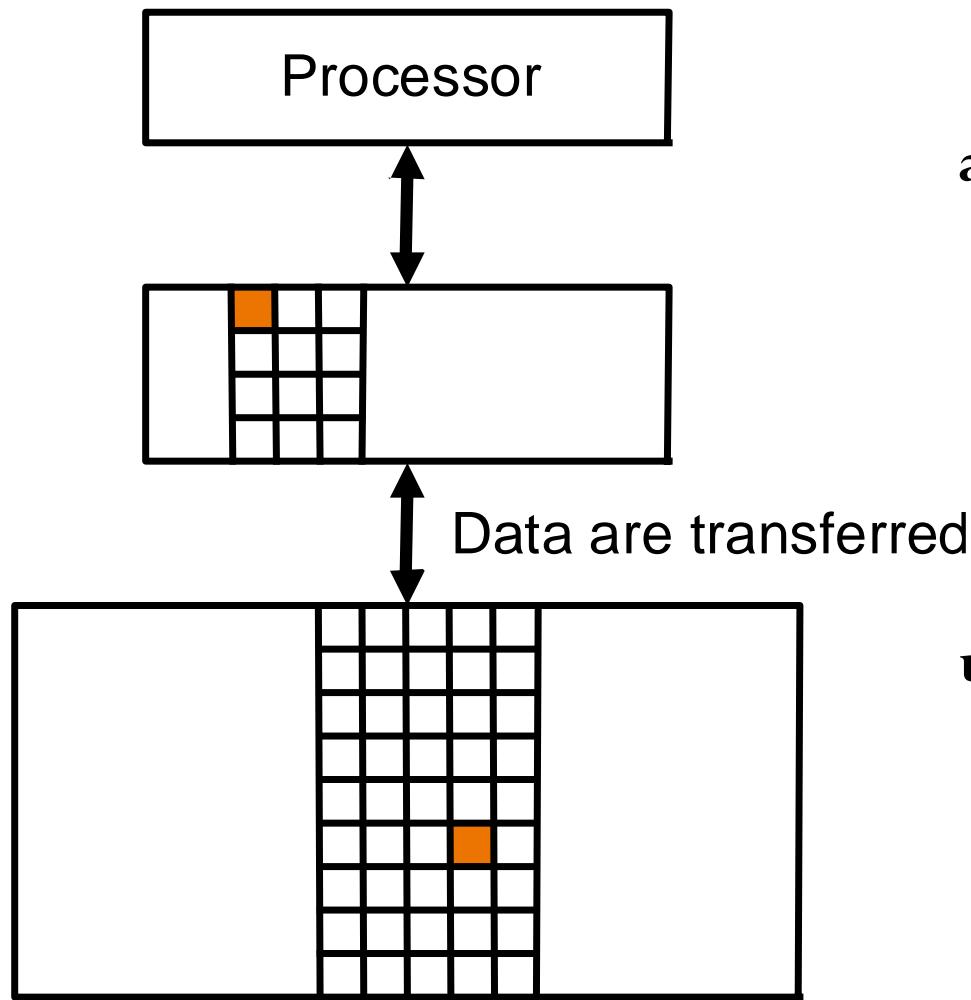

# Data transfer between levels

access

hi

t

miss

**unit of transfer = block**

# Principle of locality & Cache Policies

- Temporal Locality

- references repeated in time

- Spatial Locality

- references repeated in space

- Special case: Sequential Locality

---

- **Read**

- Sequential / Concurrent

- Simple / Forward

- **Load**

- Block load / Load forward / Wrap around

- **Replacement**

- LRU / LFU / FIFO / Random

# Load policies

Cache miss on AU 1

**Block Load**

**Load Forward**

**Fetch Bypass

(wrap around

load)**

# Fetch Policies

- Demand fetching

- fetch only when required (miss)

- Hardware prefetching

- automatically prefetch next block

- Software prefetching

- programmer decides to prefetch

## questions:

- how much ahead (prefetch distance)

- how often

# Write Policies

- Write Hit

- Write Back

- Write Through

- Write Miss

- Write Back

- Write Through

- With Write Allocate

- With No Write Allocate

# Cache Types

Instruction | Data | Unified | Split

Split vs. Unified:

- Split allows specializing each part

- Unified allows best use of the capacity

On-chip | Off-chip

- on-chip : fast but small

- off-chip : large but slow

Single level | Multi level

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# References

1. Patterson, D A.; Hennessy, J L. *Computer Organization and Design: The Hardware/software Interface*. Morgan Kaufman, 2000

2. Sima, T, FOUNTAIN, P KACSUK, *Advanced Computer Architectures: A Design Space Approach*, Pearson Education, 1998

3. Flynn M J, *Computer Architecture: Pipelined and Parallel Processor Design*, Narosa publishing India, 1999

4. John L. Hennessy, David A. Patterson, Computer architecture: a quantitative approach, 2<sup>nd</sup> Ed, Morgan Kauffman, 2001

# Thanks

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# 8085 Architecture & Its Assembly language programming

**PRESENTED BY: GROUP-03

MEMBERS:**

- Sumaia Islam Taj (20CSE034)

- Muaaz Bin Zahid (20CSE039)

- Rashedul Islam (20CSE047)

- Deepanwita Roy(20CSE024)

- Nure Hafsa Shefa(20CSE018)

- Abdullah Al Mahin(20CSE031)

- Md. Saifuzzaman Abhi (20CSE052)

- Sarabar Tahura (20CSE029)

- Nahid Forhad (20CSE020)

**PRESENTED TO:**

Dr. Tania Islam

Assistant

Professor, Dept of

CSE, University of

Barishal

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Outline

- 8085 Era and Features

- 8085

- Pin diagram

- Block diagram (Data Path)

- Bus Structure

- Register Structure

- Instruction Set of 8085

- Sample program of 8085

- Simulator & Kit for 8085

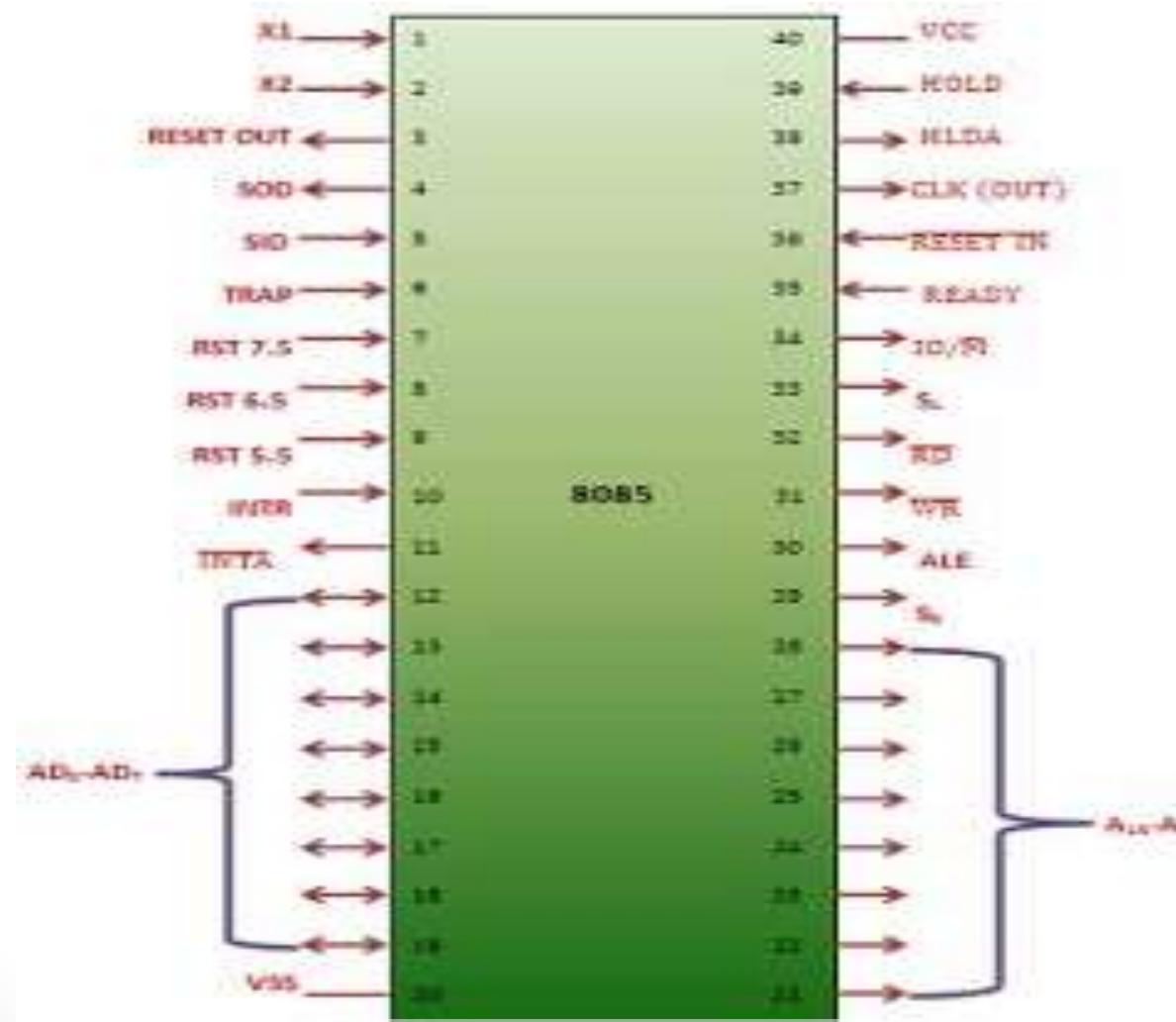

# 8085 Microprocessor

- 8 Bit CPU

- 3-6Mhz

- Simpler design: Single Cycle CPU

- 40 Pin Dual line Package

- 16 bit address

- 6 registers: B, C, D, E, H,L

- Accumulator 8 bit

**Note:** Architecture of 8085 microprocessor - GeeksforGeeks

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# 8085 Pin diagram

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

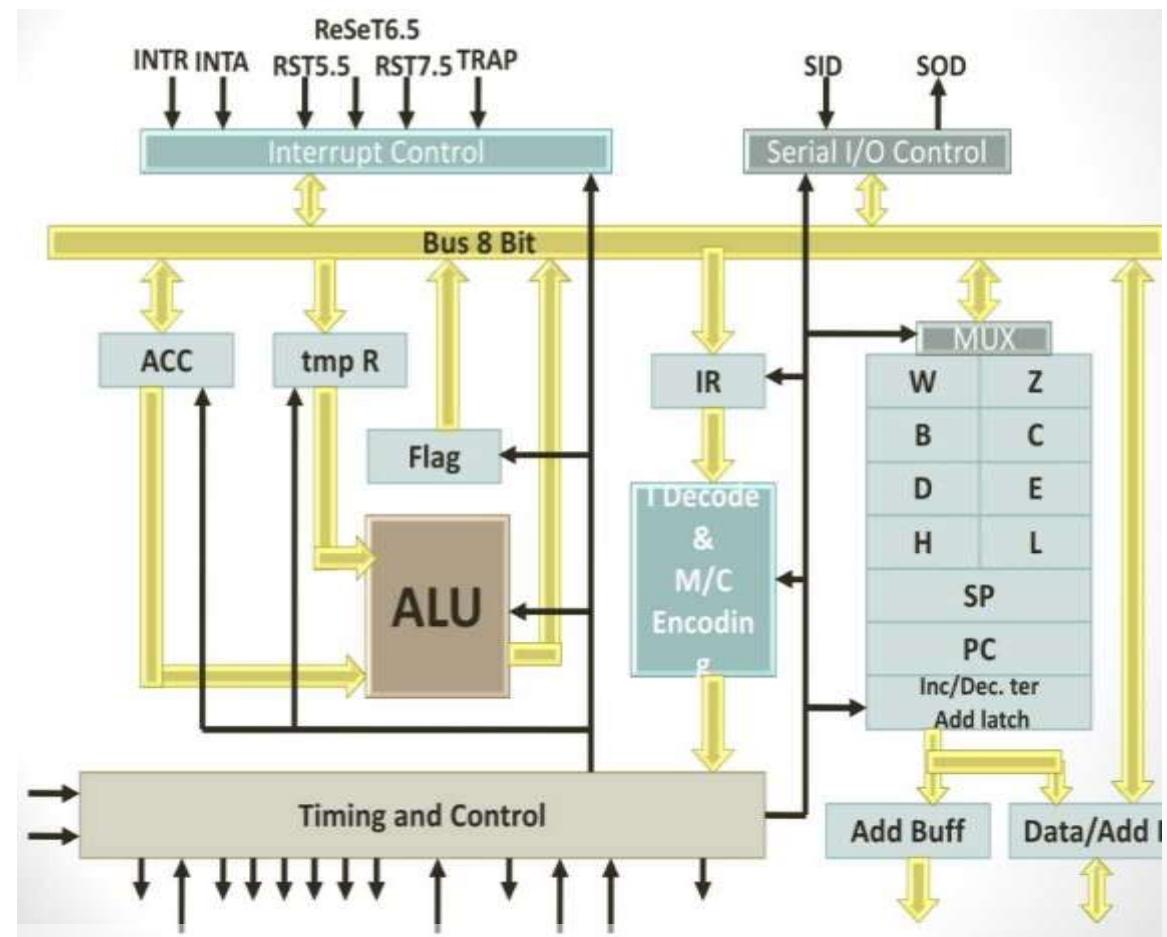

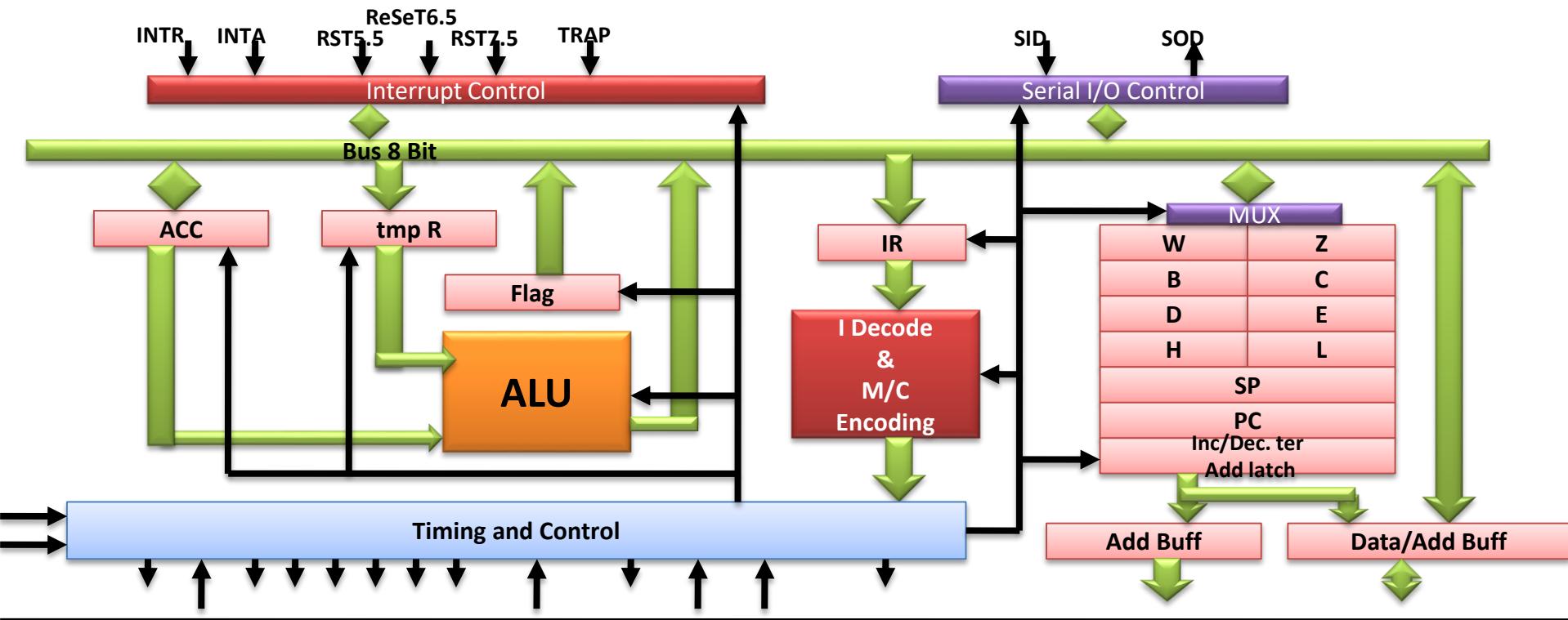

# 8085 Microprocessor Architecture

The Block Diagram of 8085 Microprocessor

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

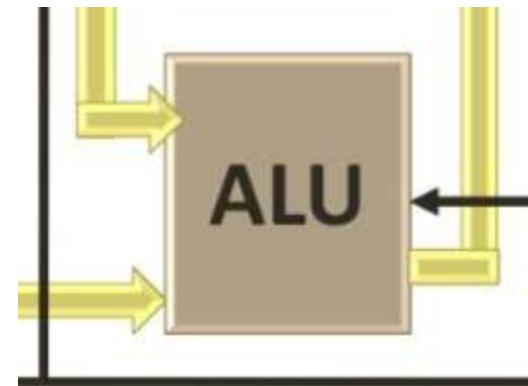

# ALU

- **ALU (Arithmetic and Logic Unit):**

- Performs 8-bit operations such as addition, subtraction, AND, OR, and XOR.

- Interacts with the Accumulator (ACC) and Temporary Register (temp R).

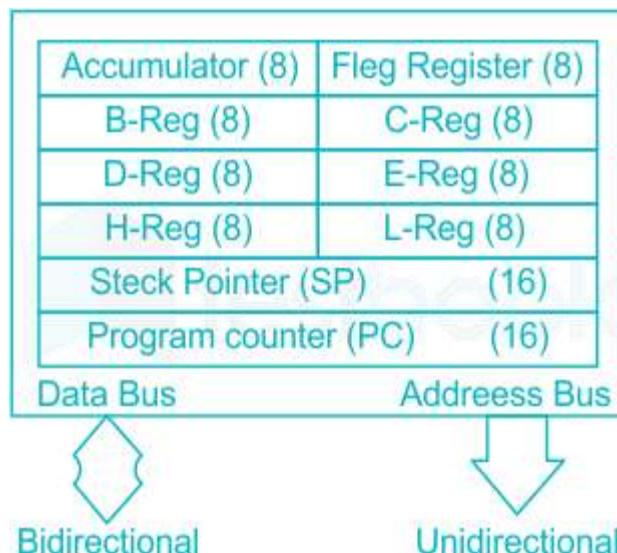

# Registers

- **Accumulator (ACC)**

- **Temporary Register (tmp R):** Used internally by the ALU during operations.

- **Flag Register**

- **W, Z Registers:** Temporary storage.

- **General-Purpose Registers**

- **Stack Pointer (SP) and Program Counter (PC)**

|    |   |

|----|---|

| W  | Z |

| B  | C |

| D  | E |

| H  | L |

| SP |   |

| PC |   |

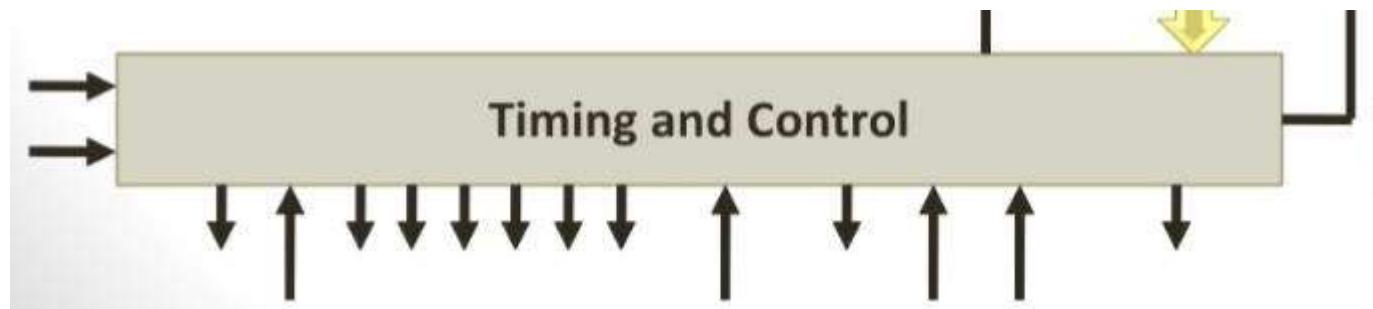

# Timing and Control Unit

- Synchronizes and controls the execution of instructions.

- Generates necessary control signals (RD, WR, ALE) and status signals (IO/M, S0, S1).

- Manages the clock cycles and fetch-execute cycle for instructions.

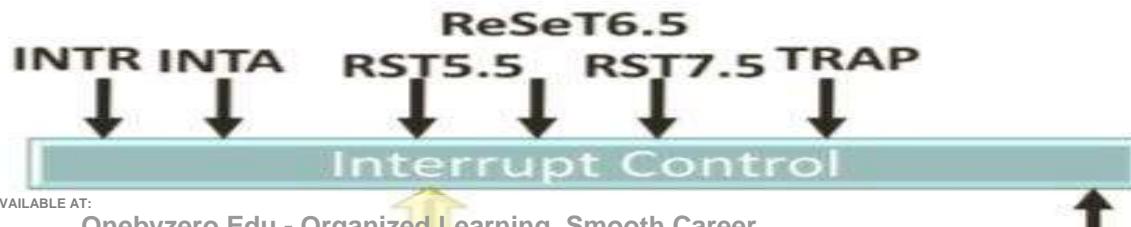

# Interrupt Control Unit

- Manages five interrupt signals: INTR, RST5.5, RST6.5, RST7.5, TRAP.

- TRAP: Non-maskable interrupt with the highest priority.

- RST5.5, RST6.5, RST7.5: Maskable, vectored interrupts.

- INTR and INTA (Interrupt Acknowledge): General-purpose interrupt and its acknowledgement.

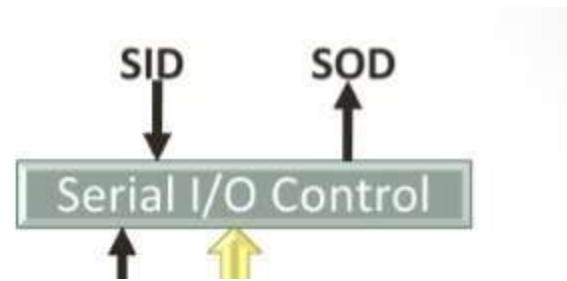

# Serial I/O Control Unit

- **Serial I/O Block:**

- Facilitates serial communication through:

- SID (Serial Input Data): Receives serial data.

- SOD (Serial Output Data): Sends serial data.

- Used for communicating with serial peripherals or data transfer over long distances.

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

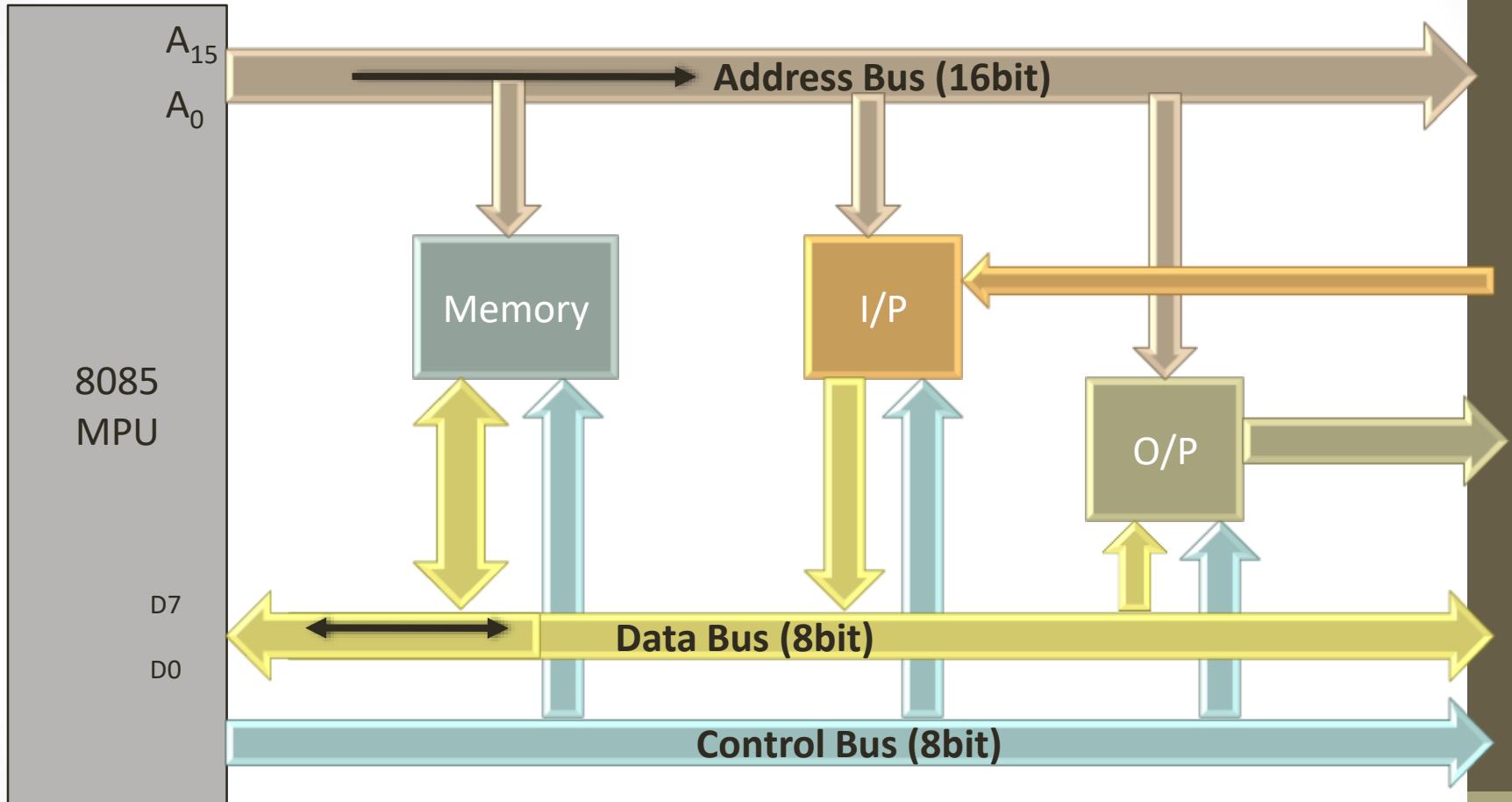

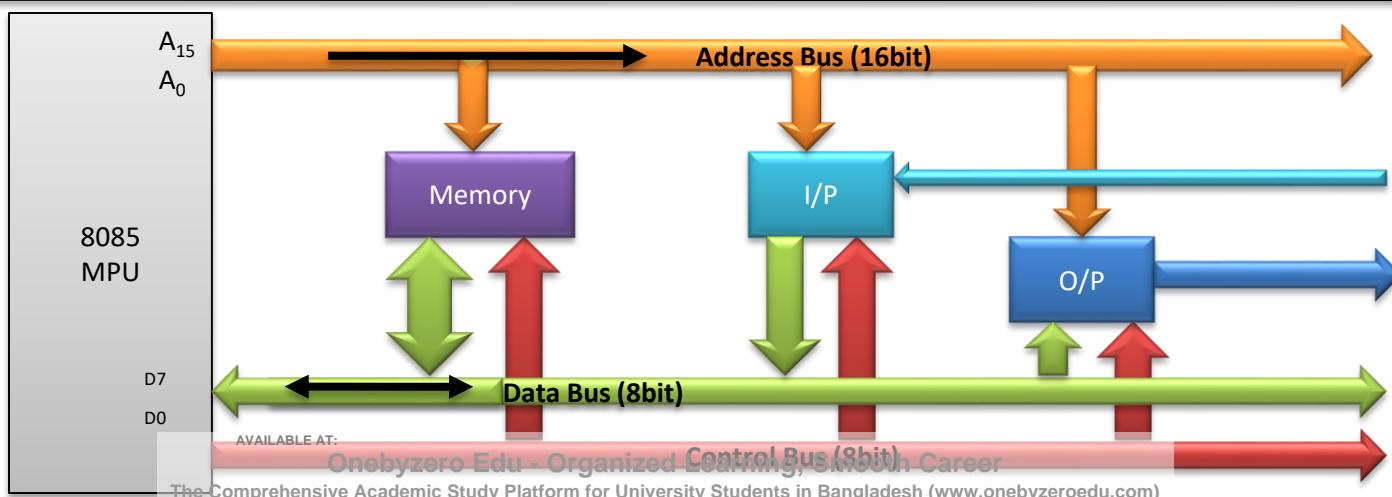

# **Data and Address Bus System**

- **Data Bus (8-bit):**

- **Transports** 8-bit data between the microprocessor and peripherals or memory.

- **Address Bus (16-bit):**

- Carries memory and I/O addresses to access data or instructions.

- **Add Buffer and Data/Address Latches:**

- Temporarily store data and addresses to manage timing during bus transactions.

# Multiplexer and Program Counter

- **Multiplexer (MUX):**

-

- Combines data inputs from various sources like the registers and flags to pass them onto the appropriate internal bus lines.

- **Program Counter (PC):**

-

- Holds the address of the next instruction to be executed.

- Increments automatically as instructions are executed.

# The 8085 Bus Structure

# 8085 Bus Structure

**1. Address Bus:** A collection of wires used to identify location in main memory is called Address Bus. It is a group of 16 lines generally marked as A0 to A15. It is unidirectional which flow from microprocessor to Input Output devices. The address bus carries address bits. It is used to identify IO peripheral or a memory location.

**2. Data Bus:** A collection of wires through which data is transmitted from one part of a computer to another is called Data Bus. It is a group of 8 lines used for data flow generally mark as D0 to D7. These lines are bidirectional. This bus connects all the computer components to the CPU and main memory. Data flow in both directions between microprocessor and memory.

**3. Control bus :**

The control bus is a bidirectional bus that is used to carry control signals between the microprocessor and other components such as memory and I/O devices. It is used to transmit commands to the memory or I/O devices

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# **8085 Bus Structure**

performing specific operations.

1. Memory read

2. Memory write

3. I/O read

4. I/O Write

5. Opcode fetch

**Why use Bus organization in 8085 microprocessor ?**

1. Memory access

2. I/O operations

3. Control signal transfer

4. DMA operations

# 8085 Registers

### • (a) General Purpose Registers:

- Six general purpose 8-bit registers: B, C, D, E, H, L

- Combined as register pairs to perform 16-bit operations: BC, DE, HL

- Registers are programmable (load, move, etc.)

# Register 1

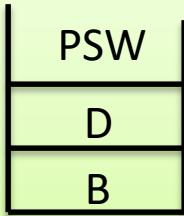

## (b) Specific Purpose Registers –

**Accumulator:** an 8-bit register

**Flag registers:** 5 flag registers are:

- **Carry Flag (CF)** : It occupies the zero th bit of the flag register. If the arithmetic operation results in a carry(if result is more than 8 bit), then Carry Flag is set; otherwise it is reset.

- **Parity Flag (PF)** : It occupies the second bit of the flag register. This flag tests for number of 1's in the accumulator. If the accumulator holds even number of 1's, then this flag is set and it is said to even parity. On the other hand if the number of 1's is odd, then it is reset and it is said to be odd parity.

| $B_7$ | $B_6$ | $B_5$ | $B_4$ | $B_3$ | $B_2$ | $B_1$ | $B_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|

| S     | Z     | —     | AC    | —     | P     | —     | CY    |

fig(a)-Bit position of various flags in flag registers of 8085

# Register 2

- **Auxiliary Carry Flag (AF)** : AF = 1 if there is a carry out from bit 3 on addition, or a borrow into bit 3 on subtraction.

- **Sign Flag (SF)** : It occupies the seventh bit of the flag register, which is also known as the most significant bit. It helps the programmer to know whether the number stored in the accumulator is positive or negative. If the sign flag is set, it means that number stored in the accumulator is negative, and if reset, then the number is positive.

- **Zero Flag (ZF)** : It occupies the sixth bit of the flag register. It is set, when the operation performed in the ALU results in zero(all 8 bits are zero), otherwise it is reset. It helps in determining if two numbers are equal or not.

# Register 3

**(c) Memory Registers** – There are two 16-bit registers used to hold memory addresses.

- **Program Counter:** This register is used to sequence the execution of the instructions.

- **Stack Pointer:** It is used as a memory pointer. It points to a memory location in read/write memory, called the stack.

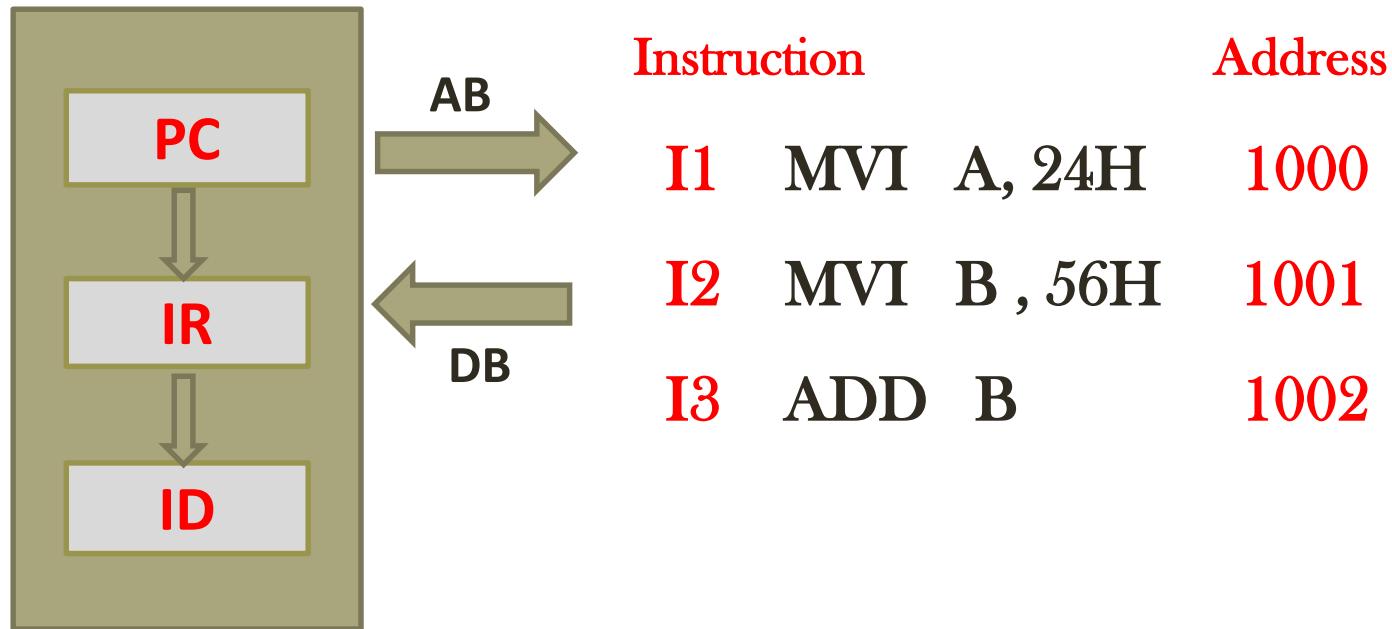

# **How instruction executed**

- All instructions (of a program) are stored in memory.

- To run a program, the individual instructions must be read from the memory in sequence, and executed.

- Program counter puts the 16-bit memory address of the instruction on the address bus

- Control unit sends the Memory Read Enable signal to access the memory

- The 8-bit instruction stored in memory is placed on the data bus and transferred to the instruction decoder

- Instruction is decoded and executed

# Instruction Set of 8085

- **Arithmetic Operations**

- ADD, SUB, INR/DCR

- Example : 'ADD B', 'SUB C'

- **Logical operation**

- AND, OR, XOR, Rotate(RLC, RRC), Compare(CMP), Complement.

- Example : 'CMP E'

- **Branch operation**

- Jump(JMP), CALL, Return(RET)

- Example : 'JMP 2000H'

- **Data transfer/Copy/Memory operation/IO**

- MOV, MVI, LD, ST, OUT

- Example : 'MOV A,B'

# Copy/Mem/IO operation

- **MVI R, 8 bit** // load immediate data

*Example:* MVI A, 25H

- **MOV R1, R2**

*Example :* MOV B, A

- **MOV R M** // Copy to R from address pointed by (HL Reg)

*Example : If HL points to '2000H', 'MOV B,M' load the contents of '2000H' into register B.*

- **MOV M R** // Copy from R to (HL Reg)

*Example : If HL points to '2000H' and B has '05H', 'MOV M,B' stores '05H' at memory location '2000H'*

# Copy/Mem/IO operation

- **LDA 16 bit** // load A from (16bit)

*Example: 'LDA 2000H'*

- **STA 16 bit** // Store A to (16bit)

*Example : 'STA 2000H'*

- **LDAX Rp** // Load A from address pointed by (Rp) Rp=Register Pair

*Example : If BC = 3000H, 'LDAX B' loads A with the contents of memory location 3000H.*

- **STAX Rp** // Store A to (Rp)

*Example : If DE = 4000H and A = 0AH, 'STAX D' stores 0AH at memory location 4000H.*

- **LXI Rp 16bit** // load immediate to Rp

*Example : 'LXI H, 3000H'*

# Arithmetic Operation

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

- **ADD R** (Add Register to Accumulator) // **SUB R** (Subtract Register from Accumulator)

- Description: This instruction adds the content of a specified register (B, C, D, E, H, L) to the Accumulator (A). The result is stored in the Accumulator..

- **Syntax: ADD R**

- Example: If A = 05H and B = 03H, after executing ADD B, A will become 08H.

- **ADI 8-bit** (Add Immediate to Accumulator) // **SUI 8-bit** (Subtract Immediate from Accumulator)

- Description: This instruction adds an 8-bit immediate value to the Accumulator. The result is stored in the Accumulator.

- **Syntax: ADI 20H (data)**

- Example: If A = 05H and the immediate data is 03H, after executing ADI 03H, A will become 08H.

- **ADD M** (Add Memory to Accumulator) // **SUB M** (Subtract Memory from Accumulator)

- Description: This instruction adds the content of the memory location pointed to by the HL register pair to the Accumulator. The result is stored in the Accumulator.

- Syntax: **ADD M**

- Example: If A = 05H, and HL points to memory location 2000H which contains 03H, after executing ADD M, A will become 08H.

- **INR R** (Increment Register) // **DCR R** (Decrement Register)

- Description: This instruction increments the content of the specified register by 1.

- Syntax: **INR R**

- Example: If B = 03H, after executing INR B, B will become 04H.

- **INR M** (Increment Memory) // **DCR M** (Decrement Memory)

- Description: This instruction increments the content of the memory location pointed to by the HL register pair by 1.

- Syntax: **INR M**

- Example: If the memory location 2000H contains 03H and HL points to 2000H, after executing INR M, the memory content at 2000H will become 04H.

- **INX Rp** (Increment Register Pair) // **DCX Rp** (Decrement Register Pair)

- Description: This instruction increments the content of the specified register pair (BC, DE, HL, or SP) by 1.

- Syntax: **INX Rp**

- Example: If HL = 2000H, after executing INX H, HL will become 2001H.

# Other Operations

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

## Logic Operations

- **ANA R**

**Example:** If A = 0AH and B = 03H, after executing ANA B, A will become 02H

- **ANI 8bit**

**Example:** If A = 0AH and the immediate value is 03H, after executing ANI 03H, A will become 02H

- **ANA M**

**Example:** If A = 0AH and the memory location pointed to by HL contains 03H, after executing ANA M, A will become 02H.

- **ORA, ORI, XRA, XRI**

- **CMP R** (Compare Register with Accumulator) // **CPI 8-bit**

(Compare Immediate with Accumulator)

- **Description:** This instruction compares the content of the specified register with the Accumulator. The result is not stored, but the flags are set based on the comparison.

- **Syntax:** CMP R

- **Example:** If A = 05H and B = 03H, after executing CMP B, the Zero (Z) flag will be reset, indicating that A is greater than B.

| $(A - B) == 02H$ | ZF | CF | SF |

|------------------|----|----|----|

| A > B            | 0  | 0  | 0  |

| A = B            | 1  | 0  | 0  |

| A < B            | 0  | 1  | 1  |

## Branch Operations

- JMP 16-bit (Jump to Address) **Syntax:** JMP address `like : goto keyword in c++`

- CALL 16-bit (Call Subroutine) **Syntax:** CALL address `like : int sum(int a, int b) return a + b; in c++`

- JZ 16-bit (Jump if Zero) **Syntax:** JZ address `if(a == 0)`

- JNZ 16-bit (Jump if Not Zero) **Syntax:** JNZ address `if(a != 0)`

- JC 16-bit (Jump if Carry) **Syntax:** JC address `if(carry == 0)`

- JNC 16-bit (Jump if No Carry) **Syntax:** JNC address `if(carry != 0)`

- RET (Return from Subroutine) **Syntax:** RET

## Machine Control Operations

- HLT (Halt) **Syntax:** HLT (Executing HLT will stop the microprocessor.) **like : exit**

- NOP (No Operation) **Syntax:** NOP

- POP (Pop Data Off Stack) **Syntax:** POP Rp

- PUSH (Push Data Onto Stack) **Syntax:** PUSH Rp

INTERRUPTED = ( DI, EI.....) disable

# How Program Works

# Simple Assembly Program

## Addition of Two 8-bit Numbers

if perform any (Add, Subtract, Multiply etc. ) Operation one operand or value must be store accumulated register . And others value store temporary register.

MVI A, 0x12 ; Load 0x12 into Accumulator

MVI B, 0x34 ; Load 0x34 into register B

ADD B ; Add the content of B to Accumulator ( $A = A + B$ )

OUT 01H ; Display Result on port 01H

HLT ; Halt the program

# Q1: If I want to take input from user?

In 8085 assembly programming, the microprocessor does not have built-in support for direct input from a user (like `Scarf()` function in C language). Instead, user input is typically handled via **I/O ports** that connect to input devices.

## 1. Input via IN Instruction

### 2. Example:

```

MVI A, 00H      ; Load the port address into the Accumulator

IN 00H          ; Read data from port 00H into the Accumulator

MOV B, A        ; Move the input data from Accumulator to register B

HLT              ; Halt the program

```

## 3. Input/Output Devices Setup

- Connect input device to a particular I/O port on the 8085 microprocessor.

- Ensure that the device is mapped to a specific I/O port address (00H, 01H etc.)

# Q2: If I want to Add Two 16 bit Number ?

## Steps to Add Two 16-bit Numbers:

- Split the 16-bit numbers into two 8-bit parts

- Add the lower bytes of both numbers and store the result

- Add the higher bytes of both numbers and store the result

- Store the result.

### Example :

The **first** 16-bit number is stored in two consecutive memory locations

- Lower byte at memory location 2000H

- Higher byte at memory location 2001H

The **Second** 16-bit number is stored in two consecutive memory locations

- Lower byte at memory location 2002H

- Higher byte at memory location 2003H

The **result** of the addition will be stored in two consecutive memory locations

- Lower byte at memory location 2002H

- Higher byte at memory location 2003H

AVAILABLE AT

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Code to Add two 16 Bit number

## *//Load the First Number:*

LXI H, 2000H

MOV A, M

INX H

MOV B, M

## *//Load and Add the Second Number:*

LXI H, 2002H

ADD M

MOV L, A

INX H

ADC M

MOV H, A

## *//Store the Result:*

LXI D, 2004H

MOV M, L

INX D

MOV M, H

# Multiplication & Division

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

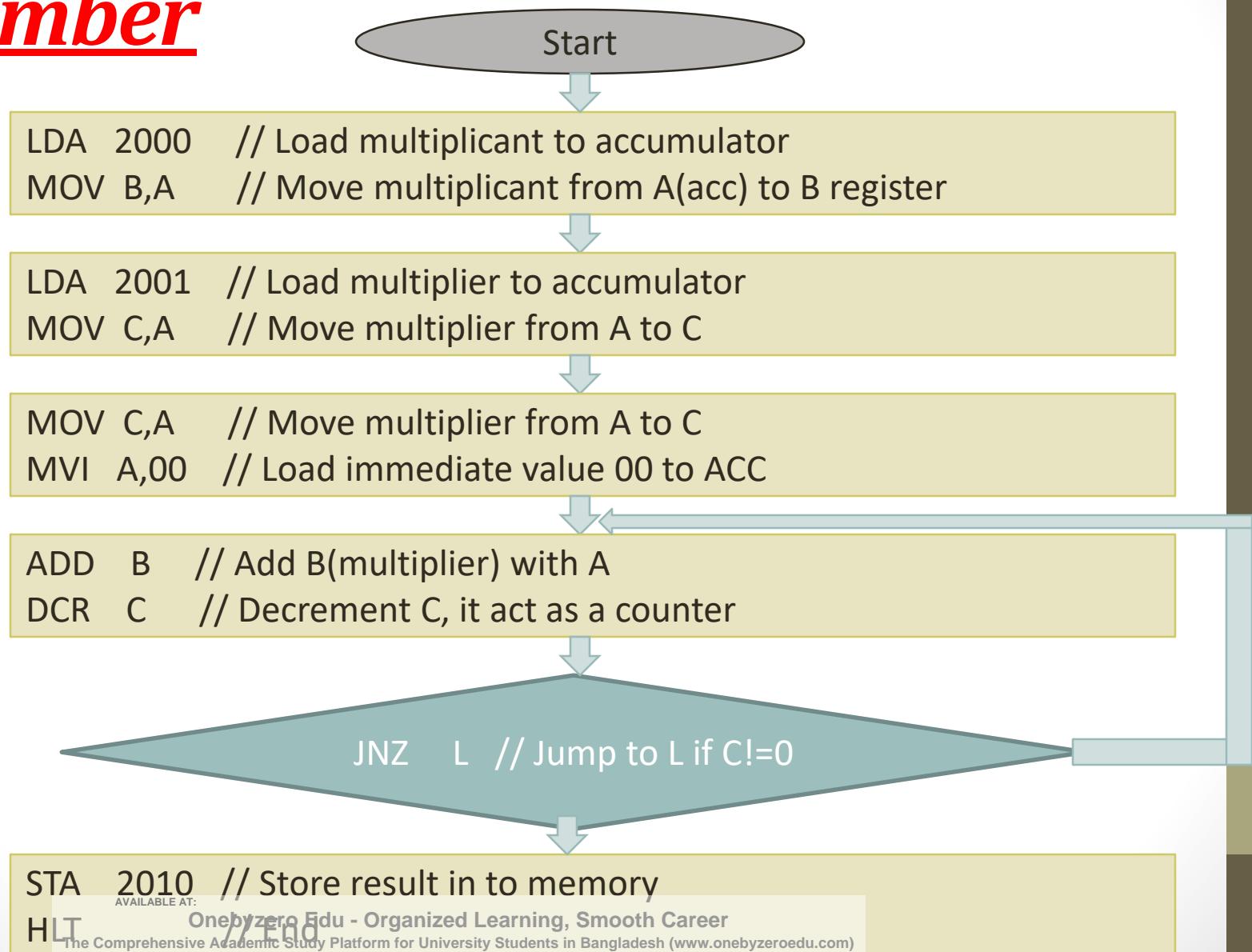

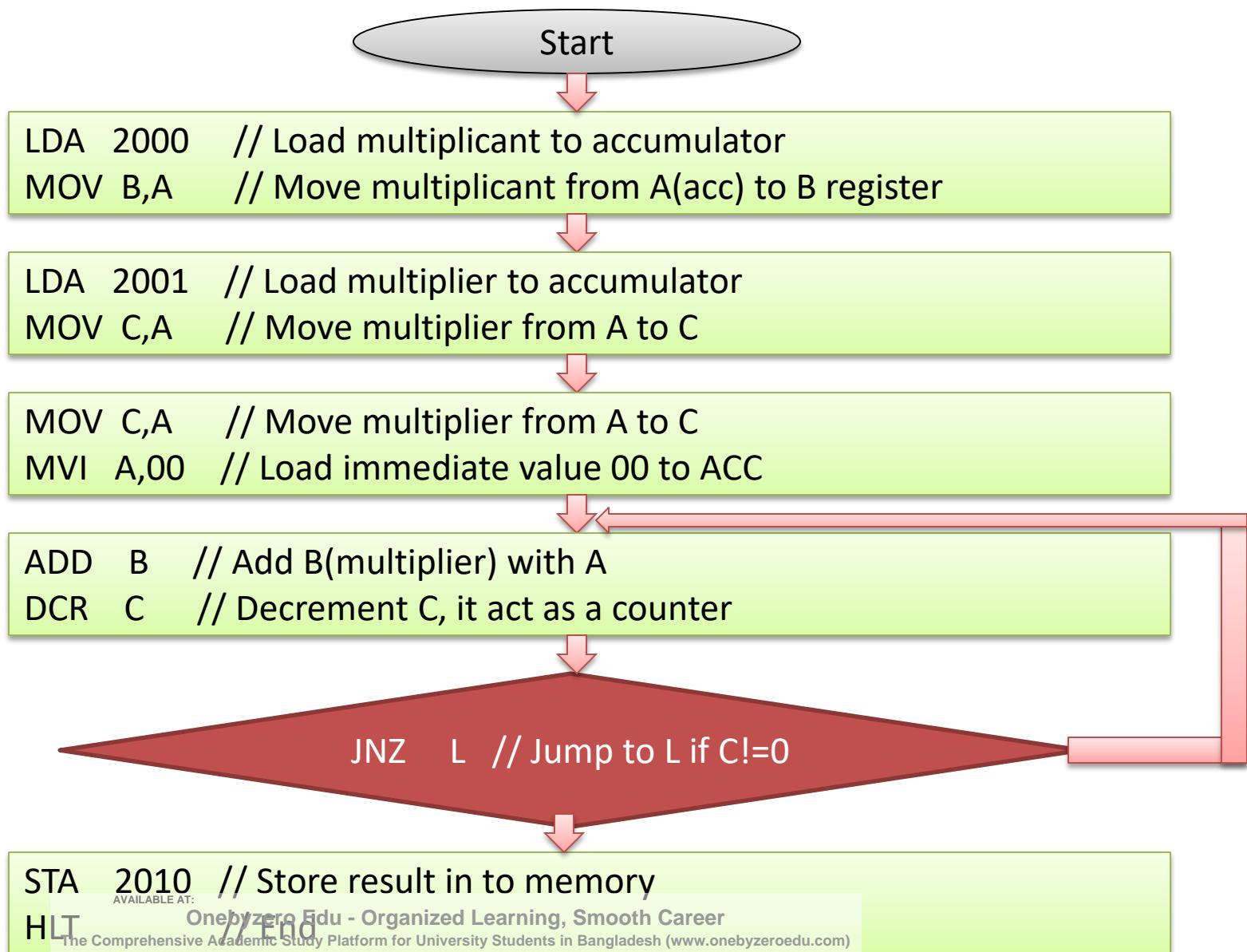

# Flowchart to multiply two number

# Code to multiply two number

```

LDA 2000 // Load multiplicand to accumulator

MOV B,A // Move multiplicand from A(acc) to B register

LDA 2001 // Load multiplier to accumulator

MOV C,A // Move multiplier from A to C

MVI A,00 // Load immediate value 00 to a

L: ADD B // Add B(multiplier) with A

DCR C // Decrement C, it act as a counter

JNZ L // Jump to L if C reaches 0

STA 2010 // Store result in to memory

HLT // End

```

# Code to get division of two number

```

LDA 3000    ; Load the dividend from memory location 3000 to accumulator (A)

MOV B, A    ; Move the dividend to register B

LDA 3001    ; Load the divisor from memory location 3001 to accumulator (A)

MOV C, A    ; Move the divisor to register C

MVI A, 00    ; Clear accumulator (A) for the quotient (A = 0)

L: CMP B    ; Compare the dividend (B) with the divisor (C)

JC END      ; If B < C (dividend < divisor), jump to END (division done)

SUB C      ; Subtract the divisor from the dividend (B)

INR A      ; Increment the accumulator (A), which holds the quotient

JMP L      ; Jump back to the label L and continue subtracting

END: STA 3010 ; Store the quotient in memory location 3010

MOV A, B    ; Move the remainder (B) to accumulator

STA 3011    ; Store the remainder in memory location 3011

HLT       ; Halt the program

```

# Factorial of a Program

LXI SP, 27FFH ; Initialize stack pointer

LDA 2200H ; Get the number

CPI 02H ; Check if number is greater than 1

JC LAST

MVI D, 00H ; Load number as a result

MOV E, A

DCR A

MOV C,A ; Load counter one less than number

CALL FACTO ; Call subroutine FACTO

**XCHG ; Get the result in HL // HL with DE**

**SHLD 2201H ; Store result in the memory // store HL at 0(16bit)**

JMP END

LAST: LXI H, 0001H ; Store result = 01

END: **SHLD 2201H**

HLT

# **Sub Routine for FACTORIAL**

FACTO:           LXI H, 0000H

MOV B, C ; Load counter

BACK:            **DAD D // double add ; HL=HL+DE**

DCR B

JNZ BACK ; Multiply by successive addition

**XCHG ; Store result in DE // HL with DE**

DCR C ; Decrement counter

CNZ FACTO ; Call subroutine FACTO

RET ; Return to main program

# 8085 Simulator & Kit

- 8085 Simulator is available

- Course website

- 8085 Kit is available in HW Lab (CS422)

- First test the program on Simulator and then go for the HW

- Sometime Kit have Driver, IDE and Assembler

AVAILABLE AT:

**Onebyzero Edu - Organized Learning, Smooth Career**

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# 8085 Architecture & Its Assembly language programming

Presented By

- Shariful Islam(20CSE008)

- Sumia Jahan Jyoti (20CSE011)

- Subrina Jahan Meem(20CSE012)

- Johra Mehjabin(20CSE0130)

- Soheb Hosen(20CSE019)

- Ashik Ghosh(20CSE032)

- Shawmitra Das Dwip(20CSE033)

- Md. Sarif(20CSE042)

- Md. Naimul Islam(20CSE045)

- Swastika Das(20CSE050)

- Sayema Siddika(20CSE51)

- Sinkia Akter(19CSE026)

Presented To

Dr. Tania Islam

Assistant Professor

Department of CSE

University of Barisal

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Outline

- 8085

- Block diagram (Data Path)

- Instruction Set of 8085

- Sample program of 8085

- Counter & Time Delay

- Stack and Sub Routine

- Assignment on 8085

- Introduction to 8086 and 30x86 architecture

- 8085 and 8086 Comparison

# 8085 Microprocessor Architecture

# The flow of an Instruction Cycle in 8085 Architecture :

- Program Counter starts program execution with the next address field .It fetches an instruction from the memory location pointed by Program Counter.

- For address fetching from the memory, multiplexed address/data bus acts as an address bus and after fetching instruction this address bus will now acts as a data bus and extract data from the specified memory location and send this data on an 8-bit internal bus. For multiplexed address/data bus Address Latch Enable(ALE) Pin is used. If ***ALE = 1 (Multiplexed bus is Address Bus otherwise it acts as Data Bus).***

- After data fetching data will go into the Instruction Register it will store data fetched from memory and now data is ready for decoding so for this Instruction decoder register is used.

# The flow of an Instruction Cycle in 8085 Architecture :

- After that timing and control signal circuit comes into the picture. *It sends control signals all over the microprocessor to tell the microprocessor whether the given instruction is for READ/WRITE and whether it is for MEMORY/I-O Device activity.*

- Hence according to timing and control signal pins, logical and arithmetic operations are performed and according to that data fetching from the different registers is done by a microprocessor, and mathematical operation is carried out by ALU. And according to operations Flag register changes dynamically.

- With the help of Serial I/O data pin(SID or SOD Pins) we can send or receive input/output to external devices .in this way execution cycle is carried out.

- ***While execution is going on if there is any interrupt detected then it will stop execution of the current process and Invoke Interrupt Service Routine (ISR) Function.*** Which will stop the current execution and do execution of the current occurred interrupt after that normal execution will be performed.

# Simple Assembly Program

MVI A, 24H // load Reg ACC with 24H

MVI B, 56H // load Reg B with 56H

ADD B // ACC=ACC+B

OUT 01H // Display ACC contents on port 01H

HALT // End the program

Result: 7A (All are in Hex)

DAA operation for Decimal Adjust A+6=10H

# Flowchart to multiply two number

# Code to multiply two number

```

LDA 2000 // Load multiplicand to accumulator

MOV B,A // Move multiplicand from A(acc) to B register

LDA 2001 // Load multiplier to accumulator

MOV C,A // Move multiplier from A to C

MVI A,00 // Load immediate value 00 to a

L: ADD B // Add B(multiplier) with A

DCR C // Decrement C, it act as a counter

JNZ L // Jump to L if C reaches 0

STA 2010 // Store result in to memory

HLT // End

```

# Delay of Instructions

- Performance/delay of each instruction

|             |                                                                                    |              |

|-------------|------------------------------------------------------------------------------------|--------------|

| MVI C, FFH  |  | 7 T-State    |

| LOOP: DCR C |   | 4 T-State    |

| JNZ LOOP    |  | 7/10 T-State |

- Performance of other INS

|           |                                                                                      |            |

|-----------|--------------------------------------------------------------------------------------|------------|

| ADD R     |     | 4 T-State  |

| ADD M     |   | 7 T-State  |

| CALL addr |  | 18 T-State |

- F=Fetch with 4 State, S=Fetch with 6 State, R=Memory Read, W=Memory Write

# Time Delay Loop

- Performance/delay of each instruction

|             |                                                                                    |              |

|-------------|------------------------------------------------------------------------------------|--------------|

| MVI C, FFH  |  | 7 T-State    |

| LOOP: DCR C |   | 4 T-State    |

| JNZ LOOP    |  | 7/10 T-State |

- Time delay in loop

$$T_L = T \times \text{Loop T-States} \times N_{10}$$

where T=System clock period

$N_{10}$ = Equiv. decimal value of count loaded to C

$$T_L = 0.5 \times 10^{-6} \times (14 \times 255) = 1.8 \text{ms} \text{ (ignore 10 T-State)}$$

# Time Delay: Nested Loop

- Performance/delay of each instruction

|              |                                                                                    |              |

|--------------|------------------------------------------------------------------------------------|--------------|

| MVI C, FFH   |  | 7 T-State    |

| MVI D, FFH   |  | 7 T-State    |

| LOOP1: DCR C |  | 4 T-State    |

| LOOP2: DCR D |  | 4 T-State    |

| JNZ LOOP2    |  | 7/10 T-State |

| JNZ LOOP1    |  | 7/10 T-State |

- Time delay in Nested loop

$$T_{NL} = N1_{10} \times T \times (L1\_TStates + L2\_TStates \times N2_{10})$$

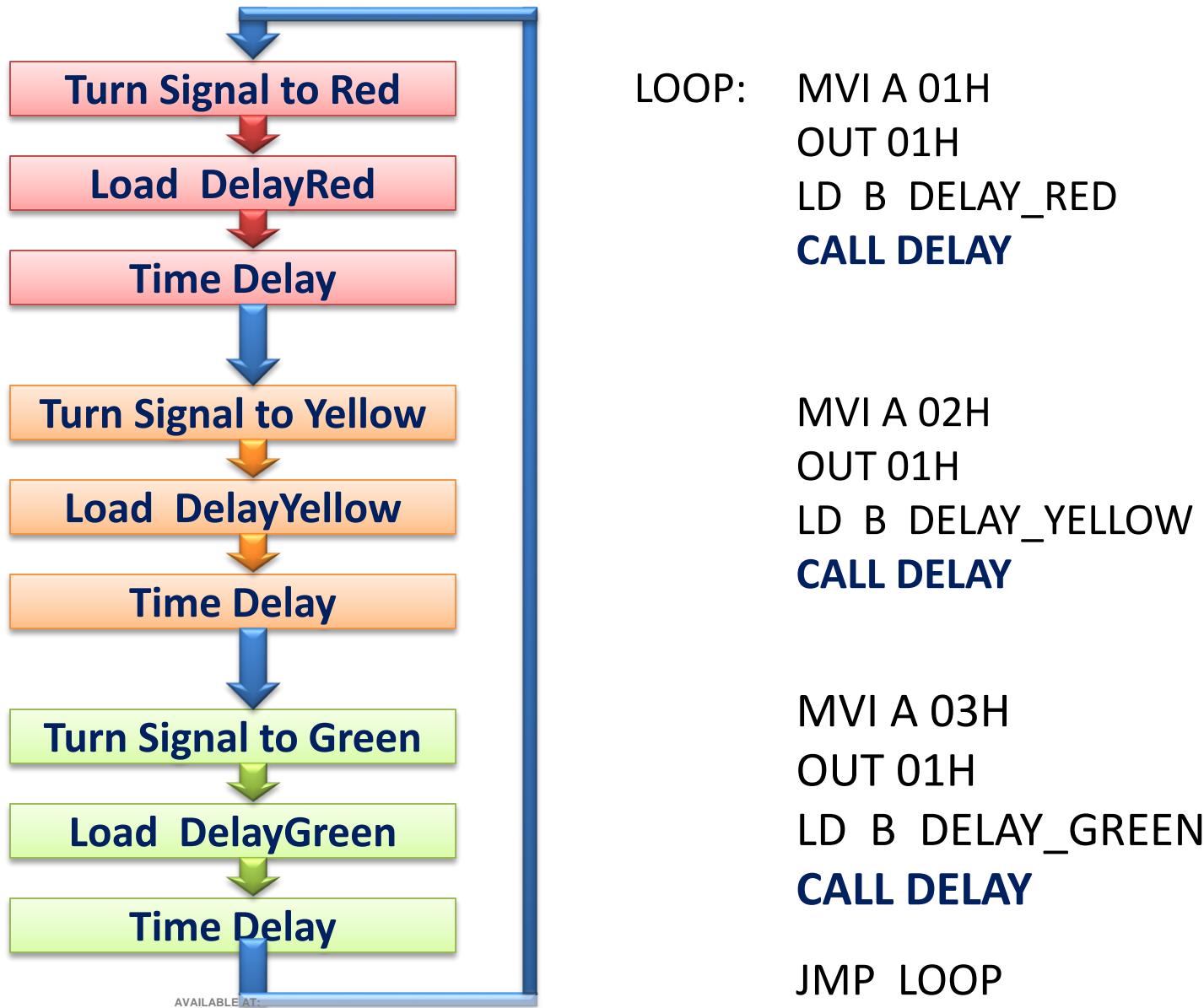

# Traffic Light Control: Counter & Delay

AVAILABLE AT:

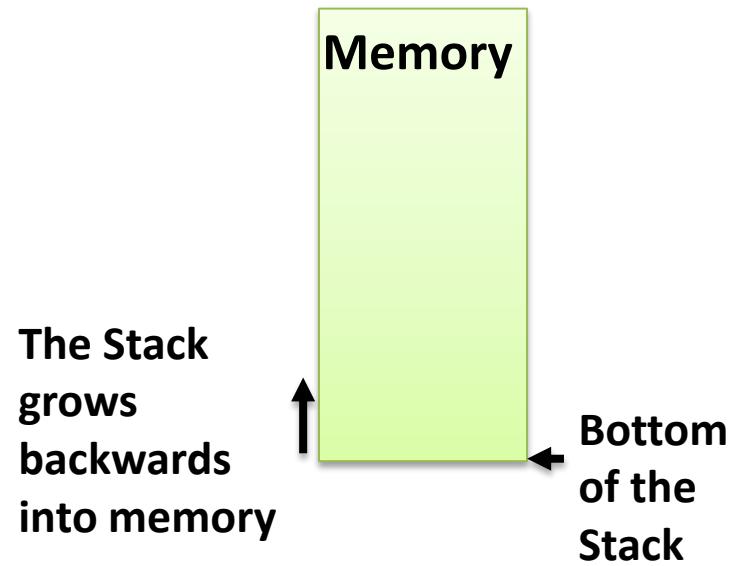

# Stack Pointer (SP) & Stack Memory

- The stack is an area of memory identified by the programmer for temporary storage of information.

- The stack is a LIFO structure.

- The stack normally grows backwards into memory.

- Programmer can defines the bottom of the stack (SP) and the stack grows up into reducing address range.

# Stack Memory

- Grows backwards into memory

- Better to place the bottom of the stack at the end of memory

- To keep it as far away from user programs as possible.

- Stack is defined by setting the SP (Stack Pointer) register.

LXI SP, FFFFH

- This sets SP to location FFFFH (end of memory for 8085).

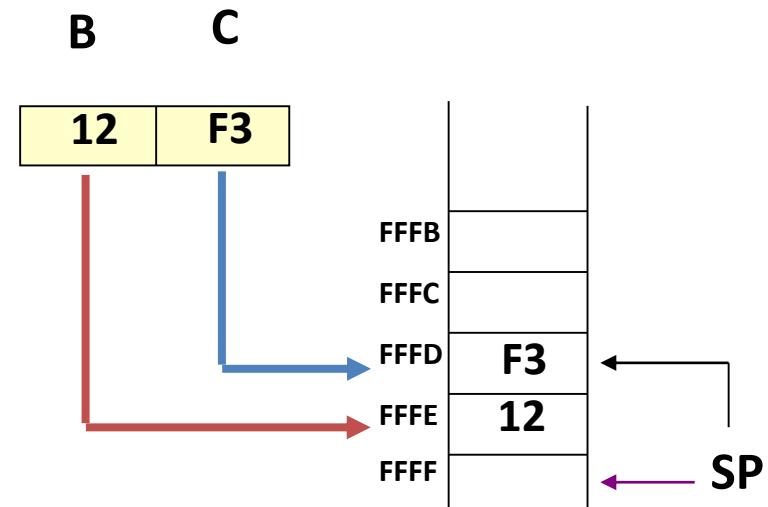

# Saving Information on the Stack

- Save information by PUSHing onto STACK

- Retrieved from STACK by POPing it off.

- PUSH and POP work with register pairs only.

- Example “PUSH B”

- Decrement SP, Copy B to 0(SP)

- Decrement SP, Copy C to 0(SP)

- Example “POP B”

- Copy 0(SP) to C, Increment SP

- Copy 0(SP) to B, Increment SP

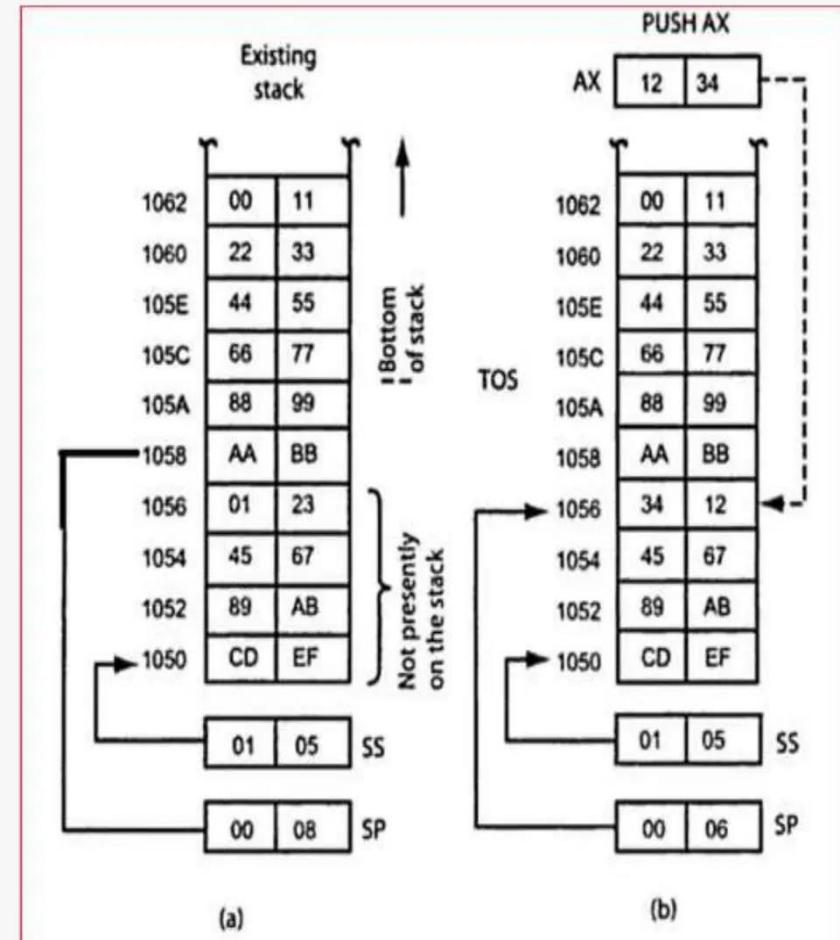

# STACK STRUCTURE OF 8086: PUSH OPERATION

AX initially contains the number 1234H.

Execution of push instruction causes the stack pointer to be decremented by two.

Therefore the next stack access is to the location corresponding to address 1056H. This location is where the value in AX is pushed.

The MSB of AX (ie, 12H) resides in memory address 1057H and LSB of AX (ie, 34H) is held in memory address 1056H

# STACK STRUCTURE OF 8086: POP OPERATION

The execution of the first instruction POP AX, causes the 8086 to read the value from the Top of the stack and put it in to AX register as 1234H

SP is incremented to give 0008H and the other read operation POP BX, causes the value BBAAH to be loaded into the BX register.

SP is incremented once more and now equals 000AH. Therefore , the new top of stack is at address 105AH

# Stack/LIFO use in CALL/RET

- Retrieve information back into its original location

- The order of PUSHs and POPs must be opposite

- 8085 recognizes one additional register pair

- PSW (Prog Status word) = ACC and Flag

**Before any routine CALL do this**

**PUSH B**

**PUSH D**

**PUSH PSW**

**After RETURN from call do this**

**POP PSW**

**POP D**

**POP B**

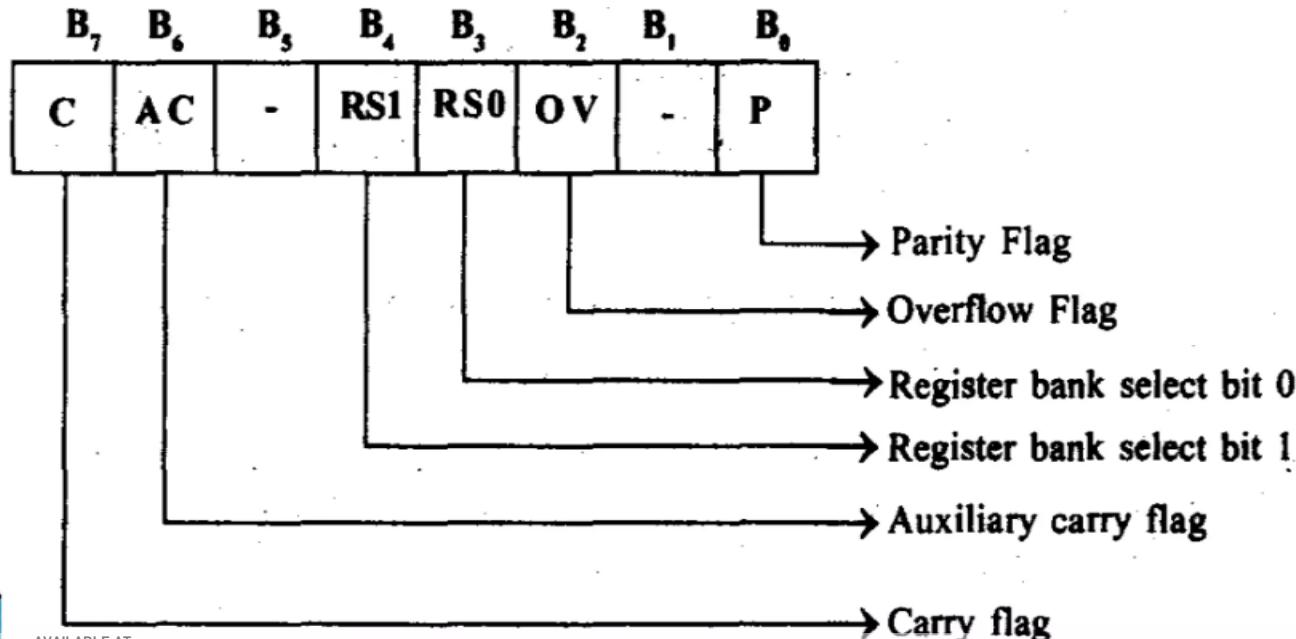

# PSW

- Program Status Word stores the processor's current condition (PSW).

- It combines accumulator A and flag register F.

- 8 bits register

## PSW IN 8051 MICROCONTROLLER

AVAILABLE AT:

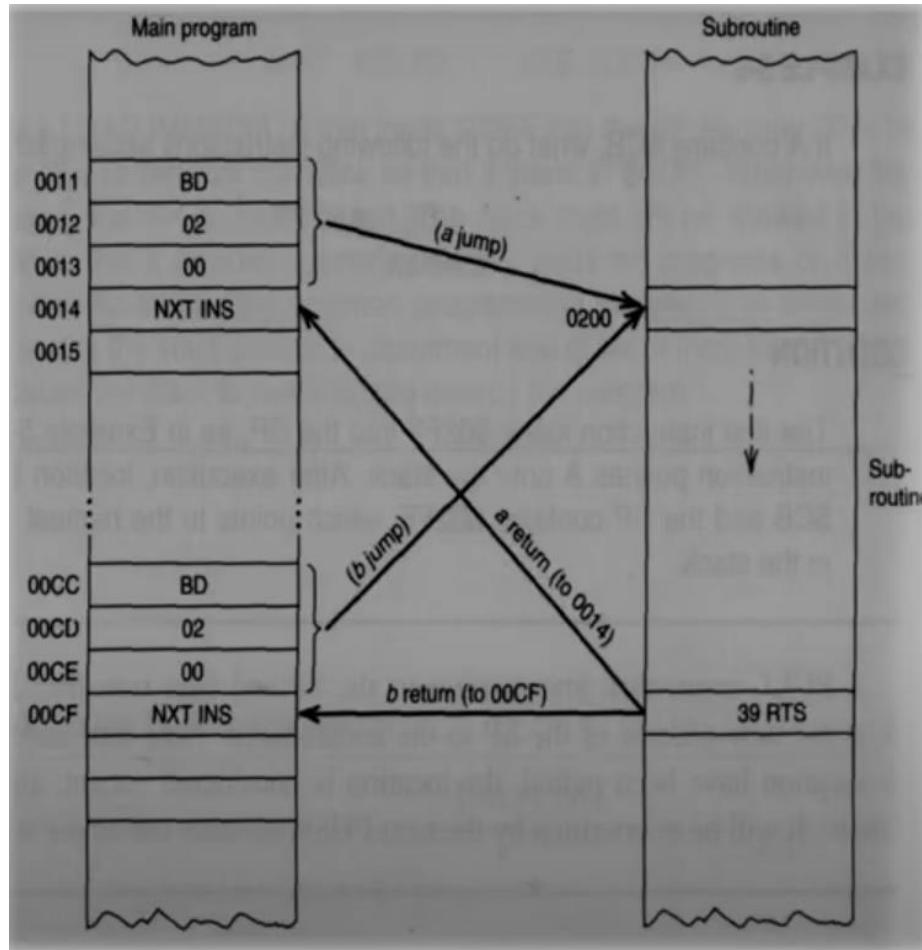

# Subroutines

- A subroutine is a group of instructions

- That is used repeatedly in different places of the program.

- Rather than repeat the same instructions several times

- It can be grouped into a subroutine and call from the different locations.

- Instructions for dealing with subroutines.

- The CALL instruction is used to redirect program execution to the subroutine.

- The RET instruction is used to return the execution to the calling routine.

# Subroutines

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

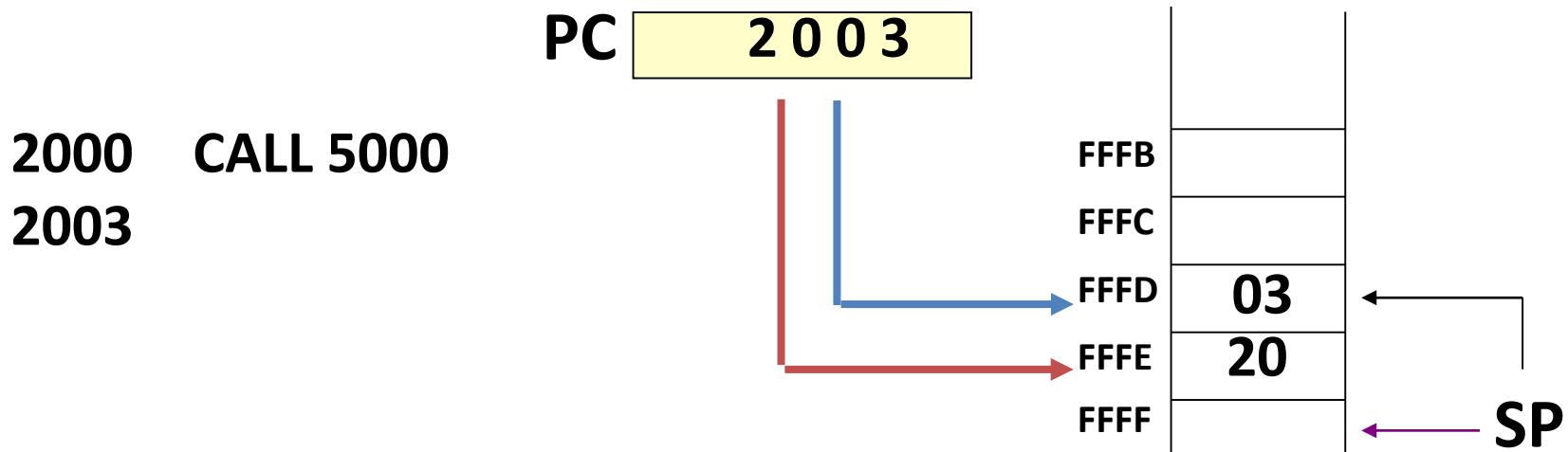

# CALL/RET Instruction

- You must set the SP correctly before using CALL

- CALL 5000H

- Push the PC value onto the stack

- Load PC with 16-bit address supplied CALL ins.

- RET : Load PC with stack top; POP PC

# CALL/RET instruction

## ❖ Procedure of Subroutine in 8085

### Program

Add Data

2000H MVI A,11H

2001H MOV A,B

⋮ ⋮

2040H CALL 2070H

2041H

2042H

2043H ADD B

2044H MOV C,B

⋮ ⋮

2060H HLT

### Subroutine

2070H LXI B, 2050H

2071H

2072H

⋮ ⋮

2080H

2081H

2082H RET

PUSH PC

PC = 2070H

POP PC

8085

SP = 1000H

Add Data

OFFEH 43H

OFFFH 20H

1000H

1001H

1002H

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Call by References

- Subroutines often manipulate data stored in registers.

- Changes made in the subroutine affect the calling program when returned.

## Managing Changes:

- Use PUSH to save register states before entering the subroutine.

- Use POP to restore register states after the subroutine completes

# Stack and LIFO in Subroutine Calls

- PUSH commands save necessary registers before subroutine execution.

- POP commands restore registers after returning from the subroutine.

Example sequence:

Before Subroutine Call:

- ✓ PUSH B // Base Register

- ✓ PUSH D // Data Register

- ✓ PUSH PSW //Program Standard Word

After Subroutine Call:

- ✓ POP PSW

- ✓ POP D

- ✓ POP B

# Assembly Language

The diagram shows a blue computer motherboard with various components like RAM, a processor, and a heatsink. Above the motherboard, there are two floating callouts. The top callout contains assembly code:

```

mov ecx, ebx

xor eax, eax

mov esp, edx

add eax, 0xff

```

The bottom callout contains binary data:

```

101001110

011100010

1001110101

```

**Assembly Language**

*[ə-'sem-blē 'laŋ-gwij]*

Low-level programming language intended to communicate directly with a computer's hardware.

Investopedia

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Factorial of a number

```

LXI SP, 27FFH // Initialize stack pointer

LDA 2200H // Get the number

CPI 02H // Check if number is greater than 1

JC LAST

MVI D, 00H // Load number as a result

MOV E, A

DCR A

MOV C,A // Load counter one less than number

CALL FACTO // Call subroutine FACTO

XCHG // Get the result in HL // HL with DE

SHLD 2201H // Store result // store HL at 0(16bit)

JMP END

LAST: LXI H, 0001H // Store result = 01

END: SHLD 2201H

HLT

```

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Factorial Number using recursion

```

C factorial.c > ⚙ main()

1  #include<stdio.h>

2  | long long int fact(long long int n)

3  {

4      //base case

5      while(n==0){

6          return 1;

7      }

8      long long int ans=fact(n-1);

9      return n*ans;

10

11 }

12 int main()

13 {

14     long long int n;

15     scanf("%lld",&n);

16     long long int x =  fact(n);

17

18     printf("%lld",x);

19     return 0;

20 }

```

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

# Sub Routine for FACTORIAL

FACTO:LXI H, 0000H

MOV B, C // Load counter

BACK: DAD D // double add ;  $HL=HL+DE$

DCR B

JNZ BACK //Multiply by successive addition

**XCHG // Store result in DE // HL with DE**

DCR C // Decrement counter

CNZ FACTO // Call subroutine FACTO

RET // Return to main program

# Assignment I

- Write and execute 8085 assembly language program to find value of  $N_{th}$  Fibonacci number (Recursive version: using recursive subroutine call)

- 16 bit can support up to  $65356 > F_{24}$

- Deadline: 12<sup>th</sup> Aug 2010, 11.55Mid night

- After deadline grading: Max 5 out of 10

- Send TXT version of program with file name RollNo.txt to [asahu@iitg.ernet.in](mailto:asahu@iitg.ernet.in) with Assignment one as subject of email

- Don't submit copied one: will get Negative marks

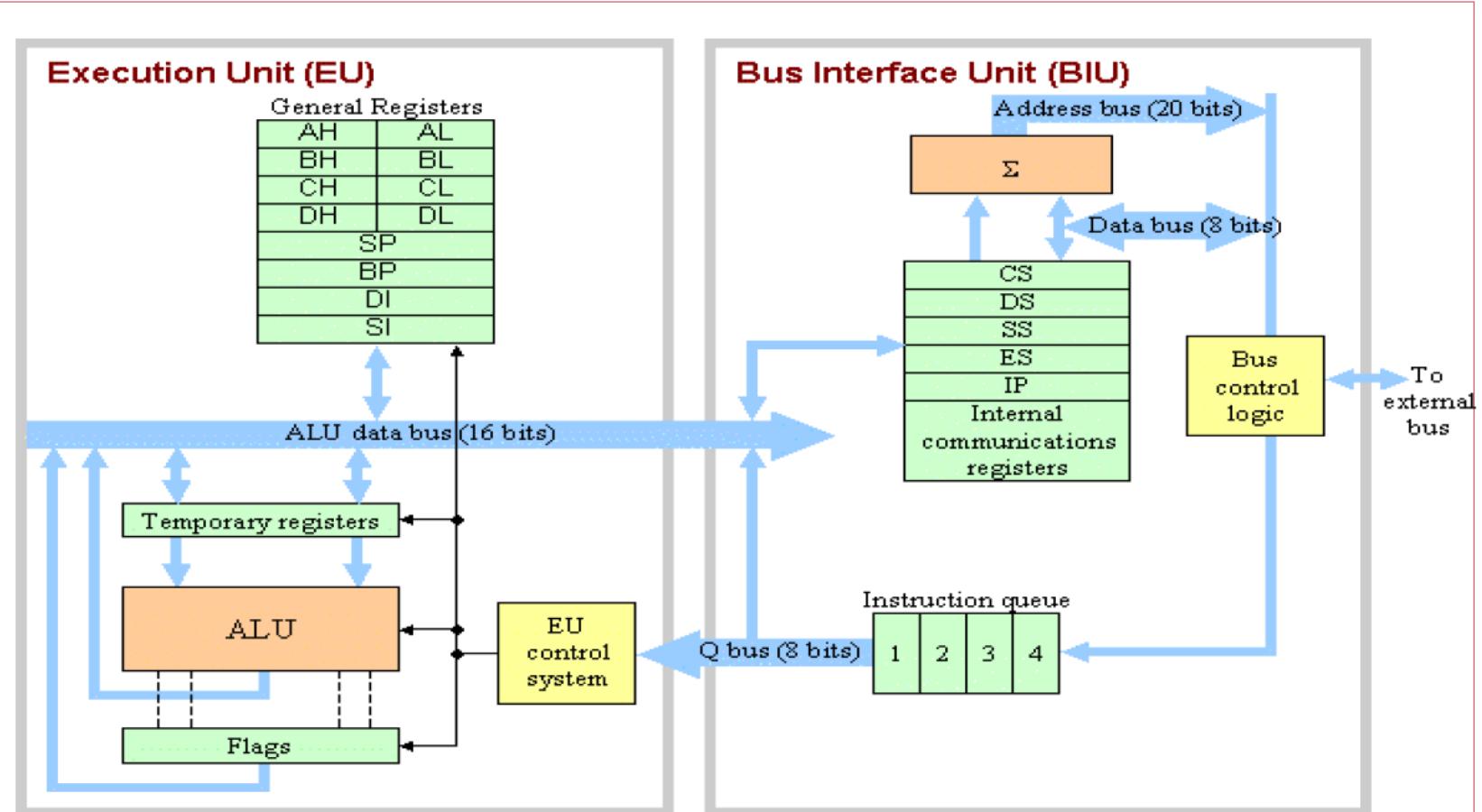

# Introduction to 8086 & i386 processor

- 16 bit Microprocessor

- All internal registers as well as internal and external data buses were 16 bits wide

- 4 Main Register, 4 Index Register, 4 Segment Register, Status Reg, Instr Ptr.

- Not compatible with 8085, but with successors

- Two Unit works in parallel:

- Bus Interface Unit (BIU)

- Execution Unit (EU)

AVAILABLE AT:

Onebyzero Edu - Organized Learning, Smooth Career

The Comprehensive Academic Study Platform for University Students in Bangladesh ([www.onebyzeroedu.com](http://www.onebyzeroedu.com))

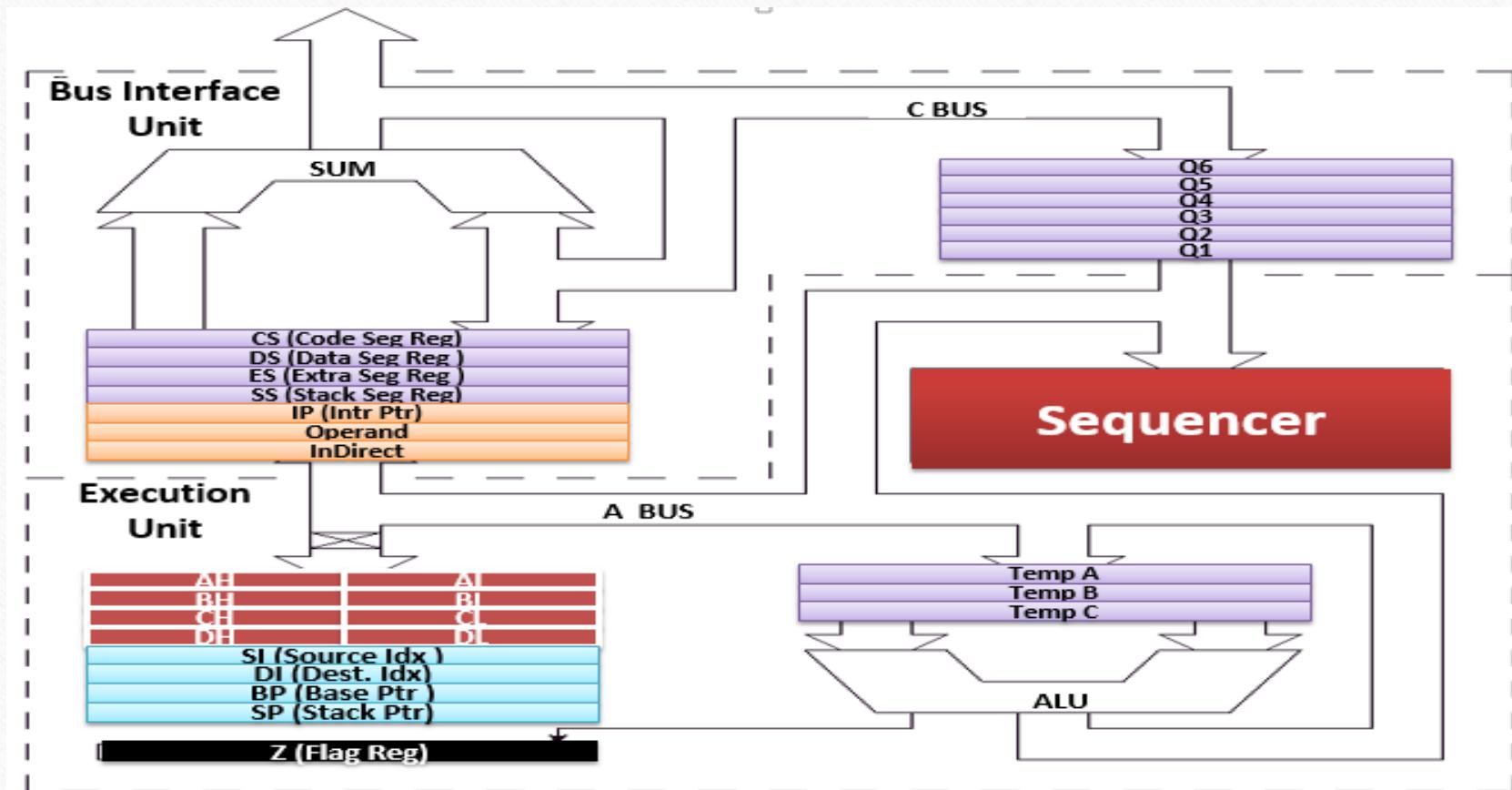

# 8086 Architecture

-- Static registers (groups of D Flip-Flops) used to hold or transfer binary data

-- Logic gate circuits designed to perform arithmetic or logical functions

-- Logic gate circuits designed to provide internal control to processor

-- Internal data buses used to pass information between components

# Internal Architecture of 8086

- The 8086 microprocessor is internally divided into two separate functional units.

- These are the Bus Interface Unit (BIU) and the Execution Unit (EU). The BIU fetches instructions, reads data from memory and ports, and writes data to memory and I/O ports. The EU executes instructions that have already been fetched by the BIU. The BIU and EU function independently.

- The BIU's instruction queue is a First-In First-out (FIFO) group of registers in which up to six bytes of instruction code are fetched from memory ahead of time.

- The BIU contains a dedicated adder, which is used to produce the 20-bit address.

- The bus control logic of the BIU generates all the bus control signals such as read and write signals for memory and I/O.

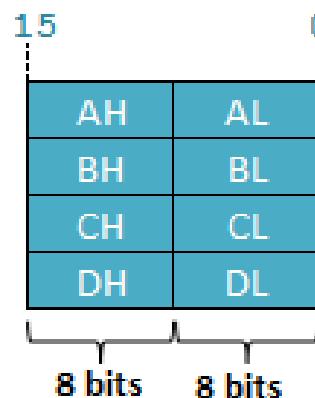

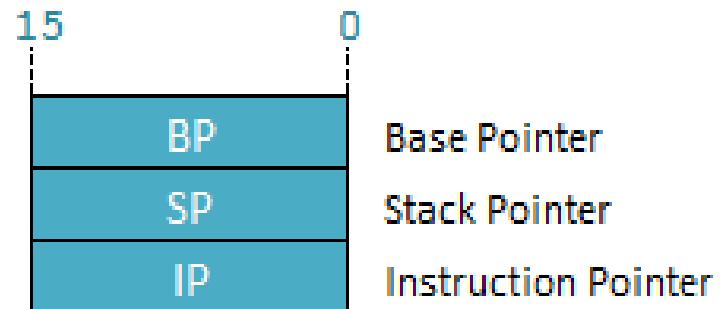

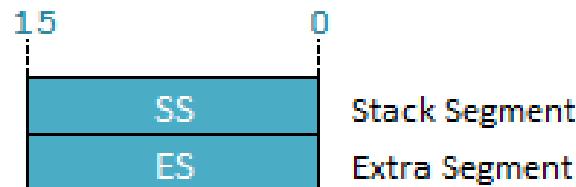

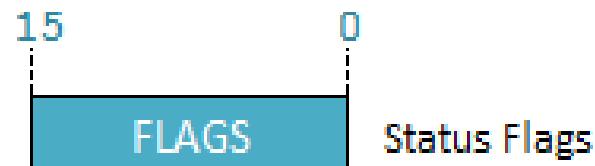

# 8086 Registers

## General Registers

AX (Primary accumulator)

BX (Base, accumulator)

CX (Counter, accumulator)

DX (Data, accumulator)

## Pointer & Index Registers

## Segment Registers

Stack Segment

Extra Segment

## Status Register

Status Flags

# General Purpose Register

- **AX - the accumulator register (divided into AH / AL):**

- Generates shortest machine code

- Arithmetic, logic and data transfer

- One number must be in AL or AX

- Multiplication & Division

- Input & Output

- **BX - the base address register (divided into BH / BL).**

- **CX - the count register (divided into CH / CL):**

- Iterative code segments using the LOOP instruction

- Repetitive operations on strings with the REP command

- Count (in CL) of bits to shift and rotate

- **DX - the data register (divided into DH / DL):**

- DX:AX concatenated into 32-bit register for some MUL and DIV operations

- Specifying ports in some IN and OUT operations

# Segment Registers

- CS - points at the segment containing the current program.

- DS - generally points at segment where variables are defined.

- ES - extra segment register, it's up to a coder to define its usage.

- SS - points at the segment containing the stack.

- IP - the instruction pointer:

- Always points to next instruction to be executed

# Pointer and Index Registers

- **SI - source index register:**

- Can be used for pointer addressing of data

- Used as source in some string processing instructions

- **DI - destination index register:**

- Can be used for pointer addressing of data

- Used as destination in some string processing instructions

- **BP - base pointer:**

- Primarily used to access parameters passed via the stack

- **SP - stack pointer:**

- Always points to top item on the stack

- An empty stack will have SP = FFFEh

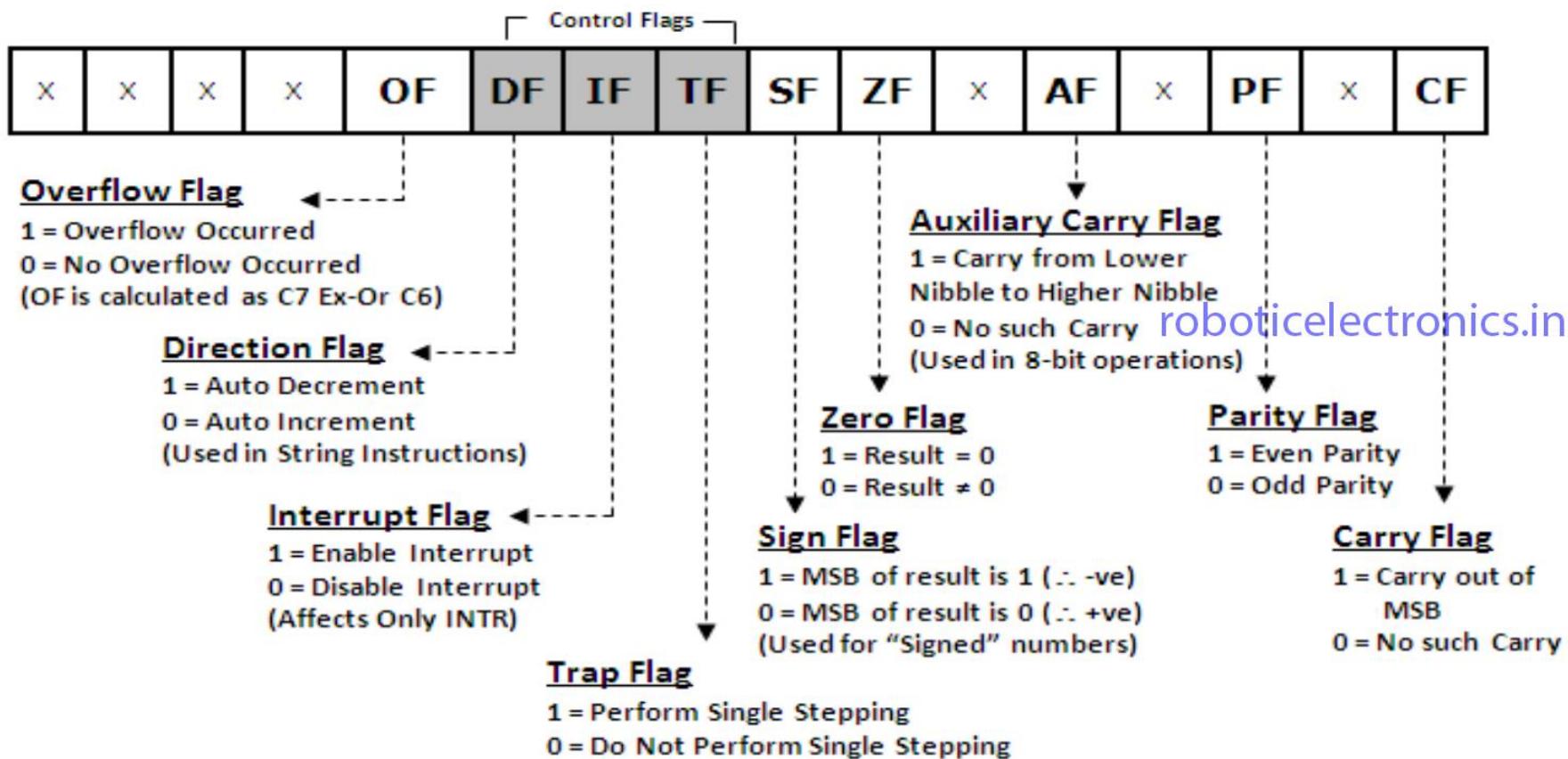

# Flag Register

# 8085 VS 8086

| <b>8085 Microprocessor</b>                                                                                 | <b>8086 Microprocessor</b>                                                                                                                       |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• Is an 8 Bit Microprocessor</li></ul>                               | <ul style="list-style-type: none"><li>• Is a 16 Bit Microprocessor</li></ul>                                                                     |

| <ul style="list-style-type: none"><li>• Has 8 bit data bus</li></ul>                                       | <ul style="list-style-type: none"><li>• Has 16 bit data bus</li></ul>                                                                            |

| <ul style="list-style-type: none"><li>• Has 16 bit address line</li></ul>                                  | <ul style="list-style-type: none"><li>• Has 20 bit address line</li></ul>                                                                        |

| <ul style="list-style-type: none"><li>• Only 64kB of memory can be used (<math>2^{16}</math>)</li></ul>    | <ul style="list-style-type: none"><li>• 1MB of memory can be used (<math>2^{20}</math>)</li></ul>                                                |

| <ul style="list-style-type: none"><li>• Has 5 Flags (Carry, Parity, Sign, Zero, Auxillary Carry)</li></ul> | <ul style="list-style-type: none"><li>• Has 9 Flags (Carry, Parity, Sign, Zero, Auxillary Carry, Direction, Trap, Interrupt, Overflow)</li></ul> |

| <ul style="list-style-type: none"><li>• It is Accumulator based processor</li></ul>                        | <ul style="list-style-type: none"><li>• It is General Purpose Register Based Processor</li></ul>                                                 |

| <ul style="list-style-type: none"><li>• It has no MIN mode or MAX mode</li></ul>                           | <ul style="list-style-type: none"><li>• It can operate in any one of MIN or MAX Mode</li></ul>                                                   |

| <ul style="list-style-type: none"><li>• Does not support Pipelining</li></ul>                              | <ul style="list-style-type: none"><li>• Supports Pipelining</li></ul>                                                                            |

| <ul style="list-style-type: none"><li>• Does not support Memory Segmentation</li></ul>                     | <ul style="list-style-type: none"><li>• Supports Memory Segmentation</li></ul>                                                                   |

| <ul style="list-style-type: none"><li>• Has 6500 transistors</li></ul>                                     | <ul style="list-style-type: none"><li>• Has 29000 transistors</li></ul>                                                                          |

# Thanks

AVAILABLE AT: