# INTEL 80186/80286/80386

This chapter describes the internal architecture, addressing modes, instruction set, and I/O techniques associated with the 80186, 80286, and 80386 microprocessors. Interfacing capabilities to typical memory and I/O chips are also included. Finally, virtual memory concepts associated with the 80286 and 80386 are covered.

## 4.1 Intel 80186 and 80286

This section covers the two enhanced versions of the 8086 microprocessor: Intel 80186 and 80286. The Intel 80186 includes the Intel 8086 and six separate functional units in a single chip, while the 80286 has integrated memory protection and management into the basic 8086 architecture.

### 4.1.1 Intel 80186

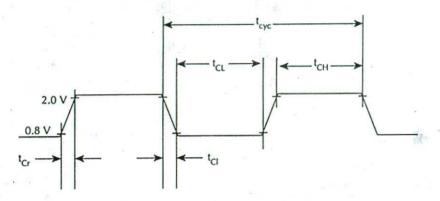

The Intel 80186 family is fabricated using HMOS technology and contains two microprocessors: Intel 80186 and 80188. The only difference between them is that the 80186 has a 16-bit data bus, while the 80188 includes an 8-bit data bus. The 80186 is packaged in a 68-pin leadless package. The 80186 can be operated at three different clock speeds: 8 MHz, 10 MHz, 12.5 MHz, and other frequencies. The 80C186 and 80C188 are the Low-Power (HCMOS) versions of the 80186 and 80188 respectively. The 80C186 and the 80186 can be operated at the same frequencies while the 80C188, like the 80188 can be operated at 8- or 10-MHz. The 80186 can directly address one megabyte of memory. It contains the 8086 microprocessor and several additional functional units. The major on-chip circuits include a clock generator, two independent DMA channels, a programmable interrupt controller, three programmable 16-bit timers, and a chip select unit.

The 80186 provides double the performance of the standard 8086. The 80186 includes 10 new instructions beyond the 8086. The 80186 is completely object code compatible with the 8086. It contains all the 8086 registers and generates the 20-bit physical address from a 16-bit segment register and a 16-bit offset in the same way as the 8086. The 80186 does not have the 8086's MN/MX pin. The 80186 has enough pins to generate the minimum mode-type pins. S0-S3 status signals can be connected to external bus controller chips such as 8288 for generating the maximum mode type signals. Like the 8086, the 80186 fetches the first instruction from physical address FFFF0H upon hardware reset.

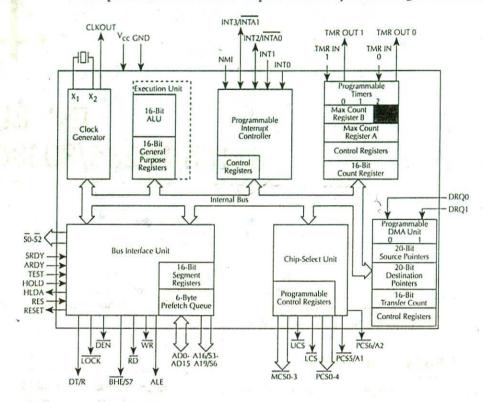

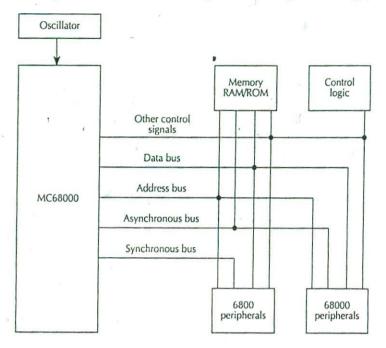

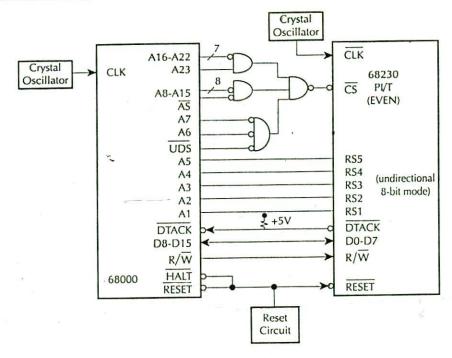

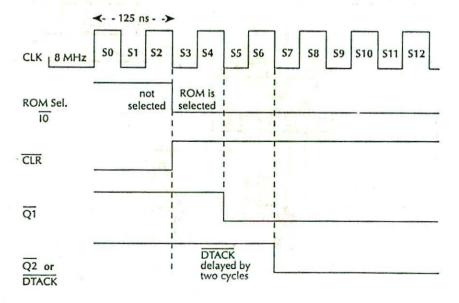

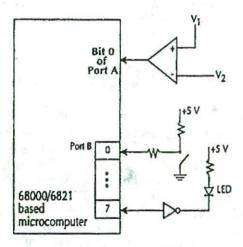

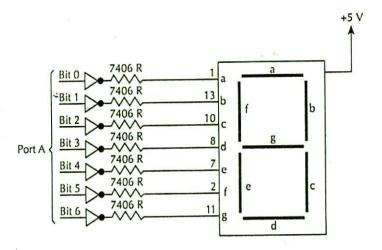

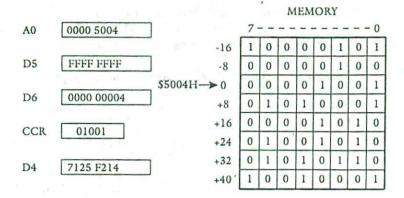

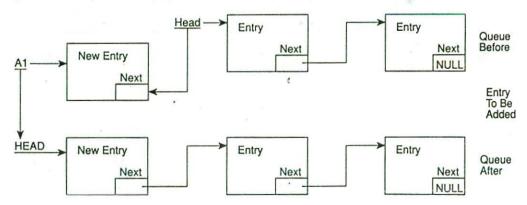

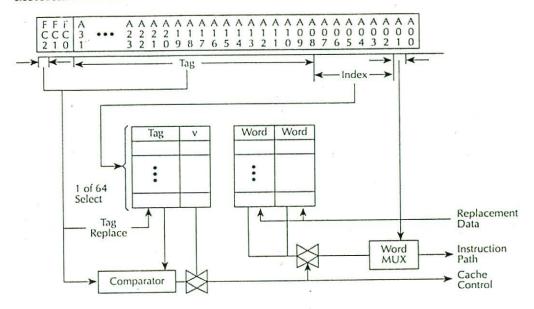

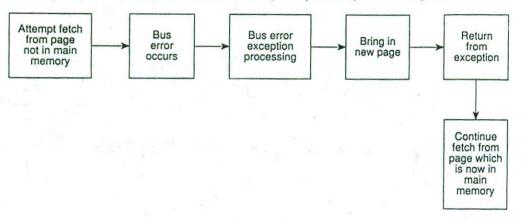

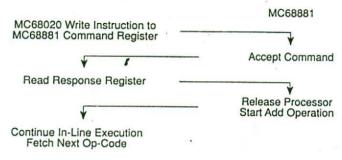

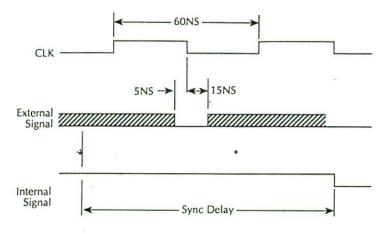

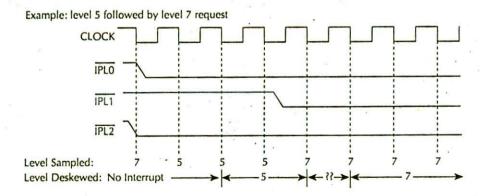

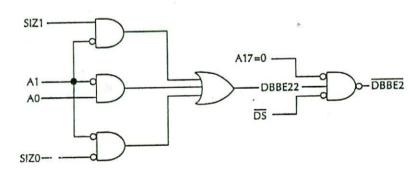

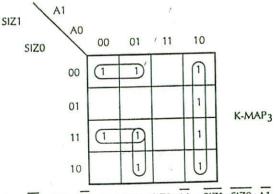

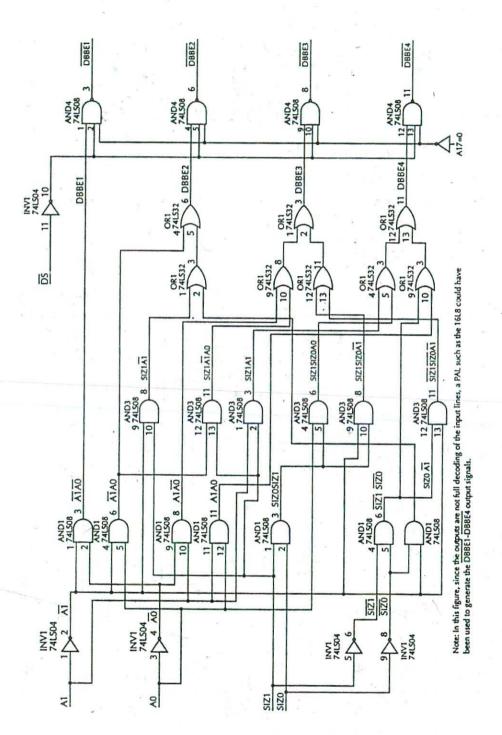

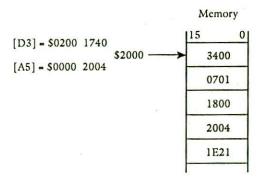

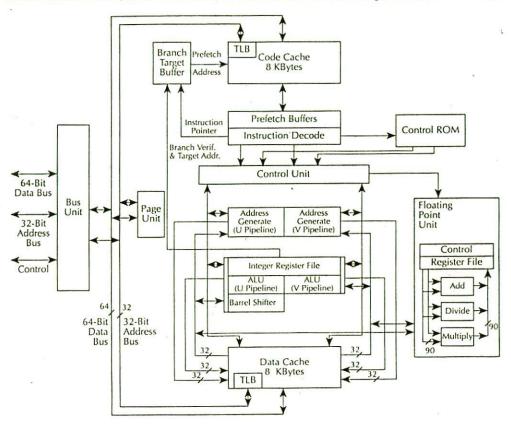

FIGURE 4.1 80186 functional block diagram.

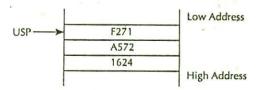

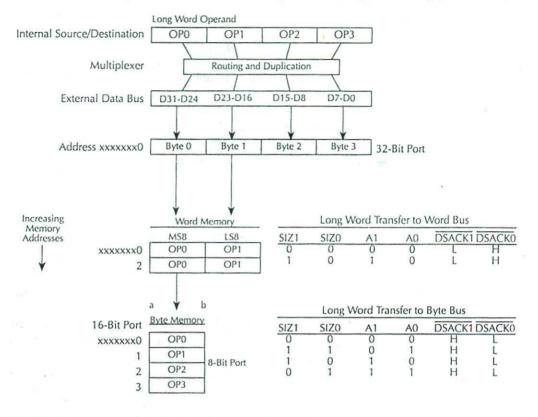

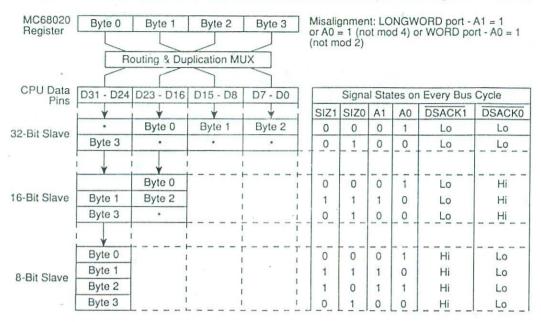

Figure 4.1 shows the 80186 functional block diagram. The DMA unit provides two DMA request input signals, DRQ0 and DRQ1. One of these input signals can be used by external devices such as disk controller to request a data transfer between the memory and disk via direct memory access technique. Each 80186 DMA channel contains two 20-bit registers and a 16-bit counter. One of the 20-bit registers holds the destination address of the DMA transfers while the 16-bit counter stores the number of words or bytes to be transferred. DMA transfers can take place between memory and I/O or from memory to memory or from I/O to I/O. The DMA channels may be programmed such that one channel has priority over the other. DMA transfers will take place whenever the ST/STOP bit in the control register is set to one.

The 80186 contains three independent 16-bit timers/counters namely counter 0, 1, and 2. Counters 0 and 1 can be programmed to count external events. The inputs and outputs of these two counters are available on the 80186 pins. The third timer, counter 2, is not connected to any external pins. This timer only counts the 80186 clock cycles. Counter 2 is decremented every four 80186 clocks. One can connect the output of counter 2 to a DMA unit or to an interrupt input or to the input of counter 1 and/or 0 by setting or clearing the appropriate bits in a control word. Counter 2 can, therefore, be used to interrupt the 80186 after a programmed amount of time or to provide a pulse to the DMA unit after a specific amount of time.

The priorities of the four interrupt pins, INT0, INT1, INT2/ INTA0 and INT3/ INTA1 are programmable. If these four interrupt inputs are programmed in their internal mode, then the activation of one of them by an external signal will cause the 80186 to push the return address on the stack and vector directly to the interrupt address vector for that interrupt. The INT2/ INTA0 and INT3/ INTA1 pins have dual functions. They can be programmed as interrupt inputs or as interrupt acknowledge output signals (INTA0 for INT0 and INTA1 for INT1). These interrupt pins can be used to connect the 80186 to an external priority interrupt controller such as the 8259A. For example, suppose that the interrupt request line from an

external 8259A is connected to the 80186 INT1 input pin and the 80186 INT3/ INTA1 pin is connected to the 8259A interrupt acknowledge input pin. When the 8259A receives an interrupt request, it activates the 80186 INT1 pin. In response, the 80186 sends the interrupt acknowledge signal via its INT3/ INTA1 pin. The 8259A then places the desired interrupt type code on the 80186 data bus. The 80186 obtains the CS and IP values based on the type code and branches to the service routine.

The 80186 interrupt controller allows the 80186 to receive interrupts from internal or external sources. Internal interrupt sources (timers and DMA channels) can be disabled by their own control registers or by mask bits within the interrupt controller. The 80186 is provided with five dedicated pins for external interrupts. These pins are NMI, INT0, INT1, INT2/ INTA0, and INT3/ INTA1. NMI is the only nonmaskable interrupt.

In the master mode, the interrupt controller provides three modes of operation. These are fully nested mode, cascade mode, and special fully nested mode. In the fully nested mode, all four maskable interrupt pins are used as direct interrupt requests. The interrupt vectors are obtained by the 80186 internally.

Upon acceptance of an interrupt (hardware, INT instructions, or instruction exceptions such as divide by 0), the 80186 pushes CS, IP, and the status word onto the stack just like the 8086. Also, similar to the 8086, an interrupt pointer table with 256 entries provides interrupt address vectors (IP and CS) for each interrupt type. This type identifies the appropriate table entry. Nonmaskable interrupts use an internally supplied type, while the types for maskable interrupts are provided by the user via external hardware. The types for INT instructions and instruction exceptions are generated internally by the 80186.

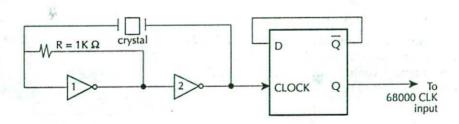

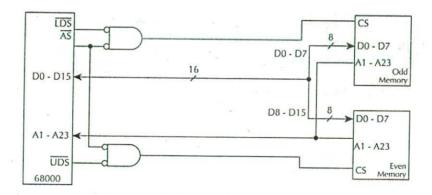

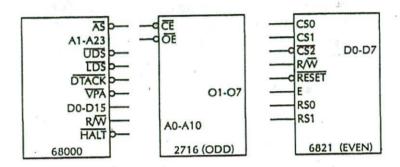

The 80186 includes an on-chip clock generator/crystal oscillator circuit. Like the 8085, a crystal connected at the 80186 X1 X2 pins is divided by 2 internally. The built-in chip select unit is an address decoder. This unit can be programmed to generate six memory chip selects (LCS, UCS, and MCS0 - 3 pins) and seven I/O or peripheral chip selects (PCS0-4, PCS5/ A1, and PCS6/A2 pins). This unit can be programmed to generate an active low chip select when a memory or port address in a particular range is sent out. For example, the 80186 outputs low on the LCS (lower chip select) pin when it accesses an address between 00000H and a higher address (in the range of 1K to 256K) programmable by the user via a control word. On the other hand, the 80186 outputs low on the UCS (upper chip select) pin when it accesses an address between a user programmable lower address (by placing some bits in a control word via an instruction) and upper fixed address FFFFFH. The four middle chip select pins (MCSO-3) are activated low by the 80186 when it accesses an address in the mid range. Both the starting address and the size of the four blocks can be specified via the control word. The specified size of blocks can be from 2K to 128K. The memory areas assigned to different chip selects must not overlap; otherwise, two chip selects will be asserted and bus contention will occur. The built-in decoder allows the 80186 to select large memory blocks. For peripheral chip selects, a base address can be programmed via a control word. The 80186 sends low on the PCS0 when it accesses a port address located in a block from this base address to up to 128 bytes. The 80186 sends low on the other chip selects PCS1-6 when one of six contiguous 128byte blocks above the block for PCS0 is selected. Like the 8086, memory for the 80186 is set up as odd (BHE = 0) and even (A0 = 0) memory banks.

The 80186 provides eight addressing modes. These include register, immediate, direct, register indirect (SI, DI, BX, or BP), based (BX or BP), indexed (SI or DI), based indexed, and

based indexed with displacement modes.

Typical data types provided by the 80186 include signed integer, ordinal (unsigned binary number), pointer, string, ASCII, unpacked/packed BCD, and floating point. The 80186 instruction set is divided into seven types. These are data transfer, arithmetic, shift/rotate, string, control transfer, high level instructions (for example, the BOUND instruction detects values outside prescribed range), and processor control. As mentioned before, the 80186 includes 10 new instructions beyond the 8086. These 10 additional instructions are listed below:

#### Data Transfer

**PUSHA** Push all registers onto stack POPA Pop all registers from stack

PUSH immediate Push immediate numbers onto stack

#### Arithmetic

IMUL destination register, source, immediate data means immediate data\*source → destination register.

#### Logical

SHIFT/ROTATE destination, immediate data or CL shifts/rotates register or memory contents by the number of times specified in immediate data or by the contents of CL.

#### String Instructions

INSB or INSW Input string byte or string word OUTSB or OUTSW Output string byte or string word

#### High Level Instructions

ENTER Format stack for procedure entry LEAVE Restore stack for procedure exit BOUND Detect values outside predefined range

Let us explain some of these instructions.

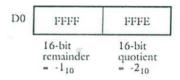

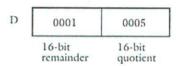

- IMUL destination register, source, immediate data. This is a signed multiplication. This instruction multiplies signed 8- or 16-bit immediate data with 8- or 16-bit data in a specified source register or memory location and places the result in a general-purpose destination register. As an example, IMUL DX, CX, -3 multiplies the contents of CX by -3 and places the lower 16-bit result in DX. Note that the immediate 8-bit data of -3 are sign extended to 16-bit prior to multiplication. A 32-bit result is obtained but only the lower 16-bit is saved by this instruction.

- ROL/ROR/SAL/SAR destination, immediate data or CL. Shift count can be specified by immediate data (one) or in CL up to a maximum of 3210.

- INSB DX or INSW DX respectively inputs a byte or a word from a port addressed by DX to a memory location in ES pointed to by DI. If DF = 0, DI will automatically be incremented (by 1 for byte and 2 for word) after execution of this instruction. On the other hand, if DF = 1, DI is automatically decremented (by 1 for byte and 2 for word) after execution of this instruction. The instructions INSB for byte and INSW for word are used. A typical example of inputting 50 bytes of I/O data via a port into a memory location is given below (assume ES is already initialized):

```

STD

Set DF to 1.

LEA DI, ADDR

Initialize DI.

MOV DX,

0E124H

Load port address.

MOV CX, 50

Initialize count.

REP INSB DX

Input port until CX = 0.

Halt.

STOP

JMP STOP

```

- OUTSB DX or OUTSW DX respectively provides outputting to a port addressed by DX from a source string in DS with offset in SI.

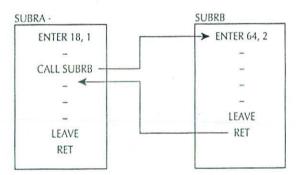

- The ENTER instruction is used at the beginning of an assembly language subroutine which is to be called by a high level language program such as Pascal. The main purpose of ENTER is to reserve space on the stack for variables used in the subroutine.

The ENTER instruction has two immediate operands:

#### ENTER imm16, imm8

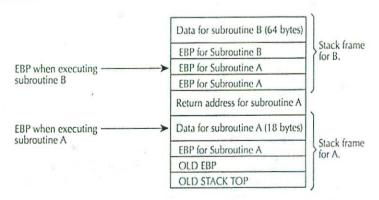

The first operand imm16 specifies the total memory area allocated to the local variables, which is 16 bits wide (0 to 64K bytes). The second operand imm8, on the other hand, is 8 bits wide and specifies the number of nested subroutines.

For the main subroutine, imm8 = 0. Note that nested subroutines mean a subroutine calling another subroutine. For example, if there are three subroutines SUB1, SUB2, and SUB3 such that the main program M calls SUB1, SUB1 calls SUB2 and SUB2 calls SUB3, then imm8 = 0 for SUB1, 1 for SUB2, and 2 for SUB3. ENTER can be used to allocate temporary stack space for local variables for each subroutine.

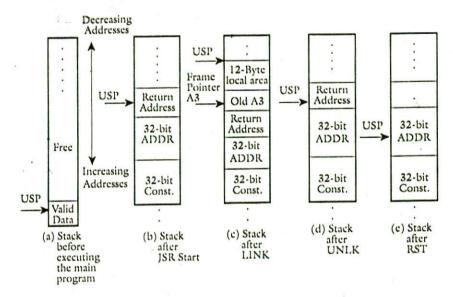

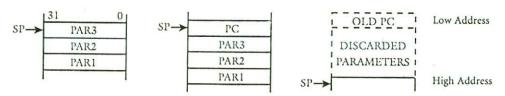

In the second operand, if imm8 = 0, the ENTER instruction pushes the frame printer BP onto the stack. ENTER then subtracts the first operand imm16 from the stack pointer and sets the frame pointer, BP, to the current stack pointer value.

The LEAVE instruction is used at the end of each subroutine (usually before the RET instruction). The LEAVE does not have any operand. The LEAVE instruction should be used with the ENTER instruction. The ENTER allocates space in stack for variables used in the subroutine, while the LEAVE instruction deallocates this space and ensures that SP and BP have the original values that they had prior to execution of the ENTER. The RET instruction then returns to the appropriate address in the main program.

As an example of application of ENTER and LEAVE instructions, suppose that a subroutine requires 16 bytes of stack for local variables. The instructions ENTER 16, 0 at the subroutine's entry point and a LEAVE before the RET instruction will accomplish this. The 16 local bytes may be accessed.

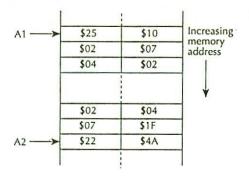

When the 80186 accesses an array, the BOUND instruction can be used to ensure that data outside the array are not accessed. When the BOUND is executed, the 80186 compares the content of a general-purpose register (initialized by the user with the offset of the array element currently being accessed) with the lower and upper bounds of the array (loaded by the user prior to BOUND). The format for BOUND is BOUND reg16, memory32. The first operand is the register containing the array index and the second operand is a memory location containing the array bounds. If the index value violates the array bounds, an exception (maskable interrupt 5) takes place. A service routine can be executed by the user to indicate that the array element being accessed is out of bounds. As an example, consider BOUND SI, ADDR. The lower bound of the array is contained in address ADDR and the upper bound is in address ADDR + 2. Both bounds are 16 bits wide. For a valid access content of SI must be greater than or equal to the content of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the contents of the memory location with offset ADDR and less than or equal to the conte

The BOUND instruction is normally placed following the computation of an offset value to ensure that the limits of the array boundaries are not violated. This permits checking whether or not the offset of an array being accessed is within the boundaries when the based addressing mode is used to access an element in the array. For example, the instruction segment shown below will allow accessing of an array with base address in BX and array length of 50<sub>10</sub> bytes:

MOV DS:ADDR, 1000; MOV DS:ADDR+2, 1049; BOUND BX, ADDR; MOV CL, [BX];

In the above, it is assumed that the offset of the lowest array element is 1000. With an array length of 50, the offset of the highest array element is 1049. It is assumed that BX contains the

offset of the array element currently being worked on. The BOUND instruction checks whether the contents of BX is between 1000 and 1049. If it is, the MOV instruction accesses the desired array element into CL; otherwise type 5 interrupt is generated.

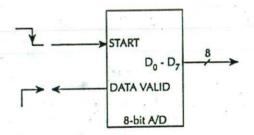

The 80186/80188 is used in embedded control. In these applications, the microcomputer performs a dedicated control function. Embedded control applications are divided into two types. These are event control and data control.

In embedded control applications involving event control, the microprocessor initiates a timed sequence of events. An example of such an application is the industrial process control.

In embedded control applications involving data control, the microprocessor transfers volumes of data to be processed from secondary memory such as disk to main memory.

The 80186/80188 is, therefore, highly integrated to satisfy the requirements of data control applications. The 80186/80188 is also provided with added features such as string I/O instructions and DMA channels to better handle fast movement of data.

#### 4.1.2 Intel 80286

The Intel 80286 is a high-performance 16-bit microprocessor with on-chip memory protection capabilities primarily designed for multiuser/multitasking systems. The IBM PC/AT and its clones capable of multitasking operations use the 80286 as their CPU. The 80286 can address 16 megabytes (2<sup>24</sup>) of physical memory and 1 gigabyte (2<sup>30</sup>) of virtual memory per task. The 80286 can be operated at several different clock speeds. These are 8 MHz (80286-4), 10 MHz (80286-6), 12.5 MHz, 16.67 MHz, and 20 MHz (80286).

The 80286 has two modes of operations. These are real address mode and protected virtual address mode (PVAM). In the real address mode, the 80286 is object code compatible with the Intel 8086/8088/80186/80188. In protected virtual address mode, the 80286 is source code compatible with the iAPX 86/88 family and may require some software modification to use virtual address features of the 80286. Note that the protected virtual address mode is not used by PCDOS.

The 80286 includes special instructions to support operating systems. For example, one instruction can end a current task execution, save its state, switch to a new task, load its state, and begin executing the new task.

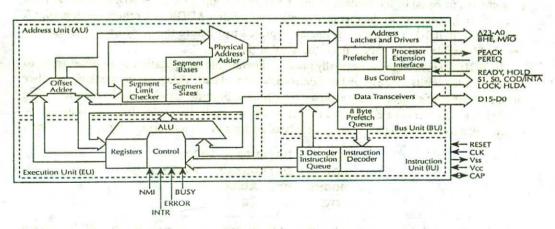

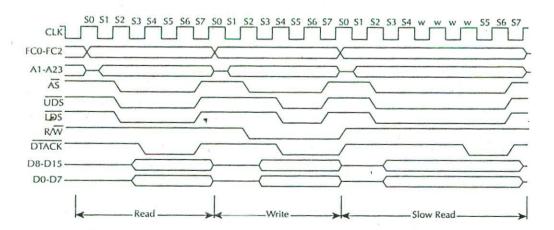

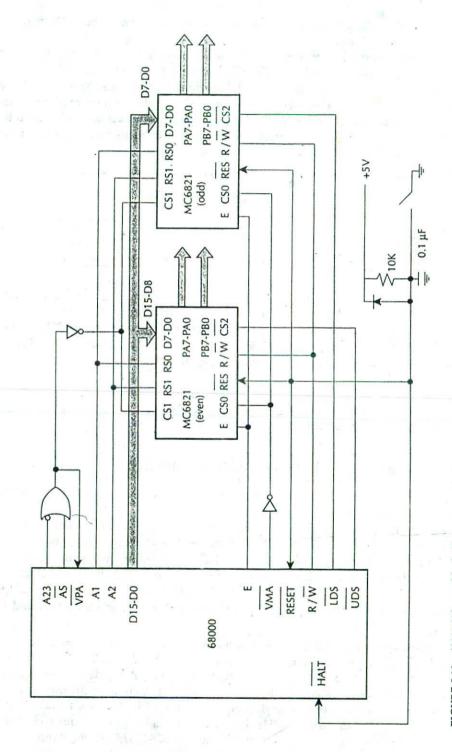

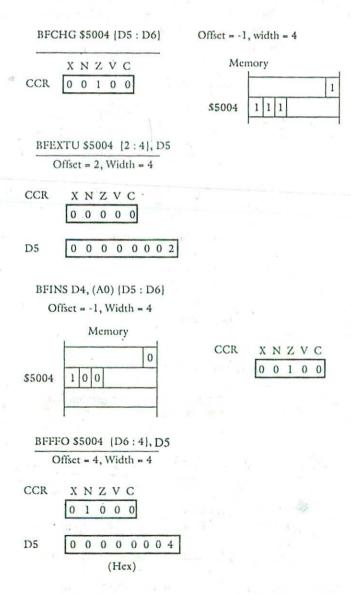

The 80286's performance is up to six times faster than the standard 5-MHz 8086. The 80286 is housed in a 68-pin leadless flat package. Figure 4.2 shows a functional diagram of the 80286. It contains four separate processing units. These are the Bus Unit (BU), the Instruction Unit (IU), the Address Unit (AU), and the Execution Unit (EU). The BU provides all memory and I/O read and write operations. The BU also performs data transfer between the 80286 and

FIGURE 4.2 80286 internal block diagram.

coprocessors such as the 80287. The prefetcher in the BU prefetches instructions of up to 6 bytes and places them in a queue.

The Instruction Unit (IU) translates or decodes up to 3 prefetched instructions and places

them in a queue for execution by the execution unit.

The Execution Unit (EU) executes instructions from the IU sequentially. The EU contains a 16-bit ALU, an 8086 flag register, general-purpose registers, pointer registers, index registers, and one 16-bit additional register called the machine status word (MSW) register. The lower four bits of the MSW are used. One bit places the 80286 into PVAM mode while the other three bits control the processor extension (coprocessor) interface. The LMSW and SMSW instructions can load and store MSW in real address mode.

The Address Unit (AU) calculates a 20-bit physical address based on the 16-bit contents of a segment register and a 16-bit offset just like the 8086. In this mode, the 80286 addresses one megabyte of physical memory. The 80286 has 24 address pins. However, in the real address mode, pins A23-A20 are ignored and A19-A0 pins are used. In the protected virtual address mode (PVAM), the AU operates as a memory management unit (MMU) and utilizes all 24 address lines to provide 16 megabytes of physical memory. The BU outputs memory or I/O addresses to devices connected to the 80286 after receiving them from the AU.

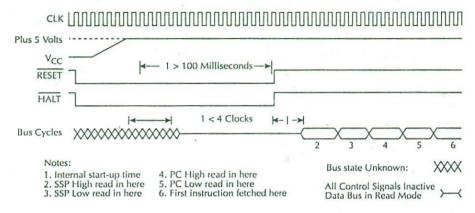

The 80286 does not have on-chip clock generator circuitry. Therefore, an external 82284 chip is required. The 80286 has a single CLK pin for a single-phase clock input. The 80286 divides its input clock by 2 internally and then provides the processor clock. The 82284 also

provides the 80286 RESET and READY signals.

The 80286 external memory is configured as odd (BHE = 0) and even (A0 = 0) memory banks just like the 8086. The 80286 operates in a mode similar to the 8086 maximum mode. Some of the 80286 pins such as M/IO, S0, S1, HOLD, HLDA, READY, and LOCK have identical functions as the 8086. Two external interrupt pins (NMI and INTR) are provided. The nonmaskable interrupt NMI is serviced in the same way as the 8086. The INTR and COD/INTA are used together to provide an interrupt-type code on the data bus via external hardware. Note that the 80286 INTA is multiplexed with another function called the COD (code). This pin distinguishes instruction fetch cycles from memory data read cycles. Also, it distinguishes interrupt acknowledge cycles from I/O cycles. M/IO = HIGH and COD/INTA = HIGH define instruction fetch cycle. On the other hand, M/IO = LOW and COD/INTA = LOW specify interrupt acknowledge cycle.

A new pin called the CAP is provided on the chip. The 80286 MOS substrate must be applied with a negative voltage for maximum speed. The negative voltage is obtained from the +5V. An external capacitor must be connected to the CAP pin for filtering this bias voltage.

<u>Four pins are provided to interface the 80286</u> with a coprocessor. These are PEREQ, PEACK, BUSY, and ERROR. The PEREQ (Processor Extension Request) input pin can be activated by the coprocessor to tell the 80286 to <u>perform</u> data transfer to or from memory for it. When the 80286 is ready, it activates the PEACK (Processor Extension Acknowledge) signal to inform the coprocessor of the start of the transfer. The 80286 BUSY signal input, when activated LOW by the coprocessor, stops 80286 program execution on WAIT and some ESC instructions until <u>BUSY</u> is HIGH. If a coprocessor finds some error during processing, it will activate the 80286 ERROR input pin. This will generate an interrupt. A service routine for this interrupt can be written to provide an indication to inform the user of the error.

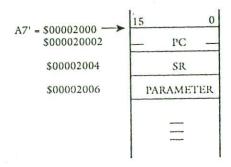

Upon hardware reset, the 80286 operates in real (physical) address mode and starts executing programs at physical address FFFOH like the 8086. In this mode, 20-bit physical addresses are generated by adding a 16-bit offset to the shifted (4 times to the left) segment register just like the 8086. Note that after hardware reset, the 80286 sets A23-A20 to all ones, CS = F000H, DS = 0000H, ES = 0000H, and SS = 0000H.

The 80286 on-chip MMU is disabled in the real address mode. In this mode, the 80286 acts functionally as a high-performance 8086. This mode averages 2 ½ times the performance of an 8086 running at the same clock frequency. All instructions of the 8086, 80186, plus a few

more such as LMSW (Load Machine Status Word) and SMSW (Store Machine Status Word) are available with the 80286 in the real address mode. In this mode, the 80286 supports only the 8086 data types and can directly execute 8086 machine code programs with minor modifications. When interfaced with an 80287 floating point coprocessor, the 80286 supports 8087 floating point data types also. Upon hardware reset, the 80286 operates in real address mode unless the user sets a bit in the Machine States Word (MSW) register by using the LMSW instruction to change the 80286 mode to Protected Virtual Address Mode (PVAM). Note that before changing to PVAM, descriptor tables must be in memory. The 80286, in real address mode, can run 8086 or 8088 software. Now, to change the 80286 mode from real address to PVAM, the user should read the contents of MSW, set just the Protection Enable (PE) bit to 1 without changing the other bits, and then load the new data into the MSW. The following instruction sequence will accomplish this:

SMSW CX ; Store MSW into a general register such as CX

OR CX, 1 ; Set only the PE bit (bit 0 in MSW) LMSW CX ; Load the new value back to MSW.

After the above instruction sequence is executed, the 80286 operates in PVAM with memory management capabilities. In the PVAM, the 80286 is compatible with the 8086/8088 at the source code level but not at the machine code level. This means that most 8086/8088 programs must be recompiled or reassembled. Note that the real address mode is normally used to initialize peripheral devices, transfer the main portion of the operating system from disk to main memory, initialize some registers, enable interrupts and place the 80286 into PVAM.

When the 80286 is in the protected mode, the on-chip MMU is enabled which expects several address-mapping tables to exist in memory. The 80286, in this mode, will automatically access these tables for translating the logical addresses used by the user to physical addresses. Once the 80286 is in PVAM, the only way to get back to the real mode is via hardware reset. This is intentionally done so that a malicious programmer cannot switch the mode from PVAM to real mode and thus the protection feature in PVAM is maintained.

The 80286 supports the following data types:

- · 8-bit or 16-bit signed binary numbers (integers)

- · Unsigned 8- or 16-bit numbers (ordinal)

- · A 32-bit pointer comprised of a 16-bit segment selector and 16-bit offset

- · A contiguous sequence of bytes or words (strings)

- ASCII

- · Packed and unpacked BCD

- · Floating point

The 80286 provides 8 addressing modes. These include register, immediate, direct, register indirect, based, indexed, based index, and based indexed with displacement modes. The new 80286 instructions are for supporting the PVAM of the 80286 via an operating system.

These instructions are listed in the following and are used by the operating system:

| CTST | Clear task switch flag to zero located in the MSW register                          |

|------|-------------------------------------------------------------------------------------|

| LGDT | Load global descriptor table register from memory                                   |

| SGDT | Store global descriptor table register into memory                                  |

| LIDT | Load interrupt descriptor table register from memory                                |

| LLDT | Load selector and associated descriptor into LDTR (local descriptor table register) |

| SLDT | Store selector from LDTR in specified register or memory                            |

| LTR  | Load task register and descriptor for TSS (task state segment)                      |

| STR  | Store selector from task register in register or memory       |

|------|---------------------------------------------------------------|

| LMSW | Load MSW register from register or memory                     |

| SMSW | Store MSW register in register or memory                      |

| LAR  | Load access rights byte of descriptor into register or memory |

| LSL  | Load segment limit from descriptor into register or memory    |

| ARPL | Adjust register privilege Level of selector                   |

| VERR | Determine if segment addressed by a selector is readable      |

| VERW | Determine if segment pointed to the selector is writable      |

Next, the 80286 will be considered from an operating systems point of view. In this context, the memory management capabilities protection and task switching features of the 80286 will be covered. Using these on-chip hardware features, a multitasking operating system can be implemented in the 80286-based microcomputer system.

The 80286 memory management features provide the operating system with the following

capabilities:

- An operating system which can separate tasks from each other. This avoids an 80286 system failure due to task errors.

- As tasks begin and end, the operating system can optimize memory usage by moving them around, a process referred to as dynamic relocation. This is because a program can be executed in different parts of memory without being reassembled or recompiled.

- Use of virtual memory becomes easy. Note that virtual memory is a method for executing programs larger than the main memory by automatically transferring parts of the programs between main memory and disk.

- · Controlled sharing of information between tasks.

The 80286 protection features allow:

- · An operating system to protect itself from malicious users in a multiuser environment

- Critical subsystems such as disk I/O from being destroyed by program bugs under development

The 80286 task switching provides:

Fast task switching due to 80286's hardware implementation for accomplishing this

feature. This permits the 80286 to spend more time on task excition than switching.

Real-time systems can thus be supported by the 80286 since they may require fast task

switching. Note that an exception in a running task or an interrupt from a peripheral

device requires task switching.

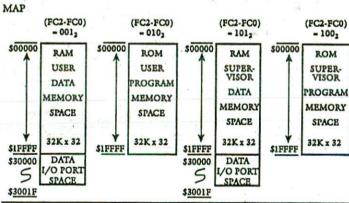

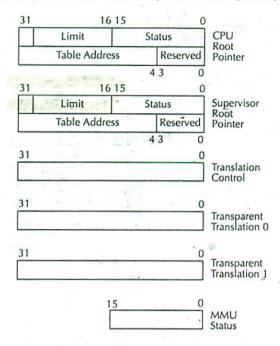

## 4.1.2.a 80286 Memory Management

The 80286 logical segments may be called virtual segments because all of them may not be resident in physical memory at the same time. A 80286 logical segment can be of any length from 1 byte to 64K bytes. During creation of each segment, a size or limit value is defined. This makes it easier for the 80286 to determine if a memory access is within bounds of a segment. The segments presently used by a task are stored in physical memory. In PVAM, all 24 address pins are used and therefore, the directly addressable (physical) memory is 16 megabytes. While writing 80286 programs in PVAM, one can refer to the current segment by the assigned names. For example, if a segment called JOHN is to be used as the current data segment, then the following instructions should be used to load JOHN into DS:

MOV BX, JOHN MOV DS, BX.

When the 80286 executes the above instruction segment, it will use JOHN as the current data segment. If the segment JOHN is not currently resident in Physical memory, the 80286 will generate an interrupt. A service routine is written to load this segment from disk to physical memory and then resume execution of the main program.

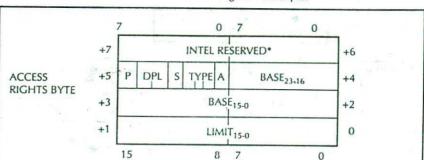

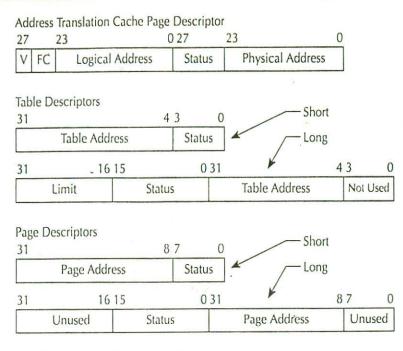

In PVAM, when a program is assembled, a descriptor (8-byte wide) is assigned to each segment. The descriptor contains information such as segment length in bytes, 24-bit base address where the segment is located in physical memory and the privilege level.

The descriptors are held in tables in main memory and are read into the 80286 as needed. There are two main types of descriptor tables. These are the global and the local descriptor tables. A system can contain only one global descriptor table. The global descriptor table includes information such as the descriptors for the operating system segments and the descriptors for segments which are accessed by user tasks. A local descriptor is created in the system for each task. All tasks share a global descriptor table with the memory areas specified by its descriptors. Also, each task contains its own local descriptor table with the memory areas specified by its descriptors.

In PVAM, all programs are written using segments. Each segment is assigned with an 8-byte descriptor which includes the length, starting address, and access rights for that segment. Segment descriptors for programs are stored in memory either in the global descriptor table or in a local descriptor table.

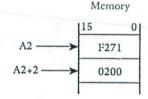

The 80286 memory management is based on address translation. That is, the 80286 translates logical addresses (addresses used in programs) to physical addresses (addressing required by memory hardware). The 80286 memory pointer includes two 16-bit words: one word for a segment selector and the other as an offset into the selected segment. The real and virtual modes compute physical addresses from these selector and offset values in different ways.

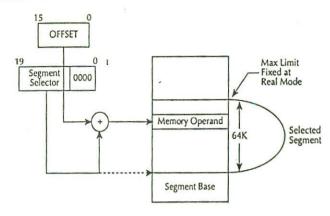

In the real address mode, the 80286 computes the physical address from a 16-bit (selector) content and a 16-bit offset just like the 8086/80186. It shifts the 16-bit selector four times to the left and then adds the 16-bit offset to determine the 20-bit physical address. As mentioned before, even though the 80286 has 24 address pins (A0-A23), in the real address mode pins A0-A19 are used. Also, A20-A23 pins are only used at reset for CS and are zero otherwise.

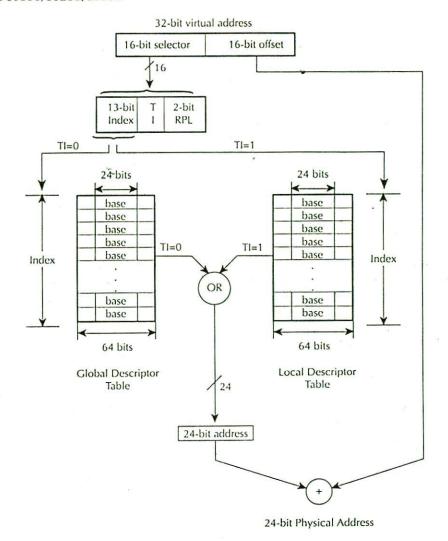

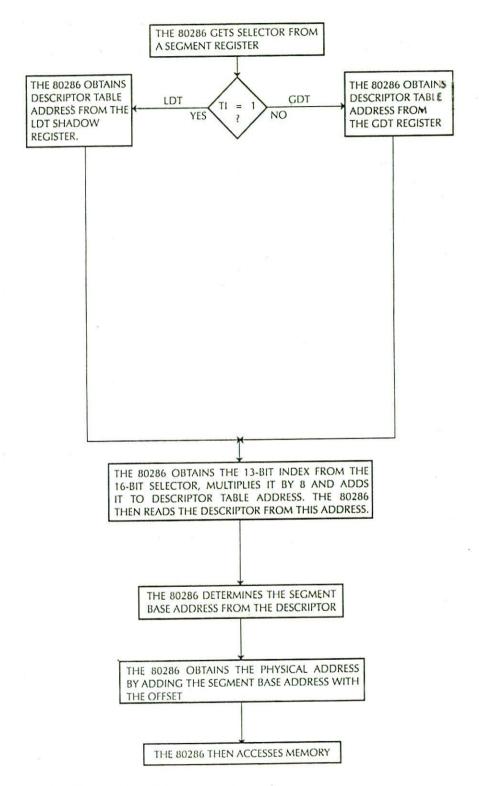

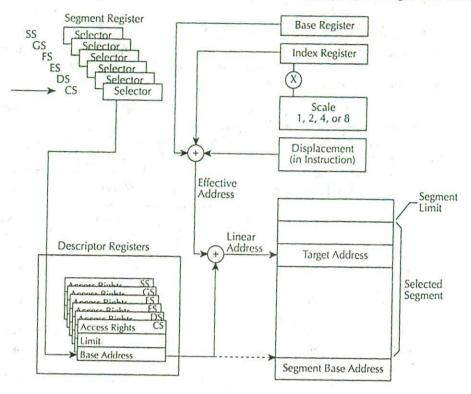

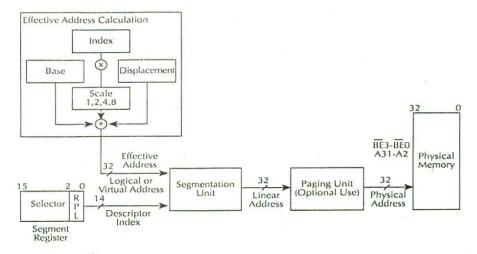

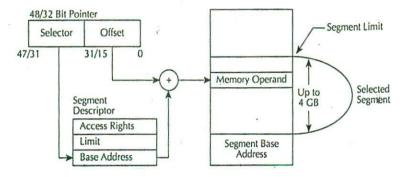

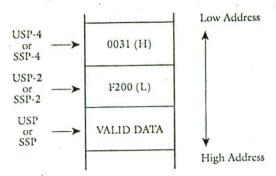

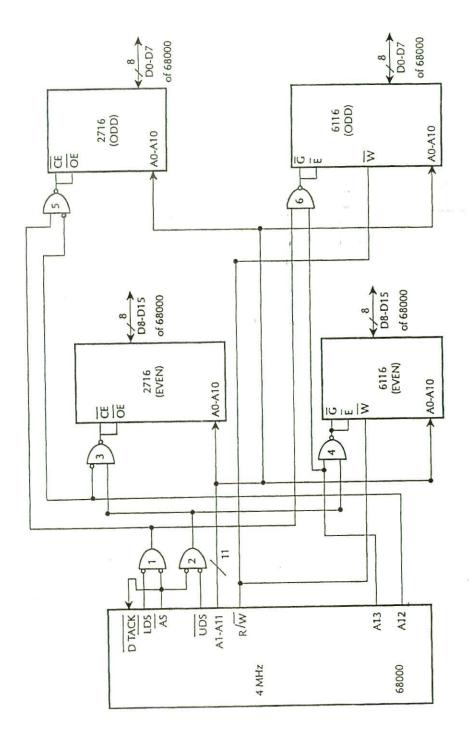

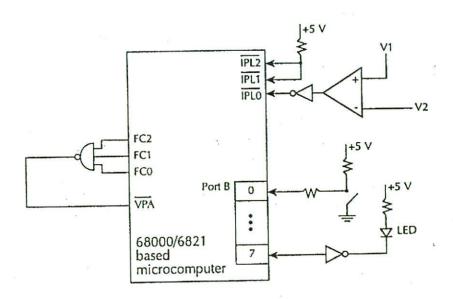

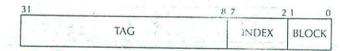

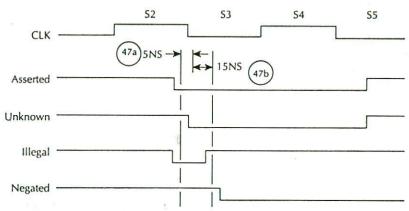

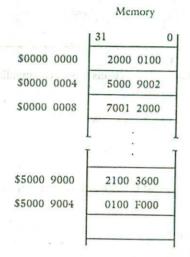

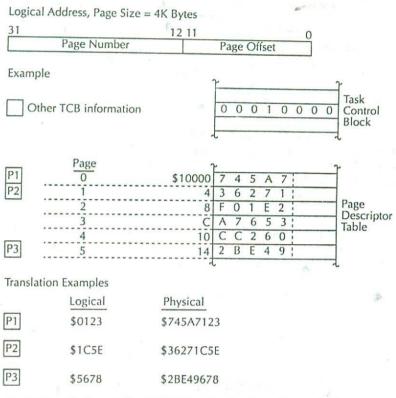

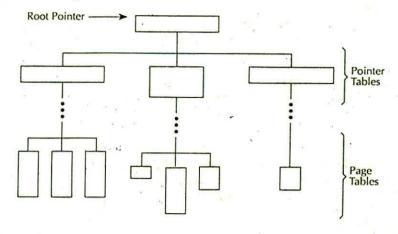

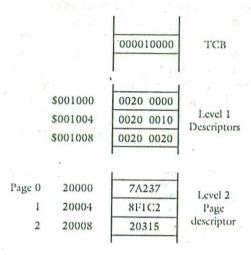

In the Protected Virtual Address Mode (PVAM or virtual mode for short), the 32-bit address is called a virtual address. Just like the logical address, the virtual address includes a 16-bit selector and a 16-bit offset. The 80286 determines the 24-bit physical address by first obtaining a 24-bit value from a table in memory using the segment value (selector) as an index (rather than shifting the segment value 4 times to left as in the real mode) and then adding the 16-bit offset. Figure 4.3 shows the 80286 virtual address translation scheme.

The 16-bit selector is divided into a 13-bit index, one-bit Table Indicator (TI), and two-bit Requested Privilege Level (RPL). The 13-bit index is used as a displacement to access the selected table. Each entry in the table is termed a descriptor. An index can start from a value of 0 to a higher value. The index value refers to a descriptor in the table. For example, index value K refers to the descriptor K. Each descriptor is 8 bytes wide and contains the 24-bit base address required for physical address calculation. This address only occupies three bytes of the 8-byte descriptor. The meaning of the other bytes will be explained later. The single-bit TI tells the 80286 to select one of two tables: Global Descriptor Table (GDT) and Local Descriptor Table (LDT). All tasks in the 80286 share a common single table called the GDT, while each task has its own LDT. Therefore, the 24-bit base addresses required in physical address calculation for segments to be shared by all tasks are stored in the GDT and the base addresses for segments dedicated to a particular task are stored in its LDT. When TI = 0, the GDT is used as the look-up table, and when TI = 1, the LDT is used as the look-up table. The 2-bit RPL is used by the operating system for implementing the 80286's protection features. RPL is not used in physical address calculation.

The 24-bit physical address is then generated by the 80286 by adding the 24-bit base address of the selected descriptor and the 16-bit offset.

FIGURE 4.3 80286 virtual address translation.

Note that in the above, when TI = 0 (GDT selector) and Index = 0, a null selector is selected. The selector does not correspond to the 0th GDT descriptor. Null selectors can be loaded into a segment register, but use of null selectors in virtual address translation would generate an 80286 exception.

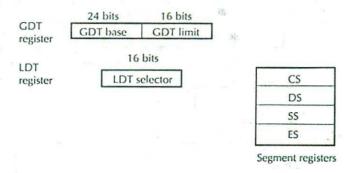

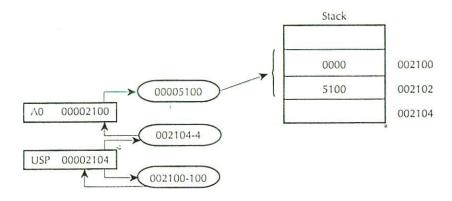

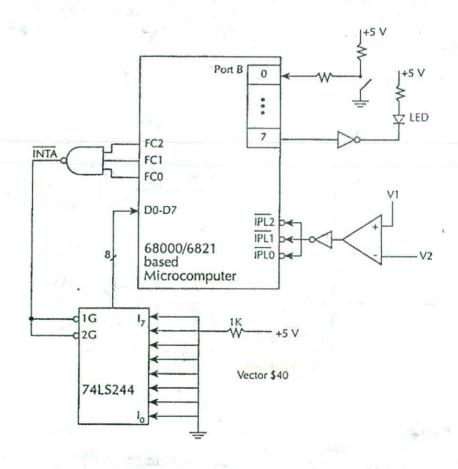

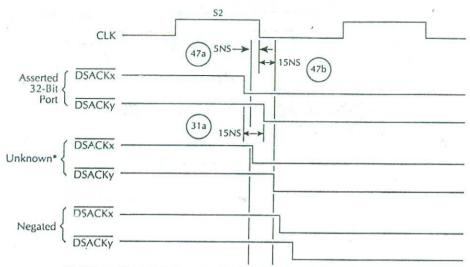

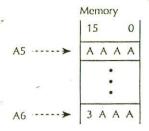

Figure 4.4 shows the 80286 address translation registers. The segment registers CS, DS, SS, and ES have already been discussed before. The GDT and LDT registers are only used in the 80286 virtual mode address translation. The GDT register stores the 24-bit base address and the length of the GDT (in bytes) minus one. During system initialization, the GDT is loaded and is usually kept unchanged after this. The 80286 generates an exception when indexing beyond the GDT limit is attempted.

The LDT register stores a 16-bit selector for a descriptor in the GDT which defines the location of the present LDT. The 80286 task switch operation is invoked by executing an inter-segment JMP or CALL instruction which refers to a task state segment (TSS) or task gate descriptor in the GDT or LDT. Each task must have a TSS associated with it. The current TSS is identified by a special register in the 80286 called the Task Register (TR). The TR register makes task switching automatic and very fast. For example, the 80286 local address space can be modified during task switching by updating the LDT register. Figure 4.5 shows flowchart for accessing memory.

FIGURE 4.4 80286 address translation registers.

The 80286 contains a number of special registers called shadow registers which are provided to speed up memory references. The shadow registers are internal and cannot be accessed by instructions. Whenever a selector is moved into a segment register, the associated shadow register is updated with its descriptor automatically. Therefore, any memory accessed with respect to the segment register does not require referral to a look-up table, since the descriptor loaded into the shadow register contains the base address of the selected segment.

Note that in the virtual mode, the 80286 descriptor table can store a maximum of  $2^{13}$  (13-bit index) descriptors and each segment can specify a segment of up to  $2^{16}$  bytes. Therefore, a task can have its own LDT address space of up to  $2^{13} \times 2^{16} = 2^{29}$  bytes and can share  $2^{29}$  bytes (GDT) with all other tasks. Therefore, an address space of 1 gigabyte ( $2^{30}$  bytes) can be assigned to a task.

The following 80286 memory management instructions include loading and storing the address translation registers and checking the contents of descriptors:

| LGDT | Load GDT register  |

|------|--------------------|

| SGDT | Store GDT register |

| LLDT | Load LDT register  |

| SLDT | Store LDT register |

| LAR  | Load Access Rights |

| LSL  | Load Segment Limit |

#### 4.1.2.b Protection

In PVAM, the 80286 has built-in features for the following protection schemes:

- 1. Protecting system software such as the operating system from user programs.

- 2. Protecting one user task from another.

- 3. Protecting portions of memory from accidental access.

The 80286 protection mechanism is implemented by using the contents of the descriptors. Any access to memory is validated by checking the information in segment descriptors. The 80286 generates an interrupt if the memory access is invalid.

The 80286 provides protection mechanism for supporting multitasking and virtual memory features. The 80286 includes certain basic protection features such as segment limit and segment usage checking. These basic protections are useful even though multitasking and virtual memory may not be available in a system. The basic protection mechanism also allows assignment of privilege levels to virtual memory space in a hierarchical manner.

The 80286 privilege level mechanism uses certain rules to define the hierarchical order. This allows protection of the operating system independent of the user. The 80286 includes special descriptor table entries named call gates to permit CALLS to higher privilege code segments

FIGURE 4.5 Flowchart showing steps for accessing memory.

#### Code or Data Segment Descriptor

Access Rights Byte Definition

| Bit<br>Position                                                                                                                         | Name *                             | Function                                      |                                                                                                                         |                   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| 7                                                                                                                                       | Present (P)                        | P = 1 Segment is mapped into physical Memory. |                                                                                                                         |                   |  |  |

| 6-5                                                                                                                                     | Decriptor Privilege<br>Level (DPL) | P = 0                                         |                                                                                                                         |                   |  |  |

| 4 Segment Descriptor S = 1 Code or data (includes stacks) segment descriptor tor (S) S = 0 System Segment Descriptor or Gate Descriptor |                                    |                                               |                                                                                                                         | 8                 |  |  |

| 3                                                                                                                                       | Executable (E)                     | E = 0                                         | Data segment descriptor type is:                                                                                        | lf .              |  |  |

| 2                                                                                                                                       | Expansion Direc-<br>tion (ED)      | ED = 0<br>ED = 1                              | Expand up segment, offsets must be ≤ limit.  Expand down segment, offsets must be > limit.                              | Data — Segment    |  |  |

| 1                                                                                                                                       | Writeable (W)                      | W = 0<br>W = 1                                | Data segment may not be written into.  Data segment may be written into.                                                | (S = 1,<br>E = 0) |  |  |

| 3                                                                                                                                       | Executable (E)                     | E = 1                                         | Code Segment Descriptor type is:                                                                                        | 1 .               |  |  |

| 2                                                                                                                                       | Conforming (C)                     | C = 1                                         | Code segment may only be executed when CPL ≥ DPL and CPL remains unchanged.                                             | Code Segment      |  |  |

| 1                                                                                                                                       | Readable (R)                       | R = 0 $R = 1$                                 | Code segment may not be read. Code segment may be read.                                                                 | (S = 1,<br>E = 0) |  |  |

| 0                                                                                                                                       | Accessed (A)                       | A = 0<br>A = 1                                | Segment has not been accessed. Segment selector has been loaded into segment register or by selector test instructions. | used              |  |  |

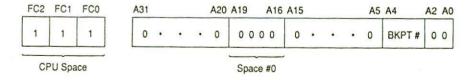

FIGURE 4.6 Code and data segment descriptor contents.

\*Must be set to 0 for compatibility with IAPX 386.

at specific valid entry points. In order to protect the operating system, the 80286 does not allow accessing a higher privilege entry point without its access gate.

The 80286 provides some instructions controlled by its IOPL (Input/Output Privilege Level) feature to protect shared system resources. The I/O instructions are permitted at the highest privilege level.

The 80286 on-chip protection features handle basic violations such as trying to access code segment instead of stack segment by trapping into the operating systems's appropriate routine. Thus, the operating system recovers a faulty task by taking whatever actions are necessary. The 80286 protection hardware provides information such as stack status to inform the operating system of the fault type.

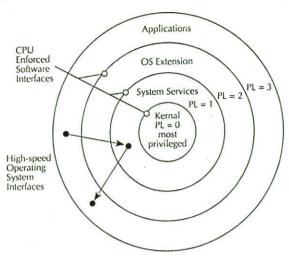

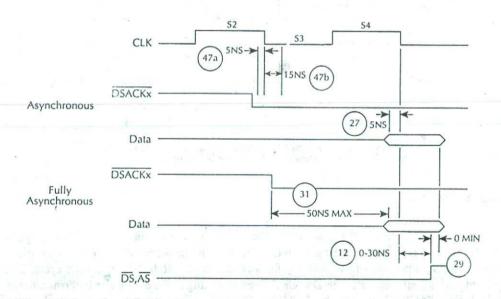

The 80286 on-chip protection hardware provides up to four privilege levels in a hierarchical manner which can be used to protect system software such as the operating system from unauthorized access. The 80286 can read specific bits in its segment descriptor to obtain privilege levels of each code and data segment. Figure 4.6 shows the format for a segment descriptor for a code or data segment.

The descriptors include four words. Bit 3 of the 3-bit-type field of the access rights byte is called the Executable (E) bit. E = 1 identifies a code segment descriptor, while E = 0 identifies the segment as a data segment descriptor. The two-bit DPL (Descriptor Privilege Level) provides the privilege level of the descriptor. The DPL field specifies a hierarchical privilege system of four levels 0 thru 3.

Level 0 is the highest level while level 3 is the lowest. Privilege level provides protection within a task. Operating system routines, interrupt handlers, and other system software can be included and protected within the virtual address space of each task using the four levels of privileges. Each task in the system has a separate stack for each of its privilege levels. Typical examples of privilege levels are summarized as follows:

- A single privilege level can be assigned to all the code of π dedicated 80286. In this case, all load/store and I/O instructions are available. The 80286 can be initialized by setting the PE bit in MSW to one and then loading the GDTR with appropriate values to address a valid global descriptor table.

- Privilege levels can be assigned to user and supervisor mode types of applications. In this

case, all system software can be defined as level 0 (highest level) and all other programs

at some lower privilege level.

- For large applications, the system software can be divided into critical and noncritical.

All critical software can be defined as a kernel with the highest privilege level (level 0),

the noncritical portion of the system software is defined with levels 1 and 2, while all

user application programs are defined with the lowest level (level 3).

Upon enabling the protected mode bit, the 80286 basic protection features are available irrespective of a single 80286-type application or user/supervisor configuration or a large application. The descriptor's limit field (the maximum offset from the base) and the access rights byte provides the 80286's basic protection features.

Segment limit checking ensures that all memory accesses are physically available in the segment. For all read and write operations with memory, the 80286 in the protected mode automatically checks the offset of an effective address with the descriptor limit (predefined). This limit checking feature ensures that a software fault in a segment does not interfere with any other segments in the system.

The descriptor access rights byte complements the limit checking. It differentiates code segments from data segments. The access right byte along with limit checking ensures proper usage of the segments. At least three types of segments can be defined using the access byte. Data segments can be defined as read/write or read-only. Code segments can be designated as execute-only and can be defined as conforming segments. A code segment in a particular privilege level can be accessed by using 80286 CALL or JMP instruction without a privilege level transition. A segment of equal or lower privilege level than another segment (defined as conforming via the access byte) can access that segment.

The hierarchical protection levels have four logical rules. These are summarized below:

- The Current Privilege Level (CPL) at any instant of time represents the level of the code segment presently being executed. This is provided by the privilege level in the access rights byte of the descriptor. The 80286 gives the value of CPL in its code register.

- Since every privilege level has its own stack, a stack segment rule is implemented in the 80286 to ensure using the proper stack. According to this rule, the stack segment (stack addressed by the stack segment register) and the current code segment must have the identical privilege level.

- As far as the data segments are concerned, the DPL (Descriptor Privilege Level) of an

accessed data segment must be lower than or equal to the CPL. This rule allows

protection of privileged data segments from unprivileged codes.

- The 80286 is provided with a rule which pertains to accessing data segments. The 80286 can access data segments of equal or lower privilege with respect to the CPL. For example, if CPL is 1, the 80286 codes in current code segment can access data segments with privilege levels of 1, 2, or 3, but not 0.

- The 80286 allows CALLing a subroutine in a code segment with higher privilege level by using call gates, and returns to code with lower privilege code segments. This is called the flow control rule and it protects higher privilege code segments. For example, if the CPL is 2, all code segments with levels 2 and 3 can be accessed by the 80286; code segments of levels 0 or 1 cannot be accessed directly. However, lower or equal privilege level accesses can be done directly. Also, higher privilege level accesses can be controlled by special descriptor table entries known as call gates. A call gate is 8 bytes wide and is stored like a descriptor in a descriptor table.

The main difference between a descriptor and a call gate is that a descriptor's contents refer to a segment in memory. On the other hand, a gate refers to another descriptor.

A descriptor includes a 24-bit physical base address, while a gate contains a 32-bit virtual address. When the effective address of an intersegment CALL references a call gate, the 80286 redirects control to the destination address defined within the gate. The 32-bit virtual address (selector and offset) of the gate can be used by the 80286 to access a higher privilege code segment.

The 80286 controls the use of I/O instructions. The user may choose the level at which these I/O instructions can be used. This level is called the IOPL (Input Output Privilege Level).

IOPL is a two-bit flag whose value varies from 0 to 3. In a user/supervisor configuration in which all supervisor code is at level 0 (highest) and all user code is at lower levels, the IOPL should be 0. This zero value of IOPL allows the supervisor code to carry out I/O operations but ensures that the user code cannot execute these I/O instructions.

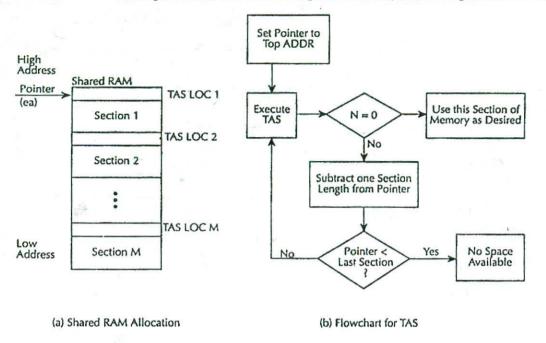

Protection of a task from unauthorized access by another is provided by the 80286 both in virtual and physical memory spaces. The 80286 provides a multitasking feature via its virtual memory capabilities. As mentioned before, the virtual memory space consists of two spaces: global and local. The local space is unique to the present task being executed. This uniqueness of the local spaces provides intertask protection in the virtual memory space. The 80286's limit checking feature in the physical memory space avoids illegal accesses of segments beyond the defined segment limits and thus provides protection.

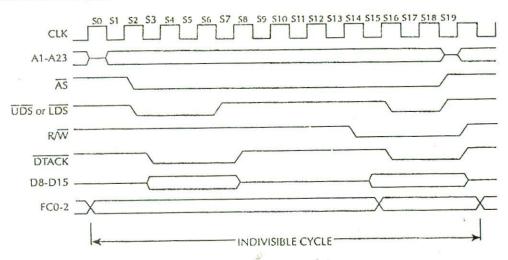

The 80286 is especially designed to execute several different tasks simultaneously (appears to be simultaneous). This is called multitasking. If the present task needs to wait for some external data, the 80286 can be programmed to switch to another task until such data are available. This mechanism of switching from one task to another is called task switching. The 80286 automatically performs all the necessary steps in order to properly switch from one task to another. When a task switching takes place, the 80286 stores the state of the present task (typically most of the 80286 registers), loads the state of the new task, and starts executing the new task. If execution of the outgoing task is desired after completion of the incoming one, the 80286 can automatically go back to the right place where the task switch took place.

Task switching may occur due to hardware or software reasons. For example, task switching may take place due to 80286 external interrupt requests (hardware reason) or due to the operating system's desire to time-share the 80286 among multiple user tasks (software reason). The task to be executed due to interrupts is termed interrupt-scheduled, while the task to be executed due to time-sharing by the operating system is called software-scheduled.

As soon as an interrupt-scheduled or a software-scheduled task is ready to be run by the 80286, it becomes the currently active (incoming) task. All inactive tasks (outgoing) have code and data segments saved in memory or disk by the 80286. Each outgoing task has a Task State Segment (TSS) associated with it. The TSS holds the task register state of an inactive task.

The TSS includes a special access right byte in its descriptor in the GDT in order that the 80286 can identify it as code or data segments. TSSs are referenced by 16-bit selectors (each task has a unique selector) that identify a TSS descriptor in the GDT. The 80286 stores the TSS selector of the presently active task in its Task State Segment register (TR). The first 44 bytes of a TSS store the complete state of a task. Information such as selectors and 80286 registers is saved.

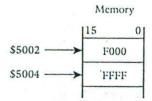

The 80286 provides protection for portions of memory from accidental access in the following ways. When a segment selector is to be loaded into a segment register, the 80286 automatically verifies whether the descriptor table indexed by the selector contains a valid descriptor for that selector. An interrupt is automatically generated by the 80286 if a valid descriptor is not present. However, if the descriptor is valid, the shadow registers are loaded with the base, limit, and access rights byte of the descriptor. The 80286 then verifies whether the segment for that descriptor is resident in physical memory. An interrupt is generated by the 80286 if it is not present (as indicated by the P-bit of the access rights byte of the descriptor). An interrupt service routine can be written to move the desired segment into physical memory and return execution to the main program. The 80286 also verifies whether the segment descriptor is of the right type to be loaded into the appropriate segment register. For example, the descriptor for a read-only data segment cannot be moved into a stack segment register since the stack is a read/write memory. After a segment selector and descriptor are loaded into a segment register, checks are made each time an address in the actual segment is accessed. For example, an attempt to write to a read-only data segment will generate an error. Also, the limit value in the segment descriptor is used to ensure that an address generated by program instructions is within the limit specified for the segment.

## Example 4.1

Discuss the 80286's performance impact on memory management while executing the following program:

```

MOV DS, Segmentselector

Load data selector

MOV BX, Displ

Load offset

MOV CX, Count

Load loop count

BEGIN

MOV DX,

data

Move 16-bit data to

DX

Find match

CMP DX, WORDPTR[BX]

JZ DONE

If match

found, stop

JMP BEGIN

else compare

HI.T

DONE

```

#### Solution

The 80286 memory management capabilities are only utilized when loading the selector value (first instruction in the above program). By loading the selector value into DS, the 80286 chooses a descriptor from a descriptor table and then automatically determines the physical address of that segment using the descriptor. Thus, by executing the first instruction MOV DS, segmentselector, the 80286 automatically determines the segment's physical address (transparent to the user).

After determining the segment's physical address, the 80286 executes all other instructions that follow. The 80286 reads data from the data segment every time it goes through the BEGIN loop. The 80286 does not refer to the descriptor table because of its on-chip cache.

Like any other memory management system, the 80286 will have some overhead for performing the virtual address to the physical address translation. This is transparent to the user's application programs and is automatically carried out by the 80286. The memory management overhead (virtual to physical address translation) is minimized due to on-chip cache. One of the main characteristics of on-chip MMU is that after the descriptor is read into the on-chip cache memory, no overhead occurs. Therefore, the overhead is kept at a minimum, thus providing good performance.

#### 4.1.2.c 80286 Exceptions

In the real address mode, the 80286 exception mechanism is similar to the 8086 except a few more exceptions such as the 'invalid opcode exception' is included in the 80286. External interrupts such as the maskable (INTR) and nonmaskable (NMI) interrupts in the 80286 are serviced in the real address mode by using interrupt vector table with 256 vectors similar to the 8086.

In the protected mode, the 80286 detects exceptions essential to its protection model, and its support for multitasking and virtual memory. Some examples of the non-real mode exceptions include 'exception for code, data, or extra segment not present' and 'Privilege violation'. The protected mode pointers are actually gates, since gates in protected mode serve as a redirection mechanism. The interrupt table can contain task gates, interrupt gates, and trap gates. The interrupt table, in protected mode, is known as the IDT (Interrupt Descriptor Table). A special register called the IDTR (Interrupt Descriptor Table register) is used by the 80286 to locate the interrupt table both in real and protected modes. The IDTR is typically initialized by the system programmer once, to point at the desired area of physical memory.

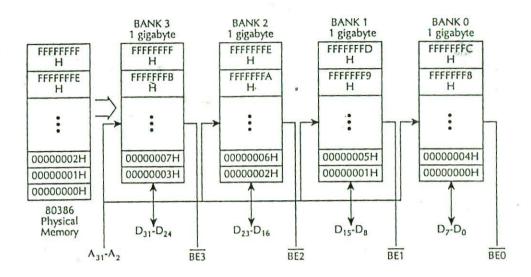

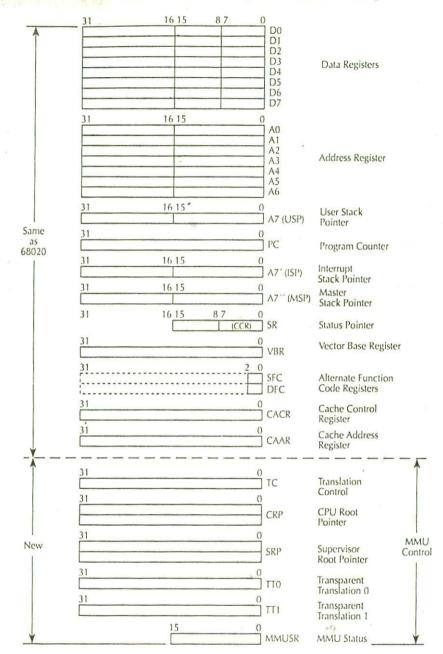

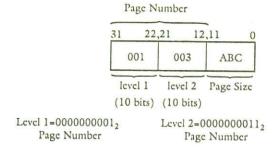

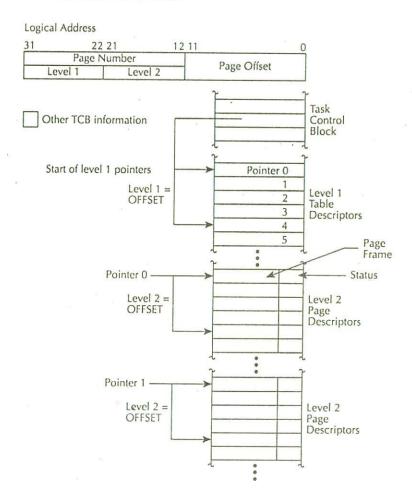

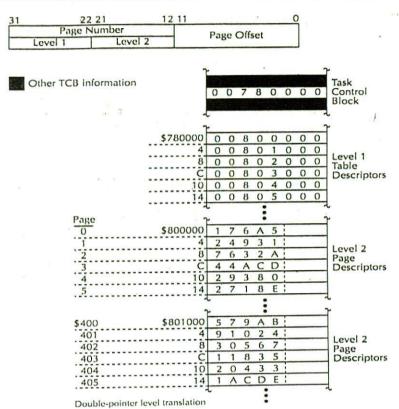

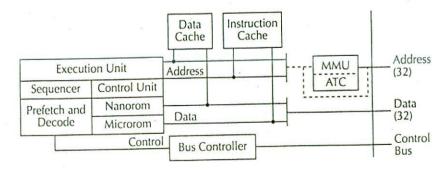

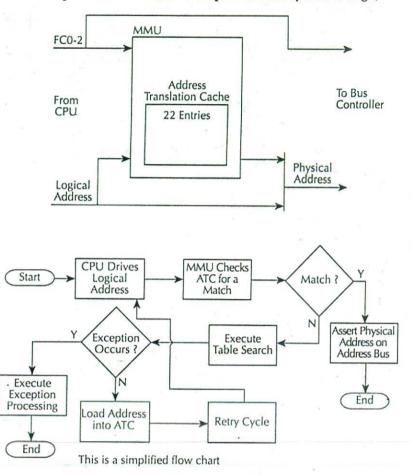

## 4.2 INTEL 80386

In 1985, Intel introduced its first 32-bit microprocessor, the 80386DX. It initially ran at a clock frequency of 16 MHz and contained 275,000 transistors. In 1988, Intel introduced the 80386SX which was a 16-bit external data bus version of the 80386DX (32-bit data bus). The 80386DX is a full 32-bit microprocessor and is available in 16-, 20-, 25- and 33-Mhz speed versions. It can directly address a maximum of 4 gigabytes of memory.

The 80386SX, on the other hand, can operate at 16- and 20-Mhz. The 80386SL is similar to the 80386SX with 16-bit data bus and can operate at 20- and 25-Mhz. The 80386SX and 80386SL can directly address up to 16 megabytes and 32 megabytes of memory respectively. Compaq was the first major OEM (Original Equipment Manufacturer) to use the 80386DX in 1986 in its PC. The 80386SL, on the other hand, is used in notebook computers with built-in power management options.

The 80386DX will be covered in detail in this section. The 80386 family of microprocessors will be referred to as the 80386 in the following.

The 80386 is a logical extension of the Intel 80286.

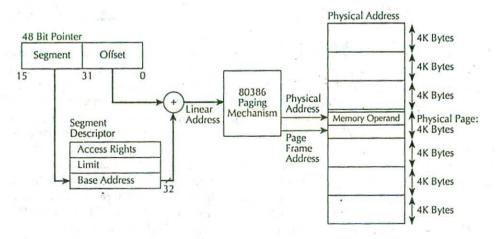

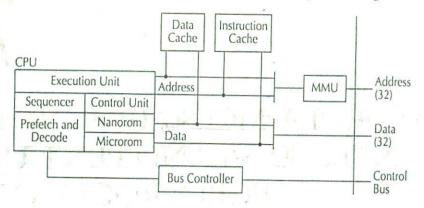

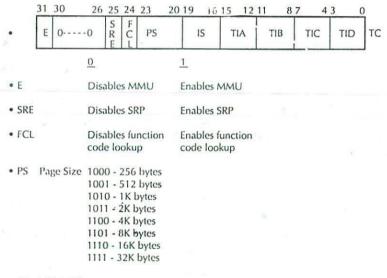

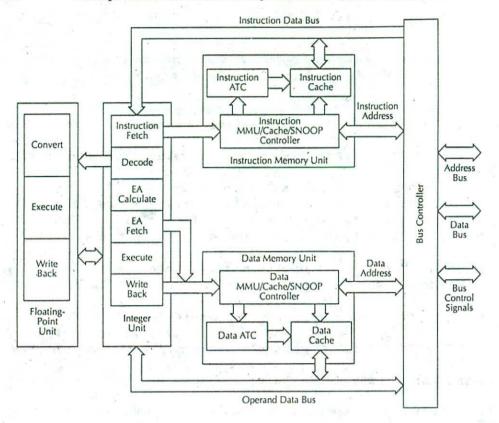

The 80386 provides multitasking support, memory management, pipelined architecture, address translation caches, and a high-speed bus interface in a single chip.

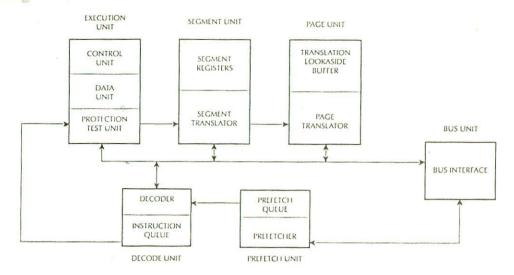

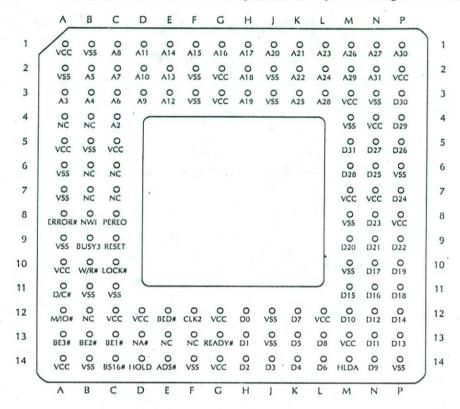

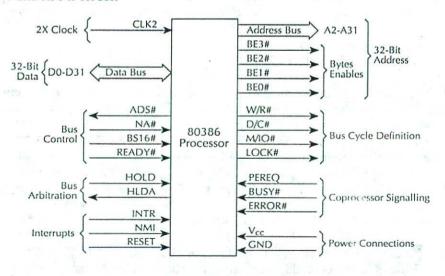

The 80386 is software compatible at the object code level with the Intel 8086, 80186, and 80286. The 80386 includes separate 32-bit internal and external data paths along with eight general-purpose 32-bit registers. The processor can handle 8-, 16-, and 32-bit data types. It has separate 32-bit data and generates a 32-bit physical address. The chip has 132 pins and is housed in a Pin Grid Array (PGA) package. The 80386 is designed using high-speed CHMOS III technology.

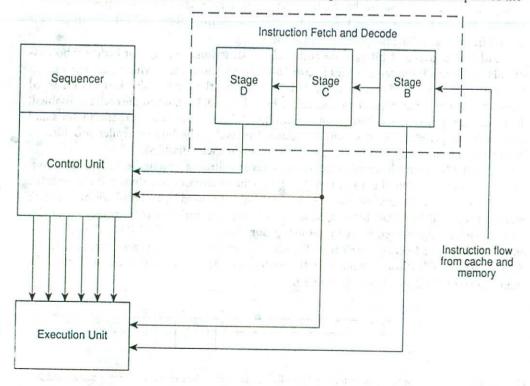

The 80386 is highly pipelined and can perform instruction fetching, decoding, execution, and memory management functions in parallel. The on-chip memory management and protection hardware translates logical addresses to physical addresses and provides the protec-

FIGURE 4.7 80386 functional units.

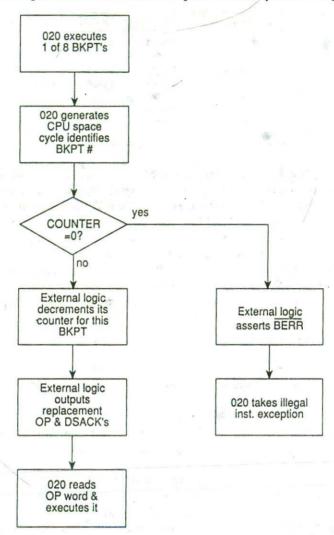

tion rules required in a multitasking environment. The 80386 includes special hardware for task switching. A single instruction or an interrupt is required for the 80386 to perform complete task switching. A 16-MHz 80386 can save the state of one task (all registers), load the state of another task (all registers, segment, and paging registers if needed), and resume execution in less than 16 microseconds. The 80386 contains a total of 129 instructions.

The 80386 protection mechanism, paging, and the instructions to support them are not present in the 8086. Also, the semantics of all instructions that affect segment registers (PUSH, POP, MOV, LES, LDS) and those affecting program flow (CALL, INTO, INT, IRET, JMP, RET) are quite different than the 8086 on the 80386 in protected mode.

The main differences between the 80286 and the 80386 are the 32-bit addresses and data types and paging and memory management. To provide these features and other applications, several new instructions are added in the 80386 instruction set beyond those of the 80286.

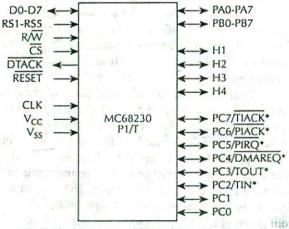

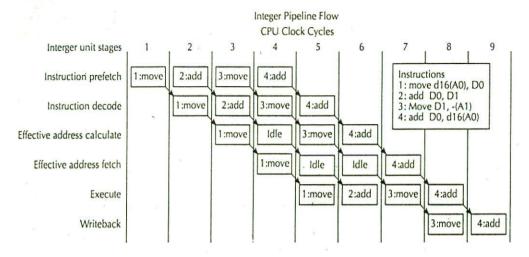

The internal architecture of the 80386 includes six functional units (Figure 4.7) that operate in parallel. The parallel operation is known as pipelined processing. Fetching, decoding, execution, memory management, and bus access for several instructions are performed simultaneously. The six functional units of the 80386 are

- · Bus interface unit

- · Code prefetch unit

- · Decode unit

- · Execution unit

- · Segmentation unit

- · Paging unit

The bus interface unit connects the 80386 with memory and I/O. Based on internal requests for fetching instructions and transferring data from the code prefetch unit, the 80386 generates the address, data, and control signals for the current bus cycles.

The code prefetch unit prefetches instructions when the bus interface unit is not executing bus cycles. It then stores them in a 16-byte instruction queue for decoding by the instruction decode unit.

The instruction decode unit translates instructions from the prefetch queue into microcodes. The decoded instructions are then stored in an instruction queue (FIFO) for processing by the execution unit. The execution unit processes the instructions from the instruction queue. It contains a control unit, a data unit, and a protection test unit.

The control unit contains microcode and parallel hardware for fast multiply, divide, and effective address calculation.

The data unit includes a 32-bit ALU, 8 general-purpose registers, and a 64-bit barrel shifter for performing multiple bit shifts in one clock. The data unit carries out data operations requested by the control unit. The protection test unit checks for segmentation violations under the control of the microcode.

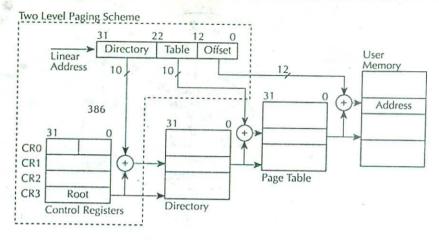

The segmentation unit translates logical addresses into linear addresses at the request of the execution unit.

The translated linear address is sent to the paging unit. Upon enabling of the paging mechanism, the 80386 translates these linear addresses into physical addresses. If paging is not enabled, the physical address is identical to the linear addresses and no translation is necessary.

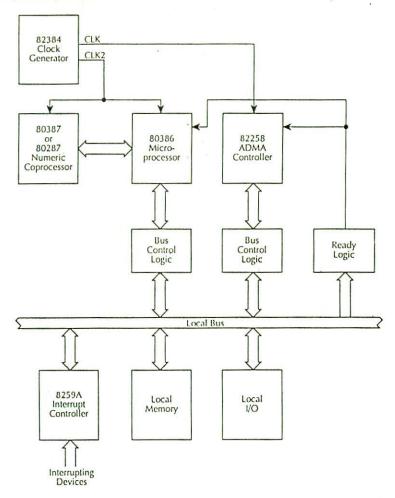

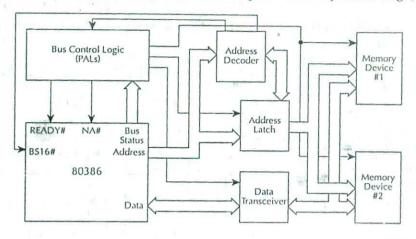

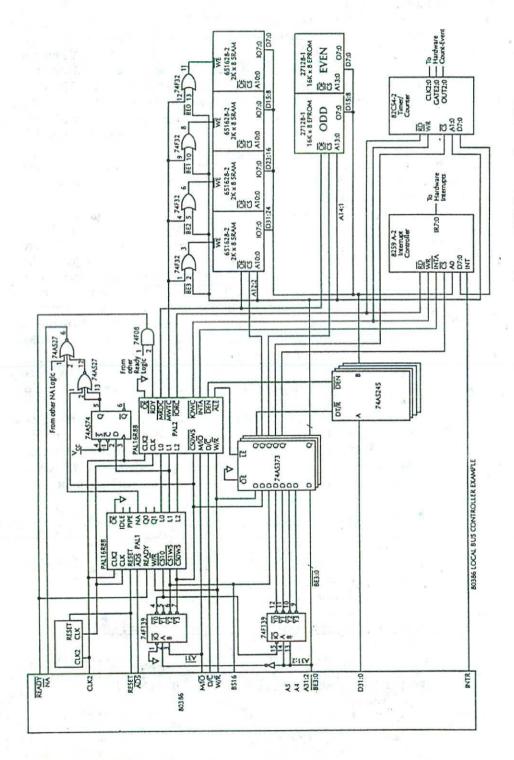

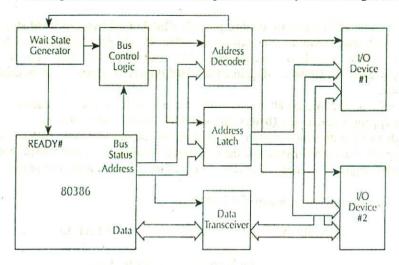

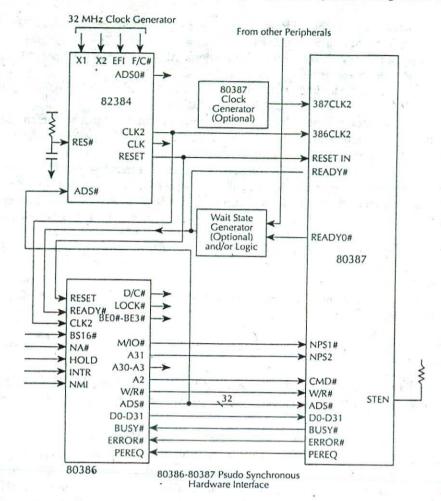

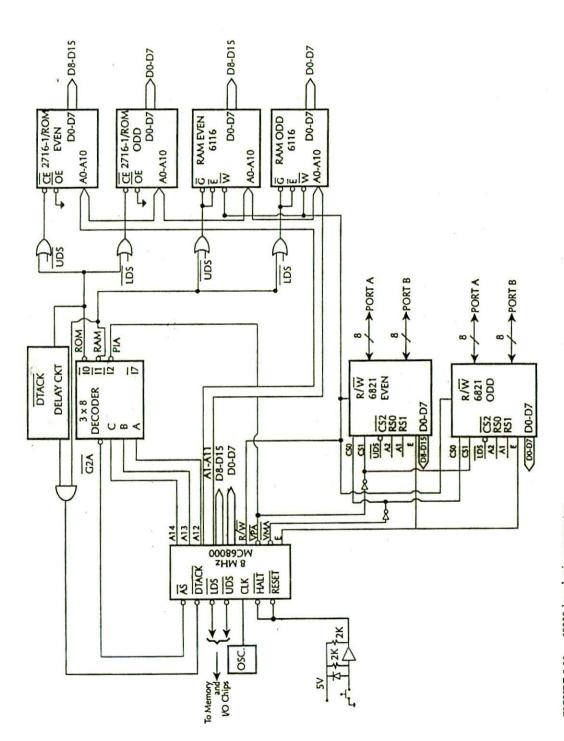

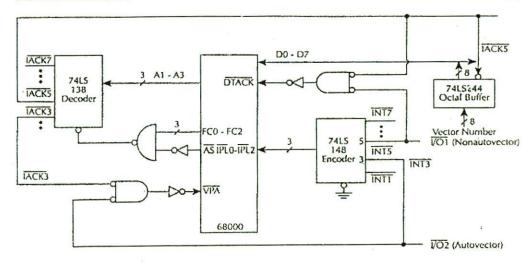

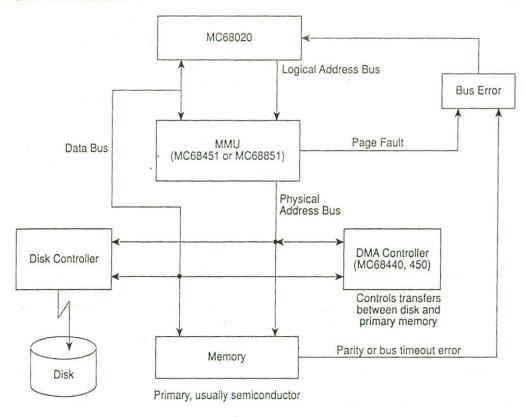

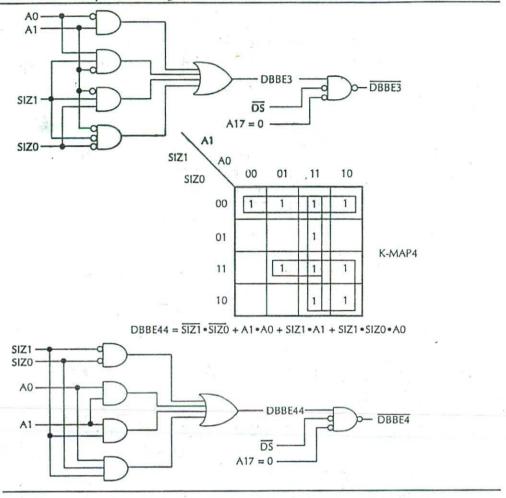

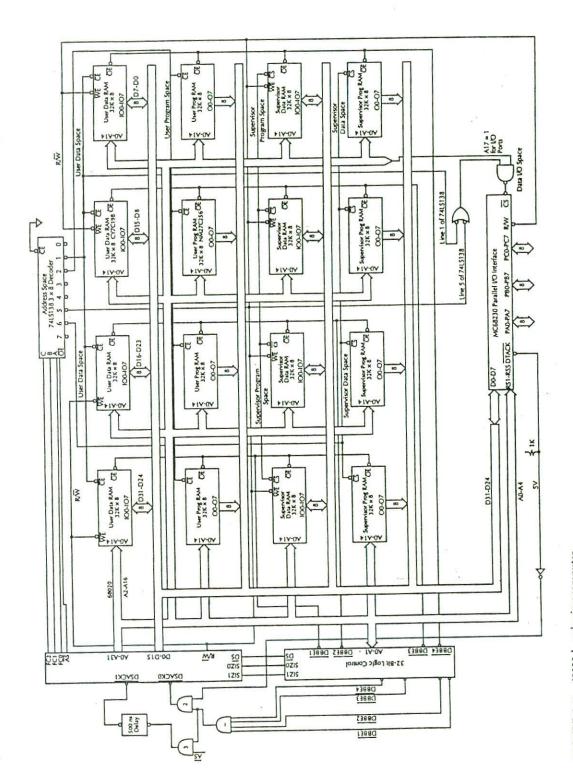

Figure 4.8 shows a typical 80386 system block diagram.

The 80287 or 80387 numeric coprocessor can be interfaced to the 80386 to extend the 80386 instruction set to include instructions such as floating point operations. These instructions are executed in parallel by the 80287 or 80387 with the 80386 and thus off-load the 80386 of these functions.

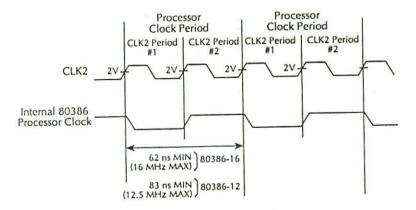

The 82384 clock generator provides system clock and reset signals. The 82384 generates both the 80386 clock (CLK2) and a half-frequency clock (CLK) to drive the 80286-compatible devices that may be included in the system. It also generates the 80386 RESET signal. The internal frequency of the 80386 is 1/2 the frequency of CLK2.

The 8259A interrupt controller provides interrupt control and management functions. Interrupts from as many as eight external sources are accepted by one 8259A and up to 64 interrupt requests can be handled by connecting several 8259A chips. The 8259A manages priorities between several interrupts, then interrupts the 80386 and sends a code to the 80386 to identify the source of the interrupt.

The 82258 Advanced DMA (ADMA) controller performs DMA transfers between the main memory and the I/O device such as a hard disk or floppy disk without involving the 80386. It provides four channels and all signals necessary to perform DMA transfers.

The 80386 has three processing modes: protected mode, real-address mode, and virtual 8086 mode.

Protected mode is the normal 32-bit application of the 80386. All instructions and features of the 80386 are available in this mode.

Real-address mode (also known as the "real mode") is the mode of operation of the processor upon hardware RESET. This mode appears to programmers as a fast 8086 with a few new instructions. This mode is utilized by most applications for initialization purposes only.

Virtual 8086 mode (also called V86 mode) is a mode in which the 80386 can go back and forth repeatedly between V86 mode and protected mode at a fast speed. The 80386, when entering into the V86 mode, can execute an 8086 program. The processor can then leave V86 mode and enter protected mode to execute an 80386 program.

As mentioned before, the 80386 enters real address mode upon hardware reset. In this mode, the Protection Enable (PE) bit in a control register called the Control Register 0 (CR0) is cleared to zero. Setting the PE bit in CR0 places the 80386 in protected mode. When in protected mode, setting the VM (Virtual Machine) bit in the flag register (called the EFLAGS register) will place the 80386 in V86 mode. Details of these modes are discussed later.

## 4.2.1 Basic 80386 Programming Model

The 80386 basic programming model includes the following aspects:

- a) Memory organization and segmentation

- b) Data types

| Component                                  | Description                                                                                               |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| 80386 Microprocessor                       | 32-bit high-performance microprocessor with on-clip memory<br>management and protection; no on-chip cache |  |  |  |

| 80287 or 80387 Numeric<br>Coprocessor      | Performs numeric instruction in parallel with 80386; expands instruction set                              |  |  |  |

| 82384 Clock Generator                      | Generates system clock and RESET signal                                                                   |  |  |  |

| 8259A Programmable Interrupt<br>Controller | Provides interrupt control and management                                                                 |  |  |  |

| 82258 Advanced DMA                         | Performs direct memory controller access (DMA)                                                            |  |  |  |

FIGURE 4.8 80386 system block diagram.

- c) Registers

- d) Addressing modes

I/O is not included as part of the basic programming model. This is because systems designers may select to use I/O instructions for application programs or may select to reserve

them for the operating system. Therefore, 80386 I/O capabilities will be covered during the discussion of systems programming.

## 4.2.1.a Memory Organization and Segmentation

The 4-gigabyte physical memory of the 80386 is structured as 8-bit bytes. Each byte can be uniquely accessed by a 32-bit address.

The programmer can write assembly language programs without a knowledge of physical address space.

The memory organization model available to applications programmers is determined by the system software designers. The memory organization model available to the programmer for each task can vary between the following possibilities:

- A "flat" address space includes a single array of up to 4 gigabytes. Even though the

physical address space can be up to 4 gigabytes, in reality it is much smaller. The 80386

maps the 4-gigabyte flat space into the physical address space automatically by using an

address translation scheme transparent to the applications programmers.

- A segmented address space includes up to 16,383 linear address spaces of up to 4 gigabytes each. In a segmented model, the address space is called the logical address space and can be up to 2<sup>46</sup> bytes (64 tetrabytes). The processor maps this address space onto the physical address space (up to 4 gigabytes) by an address translation technique.

To applications programmers, the logical address space appears as up to 16,383 onedimensional subspaces, each with a specified length. Each of these linear subspaces is called a segment. A segment is a unit of contiguous address space with sizes varying from one byte up to a maximum of 4 gigabytes.

A pointer in the logical address space consists of a 16-bit segment selector identifying a segment and a 32-bit offset addressing a byte within a segment.

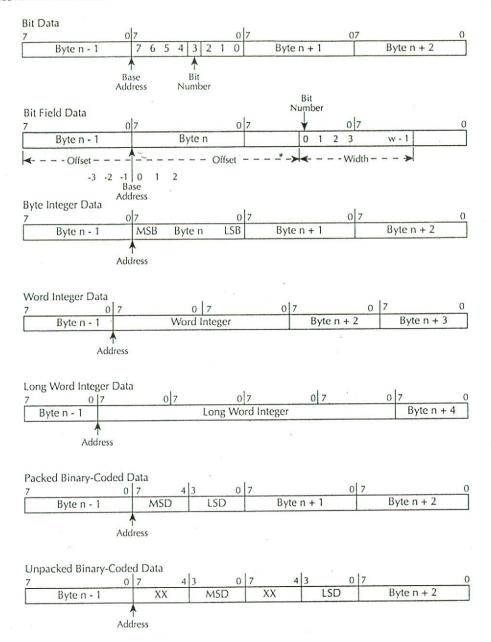

## 4.2.1.b Data Types

Data types can be byte (8-bit), word (16-bit with low byte address n and high byte by address n + 1), and double word (32-bit with byte 0 addressed by address n and byte 3 by address n + 3). All three data types can start at any byte address. Therefore, the words are not required to be aligned at even-numbered addresses and double words need not be aligned at addresses evenly divisible by 4. However, for maximum speed performance, data structures (including stacks) should be designed in such a way that, whenever possible, word operands are aligned at even addresses and double-word operands are aligned at addresses evenly divisible by 4.

Depending on the instruction referring to the operand, the following additional data types are available: integer (signed 8-, 16-, or 32-bit), ordinal (unsigned 8-, 16-, or 32-bit), near pointer (a 32-bit logical address which is an offset within a segment), far pointer (a 48-bit logical address consisting of a 16-bit selector and a 32-bit offset), string (8-, 16-, or 32-bit data from 0 bytes to  $2^{32}-1$  bytes), bit field (a contiguous sequence of bits starting at any bit position of any byte and may contain up to 32 bits), bit string (a contiguous sequence of bits starting at any position of any byte and may contain up to  $2^{32}-1$  bits), and packed/unpacked BCD and ASCII-type data. When the 80386 is interfaced to a coprocessor such as the 80287 or 80387, then floating point numbers (signed 32-, 64-, or 80-bit real numbers) are supported.

## 4.2.1.c 80386 Registers

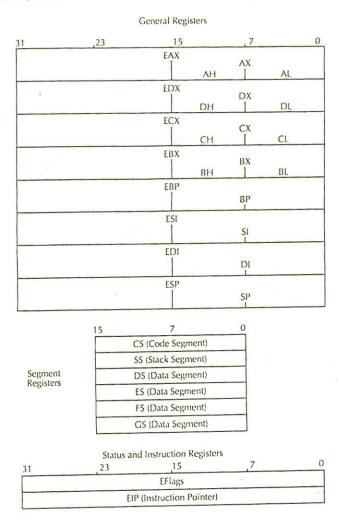

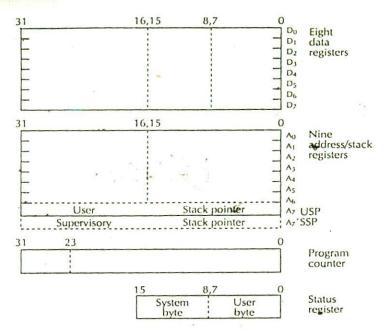

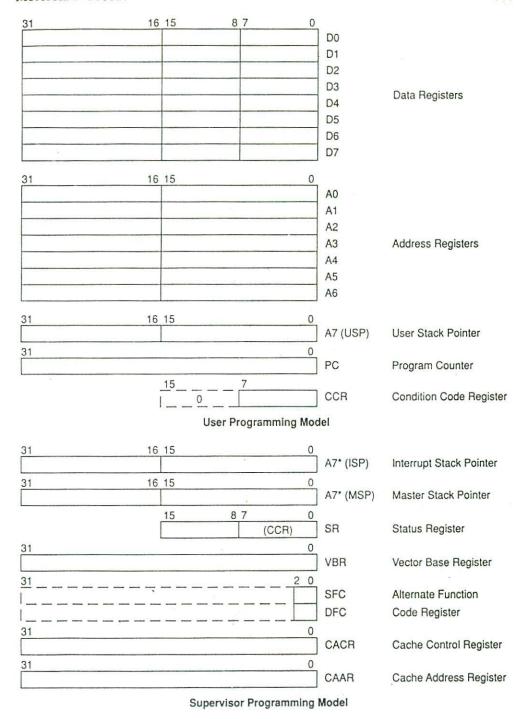

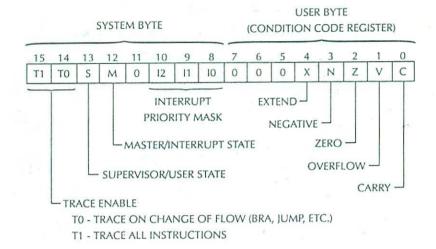

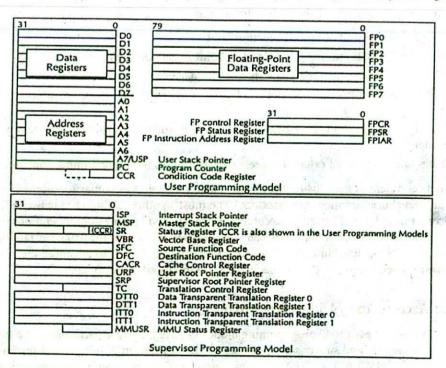

Figure 4.9 shows 80386 registers. The 80386 has 16 registers classified as general, segment, status, and instruction.

The eight general registers are the 32-bit registers EAX, EBX, ECX, EDX, EBP, ESP, ESI, and EDI. The low-order word of each of these eight registers has the 8086/80186/80286 register

FIGURE 4.9 80386 applications register set.

names AX (AH or AL), BX (BH or BL), CX (CH or CL), DX (DH or DL), BP, SP, SI, and DI. They are useful for making the 80386 compatible with the 8086, 80186, and 80286 processors.

The six 16-bit segment registers (CS, SS, DS, ES, FS, and GS) allow systems software designers to select either a flat or segmented model of memory organization. The purpose of CS, SS, DS, and ES is obvious. Two additional data segment registers FS and GS are included in the 80386. The four data segment registers (DS, ES, FS, GS) can access four separate data areas and allow programs to access different types of data structures. For example, one data segment register can point to the data structures of the current module, another to the exported data of a higher level module, another to a dynamically created data structure, and another to data shared with another task.

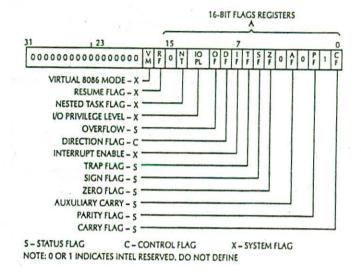

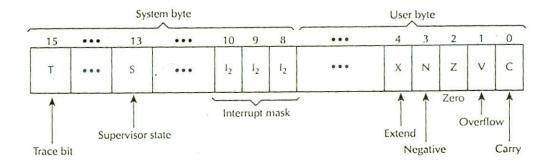

The flag register is a 32-bit register named EFLAGS. Figure 4.10 shows the meaning of each bit in this register. The low-order 16 bits of EFLAGS is named FLAGS and can be treated as

FIGURE 4.10 EFLAGS register.

a unit. This is useful when executing 8086/80186/80286 code, because this part of EFLAGS is the same as the FLAGS register of the 80286/80186/80286. The 80386 flags are grouped into three types: the status flags, the control flags, and the system flags.

The status flags include CF, PF, AF, ZF, SF, and OF as in the 8086/80186/80286. The control flag DF is used by strings as in the 8086/80186/80286. The system flags control I/O, maskable interrupts, debugging, task switching, and enabling of virtual 8086 execution in a protected, multitasking environment. The purpose of IF and TF is identical to the 8086/80186/80286. Let us explain the other flags:

- IOPL (I/O Privilege Level) This is a 2-bit field and supports the 80386 protection feature. The IOPL field defines the privilege level needed to execute I/O instructions. If the present privilege level is less than or equal to IOPL (privilege level is specified by numbers), the 80386 can execute I/O instructions; otherwise it takes a protection exception.

- NT (Nested Task) The NT bit controls the IRET operation. If NT = 0, a usual return from interrupt is taken by the 80386 by popping EFLAGS, CS, and EIP from the stack. If NT = 1, the 80386 returns from an interrupt via task switching.

- RF (Resume Flag) If RF = 1, the 80386 ignores debug faults and does not take another exception so that an instruction can be restarted after a normal debug exception. If RF = 0, the 80386 takes another debug exception to service debug faults.

- VM (Virtual 8086 Mode) When VM bit is set to one, the 80386 executes 8086 programs. When VM bit is zero, the 80386 operates in the protected mode.

The RF, NT, DF, and TF can be set or reset by an 80386 program executing at any privilege level. The VM and IOPL bits can be modified by a program running at only privilege level 0 (the highest privilege level). An 80386 with I/O privilege level can only modify the IF bit. The IRET instruction or a task switch can set or reset the RF and VM bits. The other control bits can also be modified by the POPF instruction.

The instruction pointer register (EIP) contains the offset address relative to the start of the current code segment of the next sequential instruction to be executed. The EIP is not directly accessible by the programmer; it is controlled implicitly by control-transfer instructions, interrupts, and exceptions. The low-order 16 bits of EIP is called IP and is useful when the 80386 executes 8086/80186/80286 instructions.

## 4.2.1.d 80386 Addressing Modes

The 80386 has 11 addressing modes which are classified into register/immediate and memory addressing modes. Register/immediate type includes two addressing modes, while the memory addressing type contains the other nine modes.

Register/Immediate Modes — Instructions using these register or immediate modes operate on either register or immediate operands.

Register Mode — The operand is contained in one of the 8, 16, or 32-bit general registers. An example is DEC ECX which decrements the 32-bit register ECX by one.

- ii) Immediate Mode The operand is included as part of the instruction. An example is MOV EDX, 5167812FH which moves the 32-bit data 5167812F<sub>16</sub> to EDX register. Note that the source operand in this case is in immediate mode.

- 2. Memory Addressing Modes The other 9 addressing modes specify the effective memory address of an operand. These modes are used when accessing memory. An 80386 address consists of two parts: a segment base address and an effective address. The effective address is computed by adding any combination of the following four components:

- Displacement: 8- or 32-bit immediate data following the instruction; 16-bit displacements can be used by inserting an address prefix before the instruction.

- Base: The contents of any general-purpose register can be used as base. Compilers normally use these base registers to point to the beginning of the local variable area.

- Index: The contents of any general-purpose register except ESP can be used as an

index register. The elements of an array or a string of characters can be accessed via

the index register.

Scale: The index register's contents can be multiplied (scaled) by a factor of 1, 2, 4, or 8. Scaled index mode is efficient for accessing arrays or structures.

The nine memory addressing modes are a combination of the above four elements. Of these nine modes, eight of them are executed with the same number of clock cycles, since the Effective Address calculation is pipelined with the execution of other instructions; the mode containing base, index, and displacement components requires additional clocks.

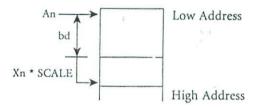

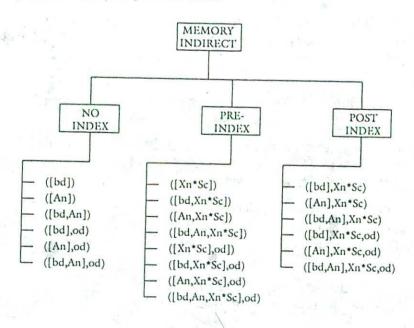

As shown in Figure 4.11, the Effective Address (EA) of an operand is computed according to the following formula:

## EA = Base reg + (Index Reg \* Scaling) + Displacement

- Direct Mode The operand's effective address is included as part of the instruction as an 8-, 16-, or 32-bit displacement. An example is DEC WORDPTR [4000H].

- Register Indirect Mode A base or index register contains the operand's effective address. An example is MOV EBX, [ECX].

- Based Mode The contents of a base register are added to a displacement to obtain the operand's effective address. An example is MOV [EDX + 16], EBX.

Index Mode — The contents of an index register are added to a displacement to obtain the operand's effective address. An example is ADD START [EDI], EBX.

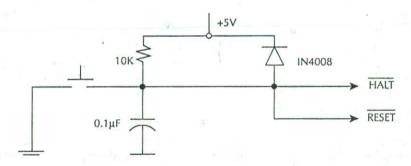

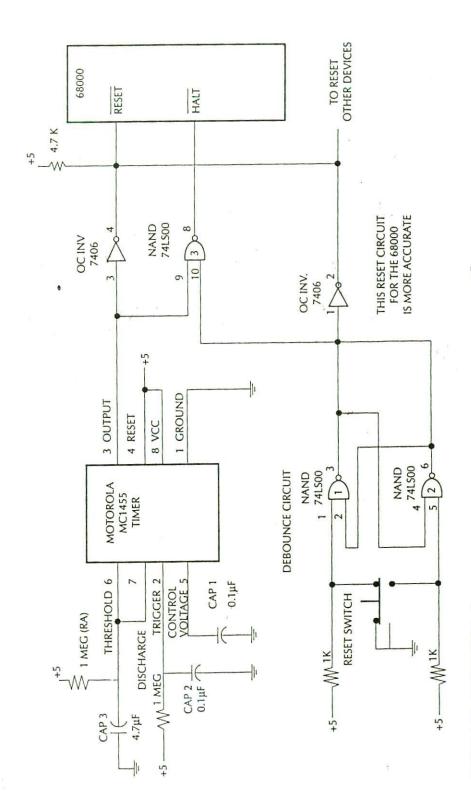

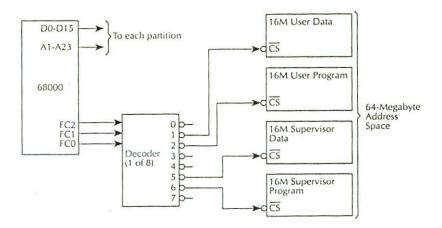

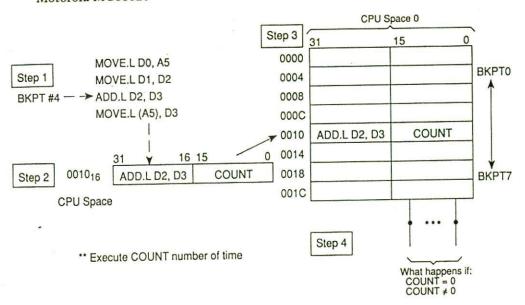

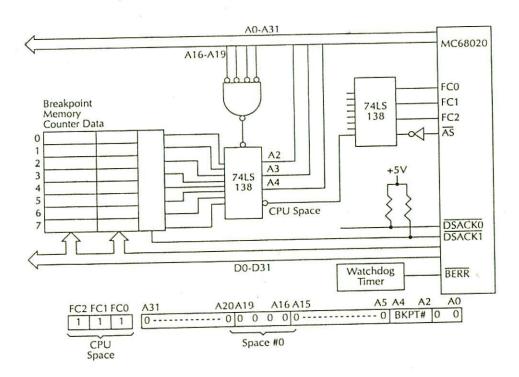

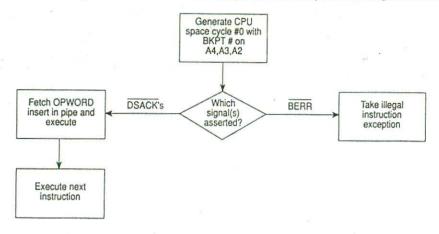

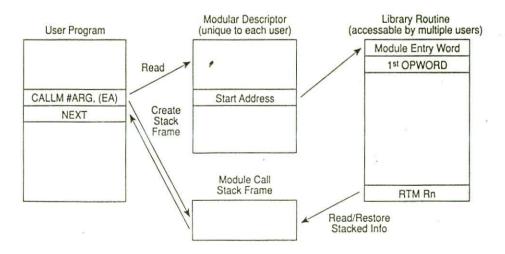

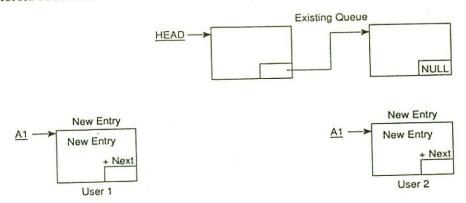

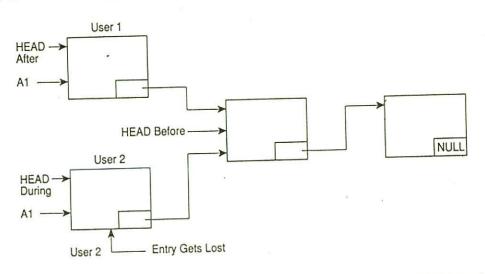

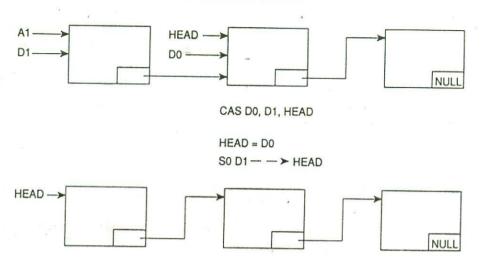

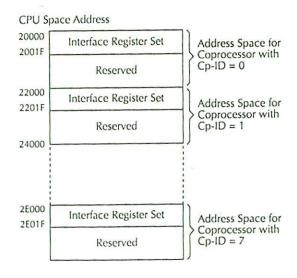

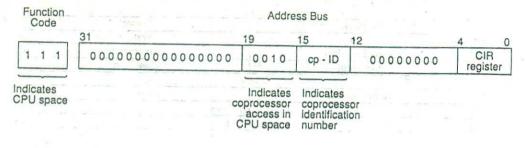

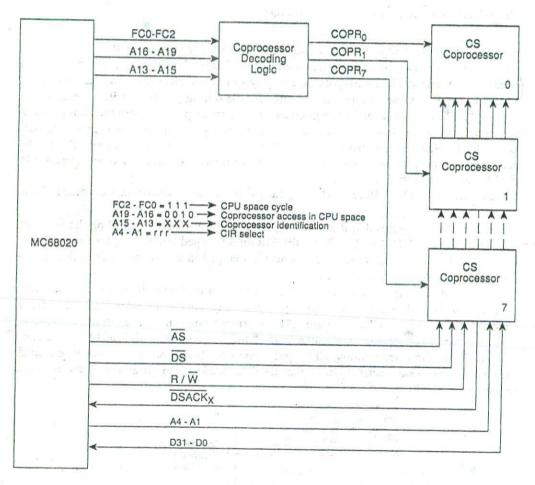

- Scaled Index Mode The contents of an index register are multiplied by a scaling factor (1, 2, 4, or 8) which is added to a displacement to obtain the operand's effective address. An example is MOV START [EBX \* 8], ECX.