# INTRODUCTION TO MICROPROCESSORS AND MICROCOMPUTER-BASED APPLICATIONS

This chapter provides a brief summary of the features of microprocessors and microcomputerbased applications.

The basic elements of a computer are the Central Processing Unit (CPU), the Memory, and Input/Output (I/O) units. The CPU translates instructions, performs arithmetic or logic operations, and temporarily stores instructions and data in its internal high-speed registers. The memory stores programs and data. The I/O unit interfaces the computer with external devices such as keyboard and display.

With the advent of semiconductor technology, it is possible to integrate the CPU in a single chip. The result is the microprocessor. Metal Oxide Semiconductor (MOS) technology is typically used to fabricate the standard off-the-shelf microprocessors such as those manufactured by Intel and Motorola. Appropriate memory and I/O chips are interfaced to the microprocessor to design a microcomputer. Single-chip microcomputers are also available in which the microprocessor, memory, and I/O are all fabricated in the same chip. These single-chip microcomputers offer limited capabilities. However, they are ideal for certain applications such as peripheral controllers.

Single chip microcomputers are also referred to as "microcontrollers". The microcontrollers are typically used for dedicated applications such as automotive systems, home appliances and home entertainment systems. Typical microcontrollers, therefore, include on-chip timers, A/D (Analog to Digital) and D/A (Digital to Analog) converters. Two popular microcontrollers are Intel 8751 (8-bit)/8096 (16-bit) and Motorola HC11 (8-bit)/HC16 (16-bit). The 16-bit microcontrollers include more on-chip ROM, RAM, and I/O compared to the 8-bit microcontrollers.

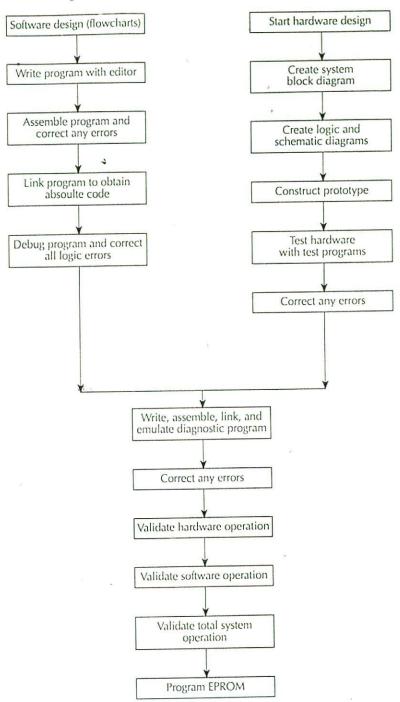

The efficient development of microprocessor-based systems necessitates the use of a microcomputer development system. The microcomputer development system is used for the design, debugging, and sometimes the documentation of a microprocessor-based system.

This chapter first covers the evolution of 8-, 16-, and 32-bit microprocessors along with an overview of programming languages, microcomputer hardware, and software. The attributes of typical microcomputer development systems features as well as some specific microprocessor applications are also included.

## 1.1 Evolution of the Microprocessor

Intel Corporation introduced the first microprocessor, the 4004 (4-bit), in 1971. The 4004 evolved from a development effort while designing a calculator chip set.

Soon after the 4004 appeared in the commercial market, three other microprocessors were introduced. These were the Rockwell International 4-bit PPS-4, the Intel 8-bit 8008, and the National Semiconductor 16-bit IMP-16.

The microprocessors introduced between 1971 and 1973 were the first-generation systems. They were designed using the PMOS (P-type MOS) technology. This technology provided low cost, slow speed, and low output currents and was not compatible with TTL (Transistor Transistor Logic).

After 1973, second-generation microprocessors such as MOS Technology 6502, Motorola 6800 and 6809, Intel 8085, and Zilog Z80 evolved. These 8-bit processors were fabricated using the NMOS (N-type MOS) technology. The NMOS process offers faster speed and higher density than PMOS and is TTL-compatible.

After 1978, the third-generation microprocessors were introduced. These processors are 16 bits wide (16-bit ALU) and include typical processors such as Intel 8086/80186/80286 and Motorola 68000/68010. These microprocessors were designed using the HMOS (high-density MOS) technology. HMOS provides the following advantages over NMOS:

· Speed-Power-Product (SPP) of HMOS is four times better than NMOS:

NMOS = 4 Picojoules (PJ) HMOS = 1 Picojoule (PJ)

Note that Speed-Power-Product

- = speed \* power

- = nanosecond \* milliwatt

- = picojoules

- Circuit densities provided by HMOS are approximately twice those of NMOS:

NMOS =  $4128 \text{ gates/}\mu\text{m}^2$

$HMOS = 1852.5 \text{ gates/}\mu\text{m}^2$

where 1  $\mu$ m (micrometer) = 10<sup>-6</sup> meter.

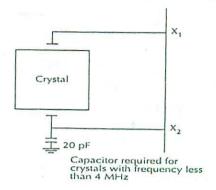

Later, Intel utilized the HMOS technology to fabricate the 8085A. Thus, Intel offers a highspeed version of the 8085A called 8085AH. The price of the 8085AH is higher than the 8085A.

In 1980, fourth-generation microprocessors evolved. Intel introduced the first commercial 32-bit microprocessor, the problematic Intel 432. This processor was eventually discontinued by Intel. Since 1985, more 32-bit microprocessors have been introduced. These include Motorola's MC 68020/68030/68040/PowerPC, Intel's 80386/80486 and the Intel Pentium processor. These processors are fabricated using the low-power version of the HMOS technology called the HCMOS.

The performance offered by the 32-bit microprocessor is more comparable to that of superminicomputers such as Digital Equipment Corporation's VAX11/750 and VAX11/780. Both Intel and Motorola introduced 32-bit RISC (Reduced Instruction Set Computer) microprocessors, namely the Intel 80960 and Motorola MC88100/PowerPC with simplified instruction sets. Note that the purpose of RISC microprocessors is to maximize speed by reducing clock cycles per instruction. Almost all computations can be obtained from a simple instruction set.

RISC microprocessors have hardwired instruction sets like the non-RISC microprocessors such as the Intel 8085 and MOS 6502. This means that for every instruction, there exists actual, physical connections that provide the desired instruction decoding. The microprocessor,

therefore, does not use valuable clock cycles (machine cycles) in instruction decoding. Most RISC instructions require a maximum of only two clock cycles to complete. These instructions are restricted to register-to-register operations with load and store for memory access. Since RISC-type microprocessors are hardwired, instructions may be executed simultaneously (as long as the instructions do not share the same register.) This technique is known as pipelining.

Pipelining is the mechanism that actually enables simultaneous processing to occur. Instructions are fetched in sequential order. The processor continues to fetch instructions even though it has not executed the present instruction. This provides an input pipeline to the instruction cache. At this stage, the instructions are intelligently fed into the instruction execution unit for processing. When an instruction is executed, the registers used by the instruction clear respective bits in a scoreboard register. As the microprocessor is executing a given instruction, it checks the scoreboard register to see if the next instructions (residing in a fast read/write memory internal to the microprocessor called the instruction cache) use registers that are currently in use. Instructions not using the same registers can therefore be executed at the same time. The RISC microprocessors can execute as many as five instructions simultaneously.

The trend in microprocessors is implementation of more on-chip functions and for improvement of the speeds of memory and I/O devices. Some manufacturers are speeding up the processors for data crunching type applications. Digital Equipment Corporation's Alpha 21164 with 300 MHz clock, four instruction-per-cycle rate and RISC-based architecture is the fastest microprocessor available today.

## 1.2 Microprocessor Data Types

This section discusses the data types used by microprocessor. Typical data types include signed and unsigned binary integers, binary coded decimal (BCD), American Standard Code for Information Interchange (ASCII) and floating-point numbers. Note that binary integer numbers do not support fractions in microprocessors. Fractions and mixed numbers (numbers comprised of integers and fractions) use either binary or BCD floating-point formats. Floating-point numbers are often referred to as real numbers.

## 1.2.1 Unsigned and Signed Binary Integers

An unsigned binary integer has no arithmetic sign. Unsigned binary numbers are therefore always positive. An example is memory address which is always a positive number. An 8-bit unsigned binary integer represents all numbers from  $00_{16}$  through FF<sub>16</sub> ( $0_{10}$  through 255<sub>10</sub>).

A signed binary integer, on the other hand, includes both positive and negative numbers. It is represented in true form for a positive number and in two's complement form for a negative number. For example, the decimal number +10 can be represented as a true form 8-bit number in a microprocessor as 0000 1010 (binary) or 0A (hexadecimal). The decimal number -10 can be represented in two's complement form as 1111 0110 (binary) or F6 (hexadecimal). The most significant bit of a signed binary number represents the sign of the number. For example, bit 7 of an 8-bit signed number, bit 15 of a 16-bit signed number and bit 31 of a 32-bit signed number represent the signs of the respective numbers. A 32-bit signed binary integer includes all numbers from -2,147,483,648 to 2,147,483,647 with 0 being a positive number.

Finally, note that the hexadecimal number  $FF_{16}$  is  $255_{10}$  when represented as an unsigned number. On the other hand,  $FF_{16}$  is  $-1_{10}$  when represented as a signed number.

## 1.2.2 BCD (Binary Coded Decimal) Numbers

A BCD digit consists of four bits with a value ranging from 0000<sub>2</sub> to 1001<sub>2</sub> (0 through 9 decimal). A BCD digit greater than 9<sub>10</sub> can be represented as two or more BCD digits.

Microprocessors store BCD numbers in two forms, packed and unpacked. The unpacked BCD number represents each BCD digit as a byte while the packed BCD number represents two BCD digits in a byte. For example, 23<sub>10</sub> is represented as 0000 0010 0000 0011<sub>2</sub> as two unpacked BCD numbers, while it is represented as 0010 0011<sub>2</sub> as a packed BCD number.

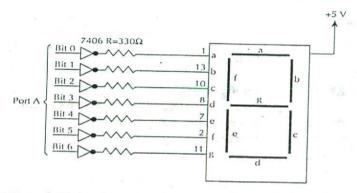

Microprocessors normally input data from a keypad in unpacked BCD form. This data can then be converted by writing a program in the microprocessor to packed BCD form for arithmetic operations or for storing in memory. After processing, the packed BCD result is then converted to unpacked BCD form by another microprocessor program written by the user for displays. Typical displays use either unpacked BCD data or unpacked BCD data converted to seven segment code by the microprocessor's program.

#### 1.2.3 **ASCII**

ASCII (American Standard Code for Information Interchange) is a code that represents alphanumeric (alpha characters and numbers) in a microcomputer's memory. ASCII also represents special symbols such as # and %. It is a 7-bit code. The most significant bit (bit 7) is sometimes used as a parity bit. The parity bit represents the number of ones in the byte. If the number of ones is odd, the parity is odd; otherwise, the parity is even.

Also, note that the hexadecimal numbers 30<sub>16</sub> through 39<sub>16</sub> are ASCII codes representing the decimal numbers 0 through 9. A listing of the ASCII codes is included in Appendix F.

#### 1.2.4 Floating-Point Numbers

Floating-Point numbers contain three components. These are a sign, exponent and mantissa. For example, consider the decimal value -2.5 x 10<sup>-2</sup>. The sign is negative, the exponent is -2 and the significand or mantissa is 2.5. In floating point numbers, it is possible to store the same number in several different ways. For example, 1 can be represented as 10.0 x 10<sup>-1</sup>, 1.0 x 10<sup>0</sup>, 0.1 x 101 and 0.01 x 102. To make computations yield the maximum accuracy, the numbers are normalized. This means that the exponent is adjusted so that the mantissa always follows a specific format. A binary floating point number is represented as a normalized binary fraction raised to a power of 2. To convert a binary number to its standard floating-point form, the binary number is converted to a normalized floating-point number. Note that a normalized binary floating-point number is represented as 1.XXXXXX raised to some power of 2 where X can be 0 or 1. The 1. part is implied and is not stored by the microprocessor. First, the binary number is converted to a common 32-bit floating-point format. The most significant bit (bit 31) is the sign bit (S). If S is zero, the number is positive, while if S is one, the number is negative. The next 8 bits contain the biased exponent. This means that an 8-bit number 7F<sub>16</sub> or 127<sub>10</sub> is added to the exponent. Biased exponent makes numeric comparison (such as less than or greater than) easy. The bias is usually chosen such that the most negative number allowed in the exponent becomes zero and the most positive number becomes the largest value of the representation. For example, with an 8-bit exponent, and +12710 bias, the smallest and the largest values of the bias exponent are 010 and 25510 respectively. Note that the zero biased exponent is represented as 12710, while the unbiased minimum and maximum values of the 8bit exponent are -12710 and +12810 respectively. The remaining 23 bits represent the fractional part of the number. Note that zero is stored as 32 zeros while infinity is stored as 32 ones. As an example, consider converting the decimal number 10 to the standard floating-point format as follows:

- 1.  $10_{10} = 1010_2$

- 2. Normalize the binary number as 1.XXXXXX x  $2^n = 1.010 \times 2^3$

- 3. Sign, S = 0 for positive

- 4. Biased exponent =  $7F_{16} + 3 = 82_{16}$

- 5. 23-bit Fraction = 0100 0000 0000 0000 0000 0000

- 6. The floating-point equivalent of 1010 is

- S Exponent Fraction

- 0 1000 0010 0100 0000 0000 0000 0000 0000

A special case of the floating-point format is called NaN (Not a Number). NaNs are results generated by floating-point operations that have no mathematical interpretations. These results may be generated by operations such as multiplication of infinity by infinity.

The BCD floating-point form represents a number in BCD scientific notation. The number is represented as normalized significand raised to some power of 10. Each BCD floating-point number is represented in typical microprocessors as 80 bits. The BCD fraction is 16 digits wide (64-bit) and is stored as packed BCD digits. The whole number portion of the significand is stored as one digit BCD from 0 to 9. The BCD exponent along with the sign is expressed as 12 bits.

Typical floating-point coprocessors such as 80387 (for the Intel 80386 microprocessor) and 68881/68882 (for the Motorola 68020/68030 microprocessor) support several data types. For example, the 80387 coprocessor supports seven data types. These are word integer (16-bits), short integer (32-bit), long integer (64-bit), packed BCD (80-bit), short real (32-bit), long real (64-bit), and temporary real (80-bit).

The 80387 integer data types are represented by the two's complement same as those used by the 80386. The only difference is that the 80386 supports an 8-bit integer while the 80387 supports a 64-bit integer.

The 80387 supports 80-bit packed BCD with 18 decimal digits (bits 0-71), bit 79 as the sign-bit and seven (bits 72-78) unused bits. With 18-digits representation, the COBOL standard (the High level language utilizing BCD) is followed.

The 80387 supports three real data formats. These are short real (32-bit with one sign bit, 8-bit exponent and 23-bit significand), long real (64-bit with one sign-bit, 11-bit for exponent and 62-bit for the significand), temporary real (80-bit with one sign-bit, 15-bit exponent, and 64-bit significand).

The 80387 uses the temporary real format internally. All data types are converted by the 80387 immediately into temporary real. This is done to maximum precision and range of computations.

The 80387 supports four special cases. These are zeros, infinities (both positive and negative), denormals, and NaNs (signalling and quiet).

Denormals represent very small numbers that are not normalized. Normally, numbers are required to be normalized by shifting to left until the most significant is one. Denormals do not have one as the most significant bit of the significand. Denormals permit a gradual underflow. That is the precision is lost gradually rather than abruptly. When the least normalizable number is reached, the next small representation is zero. Denormals provide gradual underflow of numbers that are not normalized. That is, denormals extend the range of very small numbers significantly, but with some loss in precision.

A signaling NaN causes an invalid operation exception when used in an operation. A quiet NaN, on the other hand, does not cause an invalid operation exception.

The floating-point data types supported by the Motorola 68881/68882 floating-point coprocessors are summarized next. Note that the 68881 and 68882 differ in execution speed. They are basically identical. The 68882 is an enhanced version of the 68881 in that it executes several floating-point instructions concurrently with the 68020/68030. The 68881/68882 supports integers, binary floating-point numbers, and packed floating-point BCD. Data are represented externally by using these formats. The 68881/68882 utilizes an 80-bit binary floating point form to represent all data internally.

The 68881/68882 supports three signed integer formats. These are 8-bit byte, 16-bit word, and 32-bit long word.

1

Binary floating-point format is also called binary real form. The 68881/68882 supports binary floating-point form which contains three fields. These are a sign, biased exponent and a significand. The 68881/68882 operates on these sizes, namely 32-bit single-precision, 64-bit double precision, and 96-bit extended precision.

For single precision (bit 31: sign bit, bits 23-30: 8-bit exponent, bits 0-22: 23-bit significand), 64-bit double precision (bit 63: sign bit, bits 62-52: 11-bit exponent, bits 0-51: 52-bit significand), and 96-bit extended-precision (bit 95: sign bit, bits 80-94: 15-bit exponent, bits 64-79: zero; sixteen unused bits, bits 0-63: 64-bit significand).

The biased exponent is used. The Single Precision adds a bias of 127<sub>10</sub> (7F<sub>16</sub>), double Precision uses a bias of 1023<sub>10</sub> (3FF<sub>16</sub>), and the extended-Precision uses a bias of 16383<sub>10</sub> (3FFFF<sub>16</sub>). The bias is added to the exponent before it is stored in this format and subtracted to convert to a true exponent when the number is interpreted.

A few special cases that do not conform to the floating-point form are also handled by the 68881/68882. For example, a zero is represented with all bits of the exponent and significand as zeros. The sign bit may be a one or a zero representing +0 or -0. The infinity, on the other hand is represented by all bits in the exponent and significand set to ones. The sign bit may be zero or one representing positive or negative infinity. The 68881/68882 supports BCD floating point form which represent each number as normalized significand raised to a power of 10. This format stores a number as 96 bits. The least significant 64 bits (8 bytes) contain the 16-digit BCD fraction. The next byte contains the whole number portion of the significand (0-9). The most significant bit (bit 95) contains the sign of significand while bit 94 includes the sign of the exponent. The exponent is represented by three digit BCD packed exponent (000-999) in bits 80–91. Similar to the 80387, the 68881/68882 also represents NaN's and also provides exceptions for signaling NaN's.

IEEE has established the standard for floating-point arithmetic specified by ANSI-IEEE754-1985. Typical 32-bit microprocessors use this standard.

## 1.3 Microcomputer Hardware

In this section, some unique features associated with various microcomputer components will be described.

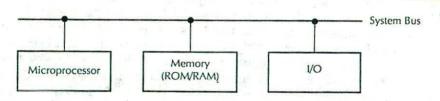

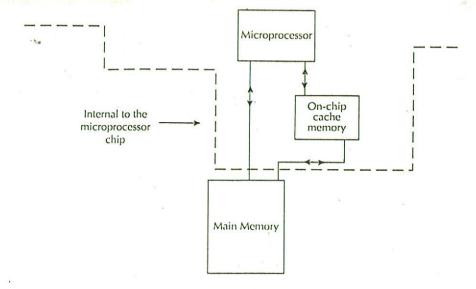

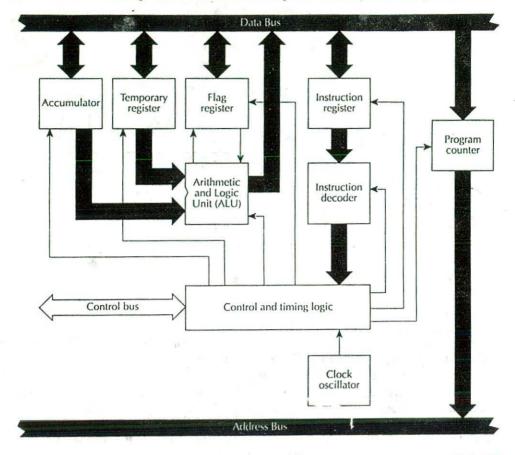

The microcomputer contains a microprocessor, a memory unit, and an input/output unit. These elements are explained in the following in detail. Figure 1.1 shows a simplified block diagram of a microcomputer.

## 1.3.1 The System Bus

The system bus contains three buses. These are the address bus, the data bus, and the control bus. These buses connect the microprocessor to each of the memory and I/O elements so that information transfer between the microprocessor and any of the other elements can take place.

FIGURE 1.1 Simplified block diagram of a microprocessor.

On the address bus, information transfer normally takes place only in one direction, from the microprocessor to the memory or I/O elements. Therefore, this is called a unidirectional bus. This bus is usually 16 to 32 bits wide. The number of unique addresses that the microprocessor can generate on this bus depends on the width of this bus. For example, for a 16-bit address bus, the microprocessor can generate 2<sup>16</sup> = 65,536 different possible addresses. A different memory location or an I/O element can be represented by each one of these addresses.

The data bus is a bidirectional bus, that is, information can flow in both directions, to or from the microprocessor. This bus is normally 8, 16, or 32 bits wide.

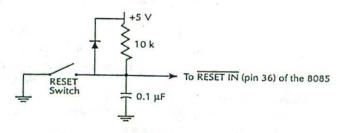

The control bus is used to transmit signals that are used to synchronize the operation of the individual microcomputer elements. Typical control signals include READ, WRITE, and RESET. Some signals on the control bus such as interrupt signals are unidirectional, while some others such as RESET may be bidirectional.

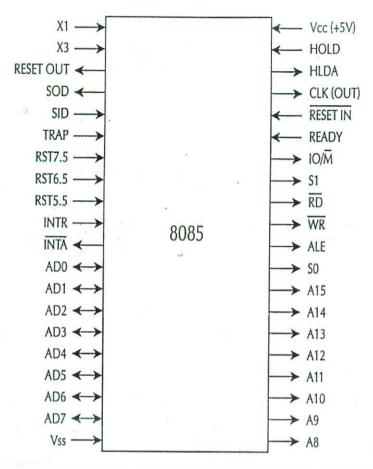

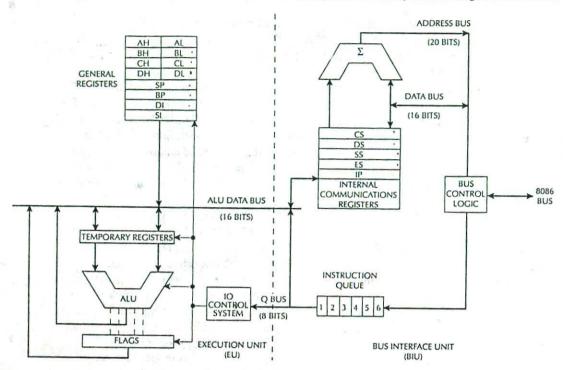

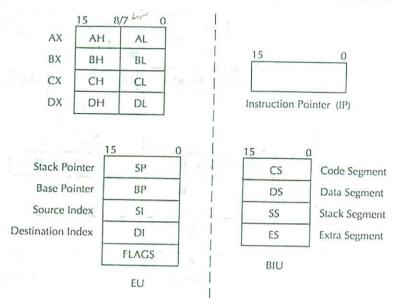

#### 1.3.2 The Microprocessor

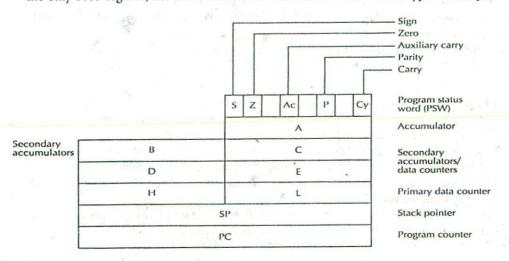

The commercial microprocessor, fabricated using the MOS technology, is normally contained in a single chip. The microprocessor is comprised of a register section, one or more ALUs (Arithmetic Logic Units), and a control unit. Depending on the register section, the microprocessor can be classified either as an accumulator-based or a general-purpose register-based machine.

In an accumulator-based microprocessor such as the Intel 8085 and Motorola 6809, one of the operands is assumed to be held in a special register called the "accumulator". All arithmetic and logic operations are performed using this register as one of the data sources. The result after the operation is stored in the accumulator. One-address instructions are very predominant in this organization. Eight-bit microprocessors are usually accumulator-based.

The general-purpose register-based microprocessor is usually popular with 16- and 32-bit microprocessors, such as Intel 8086/80386/80486 and Motorola 68000/68020/68030/68040, and is called general-purpose, since its registers can be used to hold data, memory addresses, or the results of arithmetic or logic operations. The number, size, and types of registers vary from one microprocessor to another. Most registers are general-purpose registers, while some are provided with dedicated functions.

Typical dedicated registers include the Program Counter (PC), the Instruction Register (IR), Status Register (SR), the Stack Pointer (SP) and the Index Register. The 32-bit microprocessors include special on-chip combinational network called the Barrel Shifter.

The PC normally contains the address of the next instruction to be executed. Upon activating the microprocessor chip's RESET input, the PC is normally initialized with the address of the first instruction. For example, the 80486, upon hardware reset, reads the first instruction from the 32-bit address FFFFFFF0<sub>16</sub>. In order to execute the instruction, the microprocessor normally places the PC contents on the address bus and reads (fetches) the first instruction from external memory. The program counter contents are then automatically incremented by the ALU. The microcomputer thus executes a program sequentially unless it encounters a jump or branch instruction. The size of the PC varies from one microprocessor to another depending on the address size. For example, the 68000 has a 24-bit PC, while the 68040 contains a 32-bit PC.

The instruction register (IR) contains the instruction to be executed. After fetching an instruction from memory, the microprocessor places it in the IR for translation.

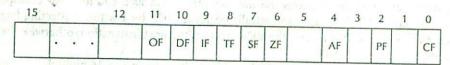

The status register contains individual bits with each bit having a special meaning. The bits in the status register are called flags. Each flag is usually set or reset by an ALU operation. The flags are used by the Conditional Branch instructions. Typical flags include carry, sign, zero, and overflow.

The carry (C) flag is used to reflect whether or not an arithmetic operation such as ADD generates a carry. The carry is generated out of the 8th bit (bit 7) for byte operations, 16th bit (bit 15) for 16-bit, or 32nd bit (bit 31) for 32-bit operations. The carry is used as the borrow flag for subtraction. In multiple word arithmetic operations, any carry from a low-order word must be reflected in the high-order word for correct results.

The zero (Z) flag is used to indicate whether the result of an arithmetic or logic operation is zero. Z = 1 for a zero result and Z = 0 for a non-zero result. The sign flag (sometimes also called the negative flag) indicates whether a number is positive or negative. S = 1 indicates a negative number if the most significant bit of the number is one; S = 0 indicates a positive number if the most significant bit of the number is zero.

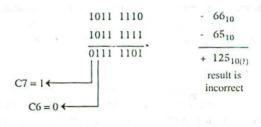

The overflow (V) flag is set to one if the result of an arithmetic operation on signed (two's complement) numbers is too large for the microprocessor's maximum word size; the C flag is overflow for unsigned numbers. The overflow flag for signed 8-bit numbers can be shown as  $V = C7 \oplus C6$ , where C7 is the final carry and C6 is the previous bit's carry. The  $\oplus$  symbol indicates exclusive-OR operation. This can be illustrated by the numerical examples shown below:

$$\begin{array}{c}

0000 \ 0100 \\

+ \ 0000 \ 0010 \\

\hline

C7 = 0 & 0000 \ 0110 \\

\hline

C6 = 0 & 0 & 6_{10}

\end{array}$$

From the above, the result is correct when C6 and C7 have the same values (0 in this case). When C6 and C7 are different, an overflow occurs. For example, consider the following:

The result is incorrect. Since  $V = C6 \oplus C7 = 0 \oplus 1 = 1$ , the overflow flag is set. Note that this applies to signed two's complemented numbers only.

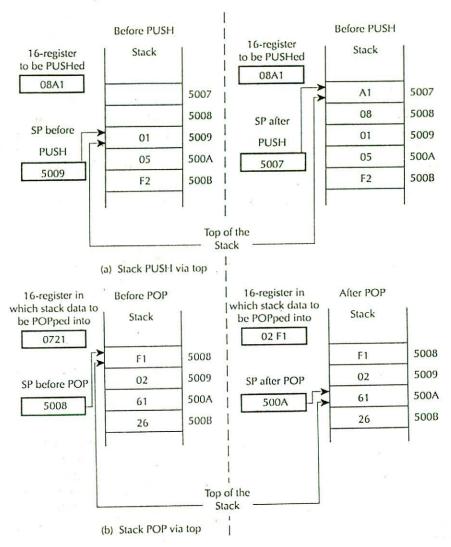

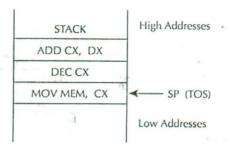

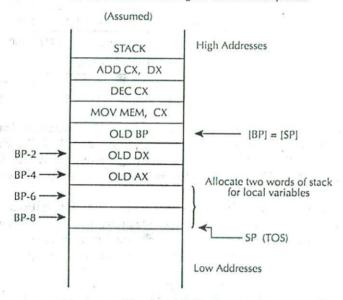

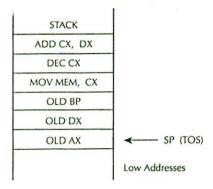

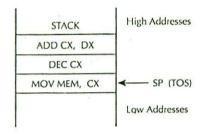

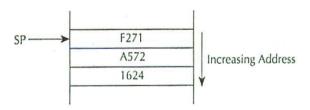

The stack pointer (SP) register addresses the stack. A stack is Last-In First-Out (LIFO) read/ write memory in the sense that items that go in last will come out first. This is because stacks perform all read (POP) and write (PUSH) operations from one end.

The stack is addressed by a register called the stack pointer (SP). The size of the SP is dependent on the microprocessor's address size. The stack is normally used by subroutines or interrupts for saving certain registers such as the program counter.

Two instructions, PUSH (stack write) and POP (stack read), can usually be performed by the programmer to manipulate the stack. If the stack is accessed from the top, the stack pointer is decremented before a PUSH and incremented after a POP. On the other hand, if the stack is accessed from the bottom, the SP is incremented before a PUSH and decremented after a POP. Typical microprocessors access the stack from the top. Depending on the microprocess-

FIGURE 1.2 PUSH and POP operations via top.

sor, an 8-, 16-, or 32-bit register can be pushed onto or popped from the stack. The value by which the SP is incremented or decremented after POP or PUSH operations depends on the register size. For example, values of one for an 8-bit register, two for 16-bit registers, and four for 32-bit registers are used. Figure 1.2 shows the stack data when accessed from the top before and after PUSHing a 16-bit register onto the stack or POPping 16 bits from the stack into the 16-bit register. Note that stack items PUSHed must be POPped in reverse order. The item pushed last must be popped first.

Consider the PUSH operation in Figure 1.2a when the stack is accessed from the top. The SP is decremented by 2 after the PUSH. The SP is decremented since it is accessed from the top. A decrement value of 2 is used since the register to be pushed is 16 bits wide.

The POP operation shown in Figure 1.2b is the reverse of the PUSH. The SP is incremented after POP. The contents of locations 5008<sub>16</sub> and 5009<sub>16</sub> are assumed to be empty.

An index register is typically used as a counter for an instruction or for general storage functions. The index register is useful with instructions where tables or arrays of data are accessed. The general-purpose register-based microprocessor can use any general-purpose register as the index register.

Typical 32-bit microprocessors such as the Intel 80386/80486 and Motorola 68020/68030/68040 include a special type of shifter called barrel shifter for performing fast shift operations.

The barrel shifter is an on-chip combinational network for 32-bit microprocessors and provides fast shift operations. For example, the 80386 barrel shifter can shift a number from 0 through 64 positions in one clock period (clock rate is 16.67 MHz).

The ALU in the microprocessor performs all arithmetic and logic operations on data. The size of the ALU defines the size of the microprocessor. For example, Intel 8086 (or Motorola 68000) is a 16-bit microprocessor since its ALU is 16 bits wide. The Intel 8088 (or Motorola 68008) is also a 16-bit microprocessor since its ALU is 16 bits wide, even though its data bus is 8 bits wide. Motorola 68040 (or Intel 80486) is a 32-bit microprocessor since its ALU is 32 bits wide. The ALU usually performs operations such as binary addition and subtraction. The 32-bit microprocessors include multiple ALUs for parallel operations and thus achieve fast speed.

The control unit of the microprocessor performs instruction interpreting and sequencing. In the fetch phase, the control unit reads instructions from memory using the PC as a pointer. It then recognizes the instruction type, gets the necessary operands, and routes them to the appropriate functional units of the execution unit. Necessary signals are issued to the execution unit to perform the desired operations, and the results are routed to the specified destination.

In the sequencing phase, the control unit determines the address of the next instruction to be executed and loads it into the PC. The control unit is typically designed using one of three techniques:

- · Hardwired control

- · Microprogramming

- Nanoprogramming

The hardwired control unit is designed by physically connecting typical components such as gates and flip-flops. Typical 32-bit RISC microprocessors such as the Intel 80960 and Motorola 88100 are designed using hardwired control. The microprogrammed control unit includes a control ROM for translating the instructions. Intel 8086 is a microprogrammed microprocessor. Nanoprogramming includes two ROMs inside the control unit. The first ROM (microROM) stores all the addresses of the second ROM (nanoROM). If the microinstructions (which is the case with the 68000/68020/68030/68040) repeat many times in a microprogram, use of two-level ROMs provides tremendous memory savings. This is the reason that the control units of the 68000, 68020, 68030, and 68040 are nanoprogrammed.

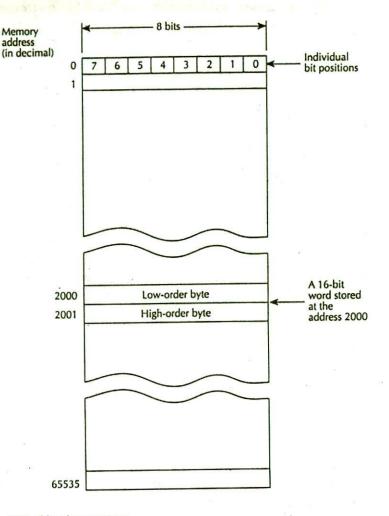

## 1.3.3 Memory Organization

#### 1.3.3.a Introduction

A memory unit is an integral part of any microcomputer system and its primary purpose is to hold programs and data.

In a broad sense, a microcomputer memory system can be logically divided into three groups:

- · Processor memory

- · Primary or main memory

- Secondary memory

Processor memory refers to the microprocessor registers. These registers are used to hold temporary results when a computation is in progress. Also, there is no speed disparity between these registers and the microprocessor because they are fabricated using the same technology.

However, the cost involved in this approach forces a microcomputer architect to include only a few registers (usually 8 or 16) in the microprocessor.

Primary or main memory is the storage area in which all programs are executed. The microprocessor can directly access only those items that are stored in primary memory. Therefore, all programs and data must be within the primary memory prior to execution.

Secondary memory refers to the storage medium comprising slow devices such as magnetic tapes and disks. These devices are used to hold large data files and huge programs such as compilers and data base management systems which are not needed by the processor frequently. Sometimes secondary memories are also referred to as auxiliary or backup store or virtual memory.

Secondary memory stores programs and data in excess of the main memory. The microcomputer cannot directly execute programs stored in the secondary memory. In order to execute these programs, the microcomputer must transfer them to its main memory by a system program called the operating system. This topic is covered later in the chapter.

Data in disk memories are stored in tracks. A track is a concentric ring of data stored on a surface of a disk. Each track is further subdivided into several sectors. Each sector typically stores 512 or 1024 bytes of data. All disk memories use magnetic media except the optical disk memory which stores data on a plastic disk. Data is read or sometimes written on the optical disk with a laser beam. There are two types of optical disks. These are the CD-ROM (Compact Disk Read Only Memory) and the WORM (Write Once Read Many). The CD-ROM is inexpensive compared to the WORM drive. However it suffers from lack of speed and has limited software applications at the present time. The WORM drive is typically used in huge data storing applications such as insurance and banking since data can be written only once. The optical disk memory is currently becoming popular with microcomputer systems. One of the commonly used disk memories with microcomputer systems is the floppy or flexible disk. The floppy disk is a flat, round piece of plastic coated with magnetically sensitive oxide material. The disk is provided with a protective jacket to prevent fingerprints or foreign matter from contaminating the disk's surface. The floppy disk is available in three sizes. These are the 8 inch, 5.25 inch, and 3.5 inch. The 8 inch floppy disk is not used in present systems. These days, the 5.25 inch and 3.5 inch are very popular. Also, the 3.5 inch floppy is replacing the 5.25 inch floppy in newer systems since it is smaller in size and does not bend easily. All floppy disks are provided with an off-center index hole that allows the electronic system reading the disk to find the start of a track and the first sector.

Hard disk memory is also frequently used with microcomputer systems. The hard disk, also known as the fixed disk, is not removable like the floppy disk.

A comparison of the some of the features associated with the hard disk and floppy disk is provided below:

| Characteristic   | Hard Disk                                                          | Floppy Disk                                                                           |  |  |

|------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Size             | 5 Mbytes to several Gbytes                                         | 1.2 Mbytes typical for 5.25 inch floppy.                                              |  |  |

|                  |                                                                    | 1.44 Mbytes typical for 3.5 inch floppy.                                              |  |  |

| Rotational Speed | 3600 rpm                                                           | 300 rpm                                                                               |  |  |

| Number of heads  | May have up to 8 disk surfaces with up to<br>two heads per surface | Two heads; One head for the upper surface<br>and the other head for the lower surface |  |  |

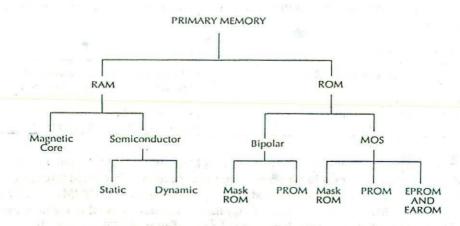

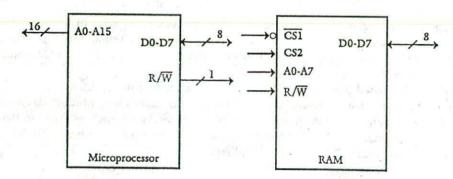

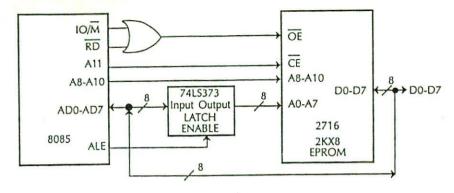

Primary memory normally includes ROM (Read-only Memory) and RAM (Random Access Memory). As the name implies, a ROM permits only a read access. Some ROMs are custom made, that is, their contents are programmed by the manufacturer. Such ROMs are called mask programmable ROMs. Sometimes a user may have to program a ROM in the field. For instance, in a fusible-link ROM, programmable read-only memory (PROM) is available. The main disadvantage of a PROM is that it cannot be reprogrammed.

Some ROMs can be reprogrammed, these are called Erasable Programmable Read-Only Memories (EPROMs).

In an EPROM, programs are entered using electrical impulses and the stored information is erased by using ultraviolet rays. Usually an EPROM is programmed by inserting the EPROM chip into the socket of a PROM programmer and providing program addresses and voltage pulses at the appropriate pins of the chip. Typical erase times vary between 10 and 30 minutes.

With advances in IC technology, it is possible to achieve an electrical means of erasure. These new ROMs are called Electrically Alterable ROMs (EAROMs) or Electrically Erasable PROMs (EEPROMs or E²PROMs) and these ROM chips can be programmed even when they are in the circuit board. These memories are also called Read Mostly Memories (RMMs), since they have much slower write times than read times. Random Access Memories (RAMs) are read/write memories.

Information stored in random access memories will be lost if the power is turned off. This property is known as volatility and, hence, RAMs are usually called volatile memories. RAMs can be backed up by batteries for a certain period of time and are sometimes called nonvolatile RAMs. Stored information in a magnetic tape or magnetic disk is not lost when the power is turned off. Therefore, these storage devices are called nonvolatile memories. Note that a ROM is a nonvolatile memory.

Some RAMs are constructed using bipolar transistors, and the information is stored in the form of voltage levels in flip-flops. These voltage levels do not usually drift away, or decay. Such memories are called static RAMs because the stored information remains constant for some period of time.

On the other hand, in RAMs that are designed using MOS transistors, the information is held in the form of electrical charges in capacitors. Here, the stored charge has the tendency to decay. Therefore, a stored 1 would become a 0 if no precautions were taken. These memories are referred to as dynamic RAMs. In order to prevent any information loss, dynamic RAMs have to be refreshed at regular intervals. Refreshing means boosting the signal level and writing it back. This activity is performed by a hardware unit called "refresh logic" which can either be a separate chip or is contained in the microprocessor chip.

Since the static RAM maintains information in active circuits, power is required even when the chip is inactive or in standby mode. Therefore, static RAMs require large power supplies. Also, each static RAM cell is about four times larger in area than an equivalent dynamic cell; a dynamic RAM chip contains about four times as many bits as a static RAM chip using the same or comparable semiconductor technology. Figure 1.3 shows the subcategories of ROMs, RAMs, and their associated technologies.

FIGURE 1.3 Subcategories of RAMs and ROMs.

Today, one megabit of data can be stored in an ordinary dynamic RAM chip. The data can be accessed in 80 nanoseconds or less. The RAM chip costs \$5. In contrast, it takes 150 nanoseconds to access a one-megabit EEPROM which costs \$150. Sixteen megabit DRAMs are very popular these days at a price of approximately 0.3 millicent per bit. Recently, IBM, Hitachi, Toshiba and others have introduced 64 mega-bit DRAMs. It is expected that giga-bit DRAMs will not be introduced until the next century.

In the mid 1980s, Toshiba Semiconductor invented flash memory. About the same time, Intel and Seeq Semiconductor were also working on flash memories. While each manufacturer

implemented its flash memory differently, they operate in a similar way.

Like EPROMs and EPROMs or EAROMs, flash memory is nonvolatile and reprogrammable. Flash memory is fabricated by using ETOX II (EPROM Tunnel Oxide) technology which is a combination of EPROM and EEPROM technologies. Flash memory is relatively inexpensive compared to EEPROM. A one megabit flash memory costs about \$15. Flash memory can be reprogrammed electrically while embedded in the board. However, one can only change a sector or a block (consisting of multiple bytes) at a time.

Flash memory cells contain a single transistor like the EPROM cell. In contrast, a DRAM cell typically contains a transistor and a capacitor, an EEPROM cell contains two transistors while

a static RAM cell requires four or six transistors.

The non-volatility and DRAM-like speed of flash memory are ideal for solid-state "disk" drives. Flash based disks do not have any disks or moving parts. Flash disks are very fast compared to most available disk drives.

Data can be accessed in 120 nanoseconds in flash memories while it takes 15 to 30 milliseconds to access data stored in today's typical hard disk. However, flash disks are limited to up to 40 megabytes in capacity whereas hard disk drives can store from 5 megabytes to several

gigabytes.

A flash disk can be built from one or more flash-memory IC chips and some controlling logic devices. For example, to build a 512Kbyte flash disk, four one-megabit flash memory chips can be connected on a small card. An example of such a flash memory system is the Intel iMC004FLKA 4 Megabyte flash memory card. In addition to flash-disk hardware, software to manage files on a flash disk is required. The file system software handles creating and deleting files, changing the file sizes and formatting the flash disk. Microsoft offers flash file system software for the MS-DOS operating system.

The most severe limitation of flash disks has been its cost. However, the cost of flash ROM is significantly decreasing. In the future, high density flash memory is expected to be available

at an inexpensive cost.

Flash memory can be programmed using either 5V or 12V. The 5V feature becomes more desirable for portable equipment will be no 12V power is available. The speed, rugged construction, and lower power consumption of flash disks is ideal for laptop and notebook

computers.

In summary, due to the high cost of flash disks, desktop computers will continue to use hard disk drives. Since flash memory combines the advantages of an EPROM's low cost with an EEPROM's case of reprogramming, flash memories are being extensively used these days as a microcomputer's main non-volatile memory. An example of flash memory is the Intel 28F020 256K x 8 flash memory. By 1997, the cost of a megabyte of flash memory is expected to move from its current level of \$120 to about \$5. At that time, flash disks will be able to replace hard disks in many applications.

## 1.3.3.b Main Memory Array Design

In many applications, a memory of large capacity is often realized by interconnecting several small-size memory blocks. In this section, design of a large main memory using small-size memories as building blocks is presented. The memory map defining all memory addresses is determined. Note that the microprocessor's reset vector must be included in the memory map.

There are three types of techniques used for designing the main memory. These are linear decoding, full decoding/partial decoding and memory decoding using PALs. We will illustrate the concepts associated with these techniques in the following.

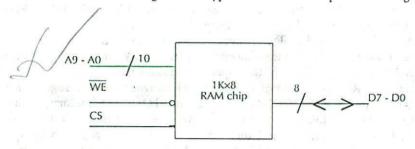

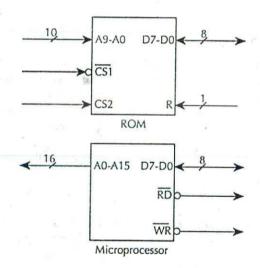

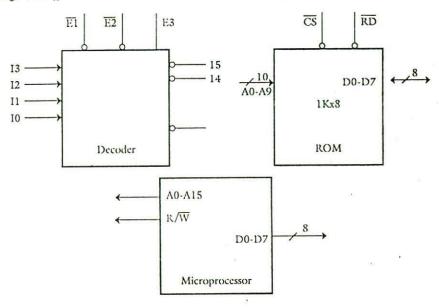

First, consider the block diagram of a typical static RAM chip shown in Figure 1.4.

FIGURE 1.4 Typical Static RAM Chip.

The capacity of this chip is 8192 bits and these bits are organized as 1024 words with 8 bits/word. Each word has a unique address and this is specified on 10-bit address lines A9—A0 (note that 2<sup>10</sup> = 1024). The inputs and outputs are routed through the 8-bit bidirectional data lines D7 through D0. The operation of this chip is governed by the two control inputs: WE (write Enable) and CS (chip select). The truth table that describes the operation of this chip is shown in Table 1.1.

| TAB | LE 1.1 | Truth Table fo |                       |         |

|-----|--------|----------------|-----------------------|---------|

| CS  | WE     | MODE           | Status of D7—D0       | Power   |

| L   | X      | Not selected   | High impedance        | Standby |

| H   | L      | Write          | Acts as an input bus  | Active  |

| LI  | 1.1    | Pand           | Acte as an output bus | Active  |

Note: H - high, L - low, X - don't care.

From this table, it is easy to see that when CS input is low, the chip is not selected and thus the lines D7 through D0 are driven to the high impedance state. When CS = 1 and WE is LOW, data on lines D7—D0 are written into the word addressed by A0 through A9. Similarly, when CS = 1 and WE is high, the contents of the memory word (whose address is specified on address lines A9 through A0) will appear on lines D7 through D0. Note that when the chip select input CS goes to low, the device is disabled and the chip automatically reduces its power requirements and remains in this low-power standby mode as long as CS remains low. This feature results in system power savings as high as 85% in larger systems, where the majority of devices are disabled.

1.3.3.b.i Linear Decoding. This technique uses the unused address lines of the microprocessor as chip selects for the memory chips. This method is used for small systems.

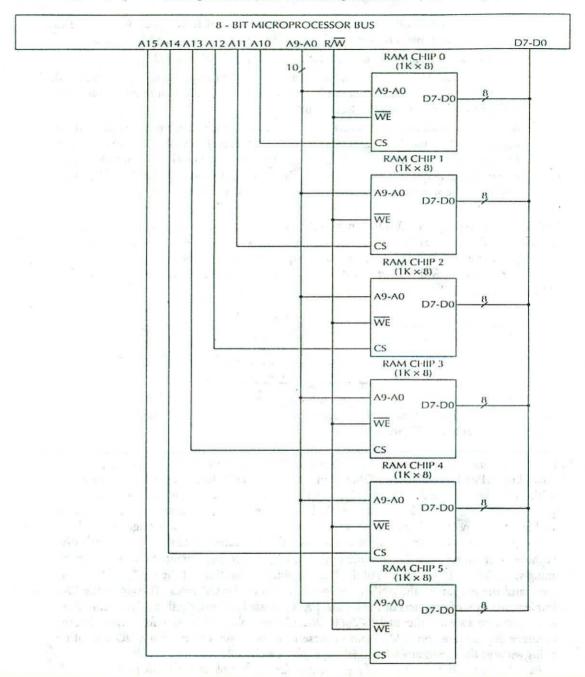

A simple way to connect an 8-bit microprocessor to a 6K RAM system using linear decoding is shown in Figure 1.5. In this approach, the address lines A9 through A0 of the microprocessor are used as a common input to each 1K × 8 RAM chip. The remaining 6 high-order lines are used to select one of the 6 RAM chips. For example, if A15A14A13A12A11A10 = 000010, then the RAM chip 1 is selected. The address map realized by this arrangement is summarized in Figure 1.6. This method is known as the linear select decoding technique. The principal advantage of this method is that it does not require any decoding hardware. However, this approach has some disadvantages:

- Although with a 16-bit address bus we have 64K bytes of RAM space, we are able to interface only 6K bytes of RAM. This means that this idea wastes address space.

- · The address map is not contiguous; rather, it is sparsely distributed.

- If both A11 and A10 are high at the same time, both RAM chips 0 and 1 are selected and

thus a bus conflict occurs. This can be avoided by proper programming to select the

desired memory chip and deselect the others.

- Also, if all unused address lines are not utilized as chip selects for memory, then these

unused pins become don't cares (can be 0 or 1). This results in foldback, meaning that

a memory location will have its image in the memory map. For example, if A15 is don't

care in design and if A14 to A0 address lines are used, then address 0000<sub>16</sub> and address

8000<sub>16</sub> are the same locations. This is called foldback and it wastes memory space.

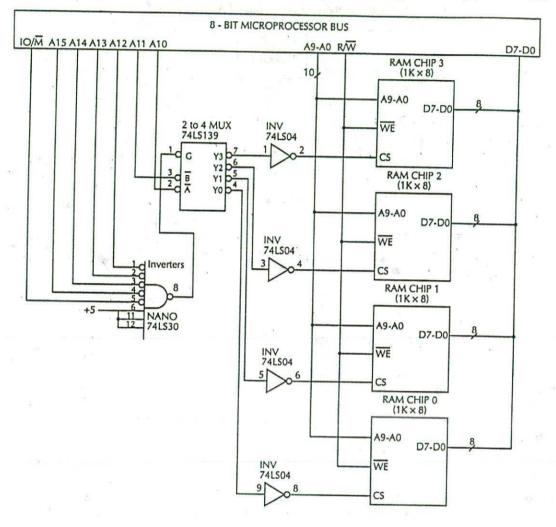

- 1.3.3.b.ii Full/Partial Decoding. Difficulties such as the bus conflict and sparse address distribution are eliminated by the use of the full/partial decoded addressing technique. To see this, consider the organization shown in Figure 1.7. In this setup, we use a 2-to-4 decoder and interface the 8-bit microprocessor with 4K bytes of RAM. In particular, the four combinations of the lines A11 and A10 select the RAM chips as follows:

| All | A10 | Device Selected |

|-----|-----|-----------------|

| 0   | 0   | RAM chip 0      |

| 0   | 1   | RAM chip 1      |

| 1   | 0   | RAM chip 2      |

| 1   | 1   | RAM chip 3      |

Also observe that this hardware makes sure that the memory system is enabled only when the lines A15 through A12 are zero. The complete address map corresponding to this organization is summarized in Figure 1.8.

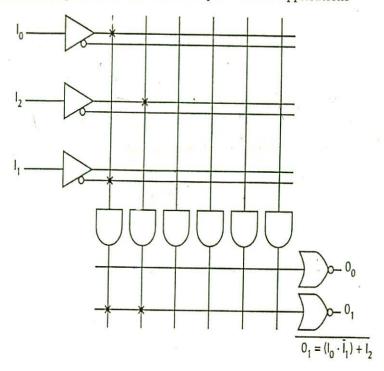

1.3.3.b.iii Memory Decoding by using Programmable Array Logic (PAL). A Programmable Array Logic (PAL) is similar to a ROM in concept except that it does not provide full decoding of the input lines. Instead, a PAL provides a partial sum of products which can be obtained via programming and saves a lot of space on the board. The PAL chip contains a fused programmable AND array and a fixed OR array. Note that in PLA (Programmable Logic Array) both AND and OR arrays are programmable. The AND and OR gates are fabricated inside the PAL without interconnections. The specific functions desired are implemented during programming via software. Programming of the PAL provides connections of the inputs of the AND gates and the outputs of the AND gates to the inputs of the OR gates. Therefore, the PAL implements sum of products of the inputs. PALs are used extensively these days with 32-bit microprocessors such as the Intel 80386/80486 and Motorola 68030/68040 for performing the memory decode function. PALs connect these microprocessors to memory, I/O and other chips without the use of any additional logic gates or circuits.

Each input has both true and complemented forms. A look at the NOR gate output  $\emptyset_1$  indicates that there are two X connections at the inputs of this NOR gate. The three X inputs are wire-ANDed together with programming the PAL so that  $\emptyset_1 = (I_0 \cdot \overline{I_1}) + I_2$ .

The PAL chips are usually identified by a two-digit number followed by a letter and then a digit. The two-digit number specifies the number of input lines while the last digit defines the number of output lines. The fixed number of AND gates are connected to either an OR or a NOR gate. The letter 'H' indicates that the output gates are OR gates. The letter 'L' is used when the outputs are NOR gates.

As an example, the 10H8 provides eight OR gate outputs driven by ten AND gate inputs. The 10L8, on the other hand, is the same as the 10H8 except that the eight output gates are NOR gates.

FIGURE 1.5 An 8-bit microprocessor interfaced to a 6K RAM system using the linear select decoding technique.

Some PALs provide additional features. The 16L8 includes tristate outputs. Each of the eight NOR gate outputs is driven internally by six AND gates. A seventh AND gate provides the enable signal for the tristate buffers.

The 16L8 is a popular PAL used with 32-bit microprocessors. The 16L8 is a 20-pin PAL manufactured using bipolar transistors. It has ten input pins (labeled I), two outputs (labeled O) and six programmable Input/Output (labeled I/O) lines. Using the programmable I/O lines, the number of input lines can be increased to a maximum of 16 and the number of output lines can be increased to 8.

|   |   |   |   |     | atte |   | A7 | Α6    | Λ5 |   | A3  | Λ2 | ΛI | Λ0  | Device<br>Selected | Address Assignment in Hex |

|---|---|---|---|-----|------|---|----|-------|----|---|-----|----|----|-----|--------------------|---------------------------|

| 0 | 0 | 0 | 0 | 0   | 1    | 0 | 0  | 0 . 1 | 0  | 0 | 0   | 0  | 0  | 0   | RAM<br>CHIP<br>0   | 0400<br>to<br>07FF        |

| 0 | 0 | 0 | 0 | 1   | 0    | 0 | 0  | 0     | 0  | 0 | 0 . | 0  | 0  | 0   | RAM<br>CHIP<br>1   | 0800<br>to<br>OBFF        |

| 0 | 0 | 0 | 1 | 0   | 0    | 0 | 0  | 0     | 0  | 0 | 0   | 0  | 0  | 0   | RAM<br>CHIP<br>2   | 1000<br>to<br>13FF        |

| 0 | 0 | 1 | 0 | 0   | 0    | 0 | 0  | 0     | 0  | 0 | 0   | 0  | 0  | 0   | RAM<br>CHIP<br>3   | 2000<br>to<br>23FF        |

| 0 | 1 | 0 | 0 | 0   | 0    | 0 | 0  | 0     | 0  | 0 | 0   | 0  | 0  | 0 . | RAM<br>CHIP<br>4   | 4000<br>to<br>43FF        |

| 1 | 0 | 0 | 0 | 0 . | 0    | 0 | 0  | 0     | 0  | 0 | 0   | 0  | 0  | 0   | RAM<br>CHIP<br>5   | 8000<br>to<br>83FF        |

FIGURE 1.6 Address map realized by the system shown in Figure 1.5.

Programming PALs can be accomplished by first creating a file by using a text editor on a personal computer. The file should include information such as the pin assignments of the PAL and the boolean equation for the outputs. By inserting the PAL into the programming module included with the personal computer, the PAL can then be programmed with the PAL programming software provided with the personal computer. Note that PAL programming hardware and software are sold separately and not usually included with a personal computer.

#### 1.3.3.c Memory Management Concepts

Due to the massive amount of information that must be saved in most systems, the mass storage is often a disk. If each access is to a disk (even a hard disk), then system throughput will be reduced to unacceptable levels.

An obvious solution is to use a large and fast locally accessed semiconductor memory. Unfortunately the storage cost per bit for this solution is very high. A combination of both off-board disk (secondary memory) and on-board semiconductor main memory must be designed into a system. This requires a mechanism to manage the two-way flow of information between the primary (semiconductor) and secondary (disk) media. This mechanism must be able to transfer blocks of data efficiently, keep track of block usage, and replace them in a nonarbitrary way. The primary memory system must therefore be able to dynamically allocate memory space.

An operating system must have resource protection from corruption or abuse by users. Users must be able to protect areas of code from each other, while maintaining the ability to communicate and share other areas of code. All these requirements indicate the need for a device, located between the microprocessor and memory, to control accesses, perform address mappings, and act as an interface between the logical (programmer's memory) and microprocessor physical (memory) address spaces. Since this device must manage memory use, it is appropriately called the memory management unit (MMU). Typical 32-bit microprocessors such as Motorola 68030 and Intel 80386 include on-chip MMU.

The MMU reduces the burden of the memory management function on the operating system.

The basic functions provided by the MMU are address translation and protection. The MMU translates logical program addresses to physical memory addresses. The addresses in a

FIGURE 1.7 An 8-bit microprocessor interfaced to a 4K RAM system using a full/partial decoded addressing technique

|   | nary<br>5 A14 |   |   |   |     |   | A7 | A6 | A5 | A4 | A3 | A2 | A1 | AO  | Device<br>Selected | Address Assignment in Hex |

|---|---------------|---|---|---|-----|---|----|----|----|----|----|----|----|-----|--------------------|---------------------------|

| 0 | 0             | 0 | 0 | 0 | 0   | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | RAM<br>CHIP<br>0   | 0000<br>to<br>03FF        |

| 0 | 0             | 0 | 0 | 0 | 1 1 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | RAM<br>CHIP<br>1   | 0400<br>to<br>07FF        |

| 0 | 0             | 0 | 0 | 1 | 0   | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 . | RAM<br>CHIP<br>2   | 0800<br>to<br>OBFF        |

| 0 | 0             | 0 | 0 | 1 | 1   | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | RAM<br>CHIP<br>3   | 0C00<br>to<br>0FFF        |

FIGURE 1.8 Address map corresponding to the organization shown in Figure 1.7.

FIGURE 1.9 A typical PAL.

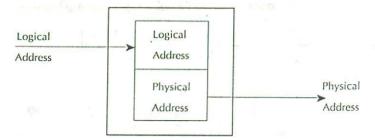

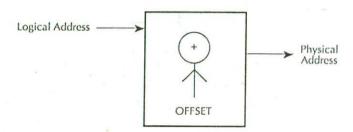

program are called logical addresses since they indicate the logical positions of instructions and data. The MMU translates these logical addresses to physical addresses provided by the memory chips. The MMU can perform address translation in one of two ways:

- 1. By using the substitution technique as shown in Figure 1.10a

- By adding an offset to each logical address to obtain the corresponding physical address as shown in Figure 1.10b

Address translation using substitution is faster than the offset method. However, the offset method has the advantage of mapping a logical address to any physical address as determined by the offset value.

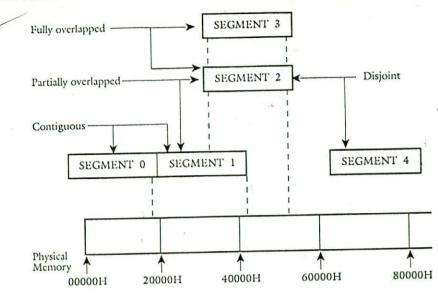

Memory is usually divided into small manageable units. The terms "page" and "segment" are frequently used to describe these units. Paging divides the memory into equal-sized pages, while segmentation divides the memory into variable-sized segments.

It is relatively easier to implement the address translation table if the logical and main memory spaces are divided into pages. The term "page" is associated with logical address space, while the term "block" usually refers to a page in main memory space.

There are three ways to map logical addresses to physical addresses. These are paging, segmentation, and combined paging/segmentation.

In a paged system, a user has access to a larger address space than physical memory provides. The virtual memory system is managed by both hardware and software. Note that memory in excess of the main memory such as floppy disk storage is called virtual memory. The hardware included in the memory management unit handles address translation. The memory management software in the operating system performs all functions including page replacement policies in order to provide efficient memory utilization. The memory management software performs functions such as removal of the desired page from main memory to accommodate a new page, transferring a new page from secondary to main memory at the right instant of time, and placing the page at the right location in memory.

FIGURE 1.10a Address translation using substitution technique.

FIGURE 1.10b Address translation by offset technique.

If the main memory is full during transfer from secondary to main memory, it is necessary to remove a page from main memory to accommodate the new page. Two popular page replacement policies are first-in first-out (FIFO) and least recently used (LRU). The FIFO policy removes the page from main memory that has been resident in memory for the longest amount of time. The FIFO replacement policy is easy to implement. One of the main disadvantages of the FIFO policy is that it is likely to replace heavily used pages. Note that heavily used pages are resident in main memory for the longest amount of time. Sometimes this replacement policy might be a poor choice. For example, in a time-shared system, several users normally share a copy of the text editor in order to type and correct programs. The FIFO policy on such a system might replace a heavily used editor program page to make room for a new page. This program page might be recalled to main memory immediately. The FIFO, in this case, would be a poor choice.

The LRU policy, on the other hand, replaces that page which has not been used for the longest amount of time.

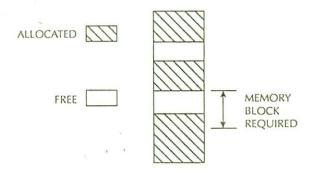

In the segmentation method, the MMU utilizes the segment selector to obtain a descriptor from a table in memory containing several descriptors. A descriptor contains the physical base address for a segment, the segment's privilege level, and some control bits. When the MMU obtains a logical address from the microprocessor, it first determines whether the segment is already in the physical memory. If it is, the MMU adds an offset component to the segment base component of the address obtained from the segment descriptor table to provide the physical address. The MMU then generates the physical address on the address bus for accessing the memory. On the other hand, if the MMU does not find the logical address in physical memory, it interrupts the microprocessor. The microprocessor executes a service routine to bring the desired program from a secondary memory such as disk to the physical memory. The MMU determines the physical address using the segment offset and descriptor as above and then generates the physical address on the address bus for memory. A segment will usually consist of an integral number of pages, say, each 256 bytes long. With differentsized segments being swapped in and out, areas of valuable primary memory can become unusable. Memory is unusable for segmentation when it is sandwiched between already allocated segments and if it is not large enough to hold the latest segment that needs to be

loaded. This is called external fragmentation and is handled by MMUs using special techniques. An example of external fragmentation is given in Figure 1.11. The advantages of segmented memory management are that few descriptors are required for large programs or data spaces, and internal fragmentation (to be discussed later) is minimized. The disadvantages include external fragmentation, involved algorithms for placing data are required, possible restrictions on starting address, and longer data swap times are required to support virtual memory.

FIGURE 1.11 Memory fragmentation (external).

Address translation using descriptor tables offers a protection feature. A segment or a page can be protected from access by a program section of a lower privilege level. For example, the selector component of each logical address includes one or two bits indicating the privilege level of the program requesting access to a segment. Each segment descriptor also includes one or two bits providing the privilege level of that segment. When an executing program tries to access a segment, the MMU can compare the selector privilege level with the descriptor privilege level. If the segment selector has the same or higher privilege level, then the MMU permits the access. If the privilege level of the selector is lower than the descriptor, the MMU can interrupt the microprocessor informing of a privilege level violation. Therefore, the indirect technique of generating physical address provides a mechanism of protecting critical program sections in the operating system.

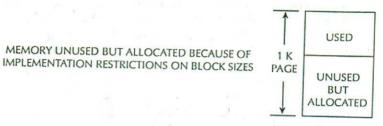

Paging divides the memory into equal-sized pages, it avoids the major problem of segmentation-external fragmentation. Since the pages are of the same size, when a new page is requested and an old one swapped out, the new one will always fit into the vacated space. However, a problem common to both techniques remains — internal fragmentation. Internal fragmentation is a condition where memory is unused but allocated due to memory block size implementation restrictions. This occurs when a module needs, say, 300 bytes and page is 1K bytes, as shown in Figure 1.12.

In the paged-segmentation method, each segment contains a number of pages. The logical address is divided into three components: segment, page, and word. The segment component defines a segment number, the page component defines the page within the segment, and the word component provides the particular word within the page. A page component of n bits can provide up to 2<sup>n</sup> pages. A segment can be assigned with one or more pages up to a maximum of 2<sup>n</sup> pages; therefore, a segment size depends on the number of pages assigned to it.

Protection mechanisms can operate either on physical address or logical address. Physical memory protection can be accomplished by using one or more protection bits with each block to define the access type permitted on the block. This means that each time a page is transferred from one block to another, the block protection bits must be updated. A more efficient approach is to provide a protection feature in logical address space by including protection bits in the descriptors of the segment table in the MMU.

## PAGES === 1 K IF 300 BYTES NEEDED 1 K BYTES ARE ALLOCATED

FIGURE 1.12 Memory fragmentation (internal).

## 1.3.3.d Cache Memory Organization

The performance of a microcomputer system can be significantly improved by introducing a small, expensive, but fast memory between the microprocessor and main memory. This memory is called cache memory and this idea was first introduced in the IBM 360/85 computer. Later on, this concept was also implemented in minicomputers such as PDP-11/70. With the advent of VLSI technology, the cache memory technique is gaining acceptance in the microprocessor world. For example, an on-chip cache memory is implemented in Intel's 32-bit microprocessor, the 80486, and Motorola's 32-bit microprocessors, the MC 68020/68030/68040. The 80386 does not have on-chip cache but external cache memory can be interfaced to it. Studies have shown that typical programs spend most of their execution times in loops. This means that the addresses generated by a microprocessor have a tendency to cluster around a small region in the main memory. This phenomenon is known as locality of reference. The 32-bit microprocessor can execute the same instructions in a loop from the on-chip cache rather than reading them repeatedly from the external main memory. Thus the performance offered by 32-bit microprocessors is greatly improved.

The block diagram representation of a microprocessor system that employs an on-chip cache memory is shown in Figure 1.13. Usually, a cache memory is very small in size and its access time is less than that of the main memory by a factor of 5.

Cache hit means that the reference is found in the cache and the data pertaining to the microprocessor reference is transferred to the microprocessor from the cache. However, if the reference is not found in the cache, we call it a cache miss. When there is a cache miss, the main memory is accessed by the microprocessor and the data are then transferred to the microprocessor from the main memory. At the same time, a block of data containing the desired data needed by the microprocessor is transferred from the main memory to the cache. The block normally contains 4 to 16 bytes, and this block is placed in the cache using the standard replacement policies such as FIFO (First-In First-Out) or LRU (Least Recently Used). This block transfer is done with a hope that all future references made by the microprocessor will be confined to the fast cache.

The relationship between the cache and main memory blocks is established using mapping techniques. Three widely used mapping techniques are

- · Direct mapping

- · Fully-associative mapping

- · Set-associative mapping

In direct mapping, the main memory address is divided into two fields: an index field and a tag field. The number of bits in the index field is equal to the number of address bits required to access the cache memory.

Assume that the main memory address is m bits wide and the cache memory address is n bits wide. Then the index field requires n bits and the tag field is (m — n) bits wide. The n-

FIGURE 1.13 Memory organization of a computer system that employs a cache memory.

bit address accesses the code. Each word in the cache includes the data word and its associated tag. When the microprocessor generates an address for main memory, the index field is used as the address to access the cache. The tag field of the main memory is compared with the tag field in the word read from cache. A hit occurs if the tags match. This means that the desired data word is in cache. A miss occurs if there is no match, and then the required word is read from main memory. It is written in the cache along with the new tag. A random access memory is used as the cache memory.

One of the main drawbacks of direct mapping is that numerous misses may occur if two or more words with addresses having the same index but different tags are accessed several times. This can be minimized by incorporating a larger cache.

The fastest cache memory utilizes an associative memory. The method is known as fully associative mapping. Each associative memory content contains main memory address and its content (data). When the microprocessor generates a main memory address, it is compared associatively (simultaneously) with all addresses in the associative memory. If there is a match, the corresponding data word is read from the associative cache memory and sent to the microprocessor. If a miss occurs, the main memory is accessed, and the address and its corresponding data are written to the associative cache memory. If the cache is full, certain policies such as FIFO (first-in first-out) are used as replacement algorithm for the cache. The associative cache is expensive but provides fast operation.

The set-associative mapping is a combination of direct and associative mapping. Each cache word stores two or more main memory words using the same index address. Each main memory word consists of a tag and its data word. An index with two or more tags and data words forms a set. When the microprocessor generates a memory request, the index of the main memory address is used as the cache address. The tag field of the main memory address is then compared associatively (simultaneously) with all tags stored under the index. If a match occurs, the desired data word is read. If a miss occurs, the data word, along with its tag, is read from main memory and also written into the cache. The hit ratio improves as the set size increases. This is because more words with the same index but different tags can be stored in cache.

There are two ways of writing into cache: the write-back and write-through methods. In the write-back method, whenever the microprocessor writes something into a cache word, a dirty bit is assigned to the cache word. When a dirty word is to be replaced with a new word, the

dirty word is first copied into the main memory before it is overwritten by the incoming new word. The advantage of this method is that it avoids unnecessary writing into main memory.

In the write-through method, whenever the microprocessor alters cache data, the same alteration is made in the main memory copy of the altered cache data. This policy can be easily implemented and also it insures that the contents of the main memory are always valid. This feature is desirable in a multiprocessor system where the main memory is shared by several processors. However, this approach may lead to several unnecessary writes to main memory.

One of the important aspects of cache memory organization is to devise a method that insures proper utilization of the cache. Usually, the tag directory contains an extra bit for each entry. This additional bit is called a valid bit. When the power is turned on, the valid bit corresponding to each cache block entry of the tag directory is reset to zero. This is done in order to indicate that the cache block holds invalid data. When a block of data is first transferred from the main memory to a cache block, the valid bit corresponding to this cache block is set to 1. In this arrangement, whenever the valid is a zero, it implies that a new incoming block can overwrite the existing cache block. Thus, there is no need to copy the contents of the cache block being replaced into the main memory.

## 1.3.4 Input/Output (I/O)

This section describes the basic input and output techniques used by microcomputers to transfer data between the microcomputer and external devices. The general characteristics of I/O are described. One communicates with a microcomputer system via the I/O devices interfaced to it. The user can enter programs and data using the keyboard on a terminal and execute the programs to obtain results. Therefore, the I/O devices connected to a microcomputer system provide an efficient means of communication between the computer and the outside world. These I/O devices are commonly called peripherals and include keyboards, CRT displays, printers, and disks.

The characteristics of the I/O devices are normally different from those of the microcomputer. For example, the speed of operation of the peripherals is usually slower compared to the microcomputer, and the word length of the microcomputer may be different from the data format of the peripheral device. To make the characteristics of the I/O devices compatible with those of the microcomputer, interface hardware circuitry between the microcomputer and I/O devices is necessary.

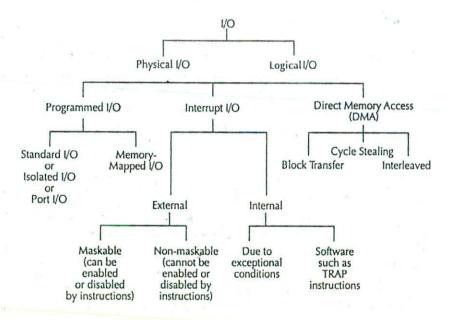

In a typical microcomputer system, the user gets involved with two types of I/O devices: physical I/O and logical I/O. When the microcomputer has no operating system, the user must work directly with physical I/O devices and perform detailed I/O design.

There are three ways of transferring data between the microcomputer and a physical I/O device:

- · Programmed I/O

- · Interrupt driven I/O

- Direct memory access (DMA)

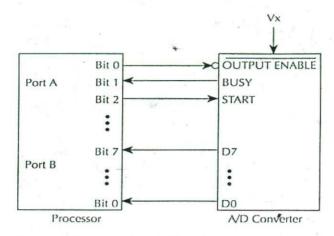

The microcomputer executes a program to communicate with an external device via a register called the I/O port for programmed I/O.

An external device requests the microcomputer to transfer data by activating a signal on the microcomputer's interrupt line during interrupt I/O. In response, the microcomputer executes a program called the interrupt-service routine to carry out the function desired by the external device, again by way of one or more I/O ports.

Data transfer between the microcomputer's memory and an external device occurs without microprocessor involvement with direct memory access.

For a microcomputer with an operating system, the user works with virtual I/O devices. The user does not have to be familiar with the characteristics of the physical I/O devices. Instead, the user performs data transfers between the microcomputer and the physical I/O devices indirectly by calling the I/O routines provided by the operating system using virtual I/O instructions. This is called logical I/O.

#### 1.3.4.a Programmed I/O

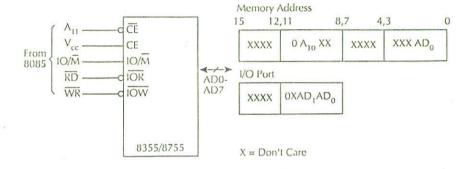

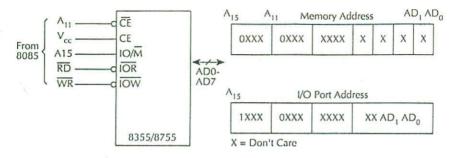

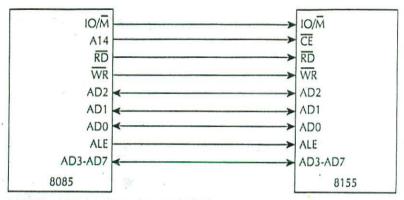

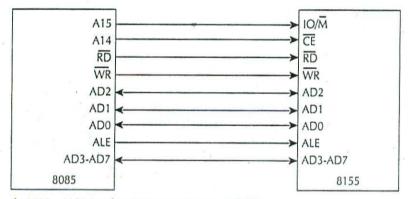

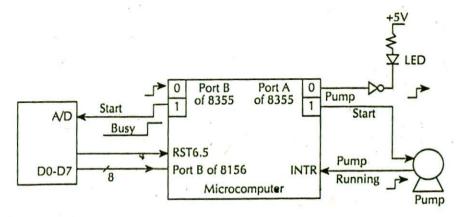

As described earlier, the microcomputer communicates with an external device via one or more registers called I/O ports using programmed I/O. These I/O ports are occasionally fabricated by the manufacturer in the same chip as the memory chip to achieve minimum chip count for small system applications. For example, the Intel 8355/8755 contains 2K bytes of ROM/EPROM with two I/O ports. The Motorola 6846 has 2K bytes of ROM and an 8-bit I/O port.

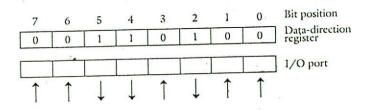

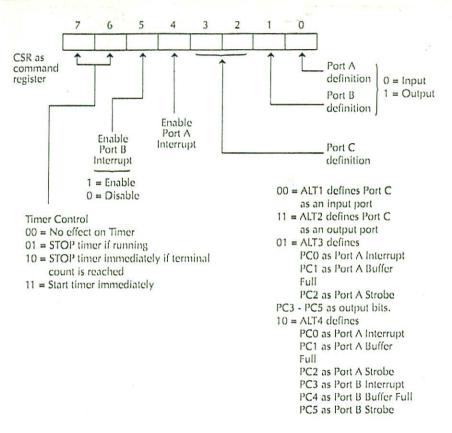

I/O ports are usually of two types. For one type, each bit in the port can be individually configured as either input or output. For the other type, all bits in the port can be set up as either all parallel input or output bits. Each port can be configured as an input or output port by another register called the command, or data-direction register. The port data register contains the actual input or output data. The data-direction register is an output register and can be used to configure the bits in the port as inputs or outputs.

Each bit in the port can usually be set up as an input or output by respectively writing a 0 or a 1 in the corresponding bit of the data-direction register (DDR). A bidirectional buffer (one input buffer and one output buffer) is connected at each bit of the port. A '1' written to a particular bit in DDR enables the output buffer while a '0' enables the input buffer connected at the corresponding bit of the port. As an example, if an 8-bit data-direction register contains  $34_{16}$ , then the corresponding port is defined as follows:

In the preceding example, since  $34_{16}$  (0011 0100<sub>2</sub>) is sent as an output into the data-direction register, bits 0, 1, 3, 6, and 7 of the port are set up as inputs, and bits 2, 4, and 5 of the port are defined as outputs. The microcomputer can then send outputs to external devices, such as LEDs, connected to bits 2, 4, and 5 through a proper interface. Similarly, the microcomputer can input the status of external devices, such as switches, through bits 0, 1, 3, 6, and 7. To input data from the input switches, the 8-bit microcomputer assumed here inputs the complete byte, including the bits to which LEDs are connected. While receiving input data from an I/O port, however, the microcomputer places a value, probably 0, at the bits configured as outputs and the program must interpret them as "don't cares". At the same time, the microcomputer's outputs to bits configured as inputs are disregarded.

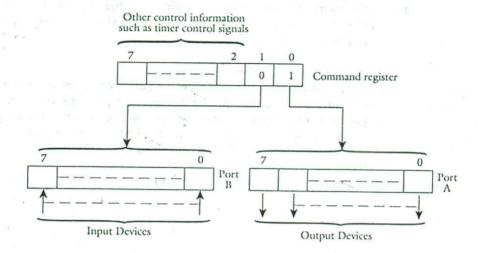

For parallel I/O, there is only one register, known as the command register, for all ports. A particular bit in the command register configures all bits in a port as either inputs or outputs. Consider two I/O ports in an I/O chip along with one command register. Assume that a 0

or a 1 in a particular bit position defines all bits of ports A or B as inputs or outputs.

For example,

Some I/O ports are called handshake ports. Data transfer occurs via these ports through exchanging of control signals between the I/O controller and an external device.

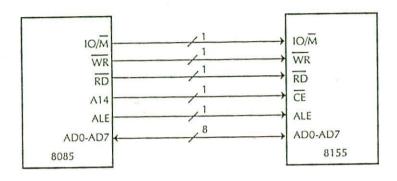

## 1.3.4.b Standard I/O Versus Memory-Mapped I/O

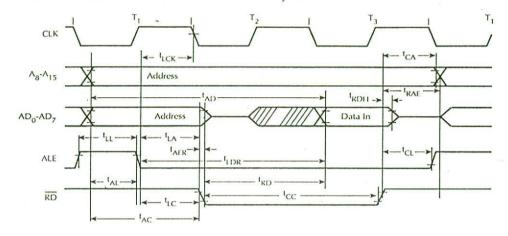

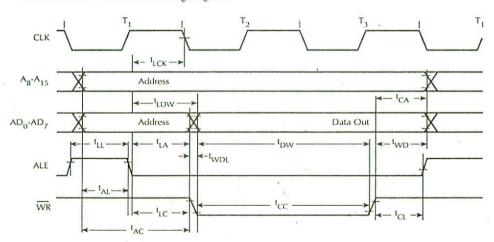

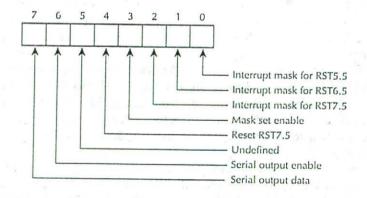

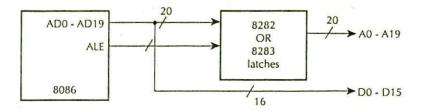

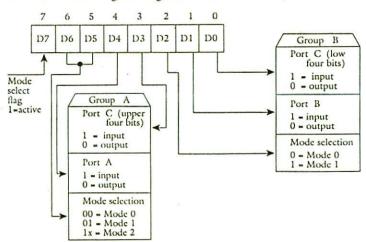

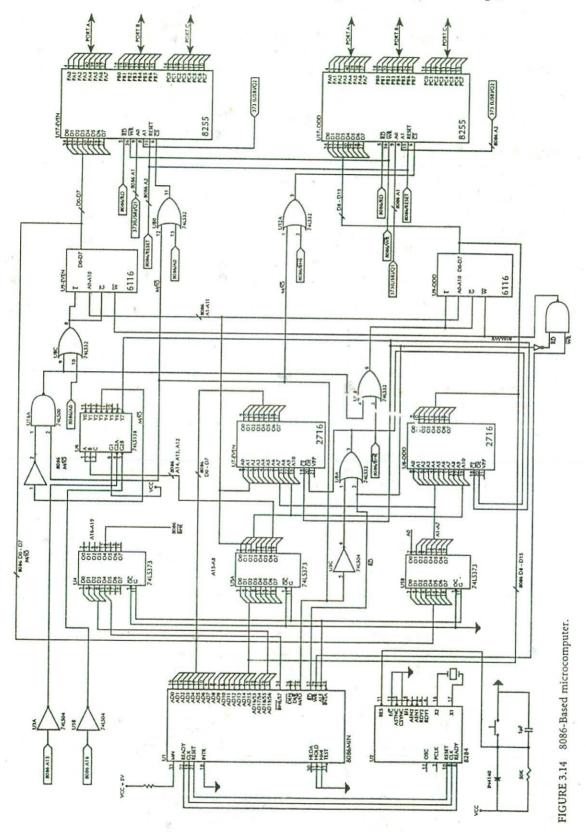

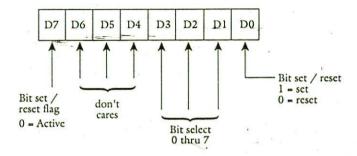

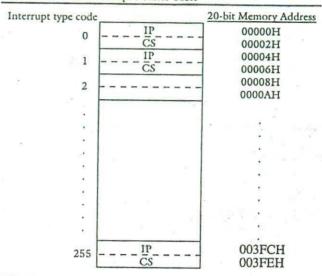

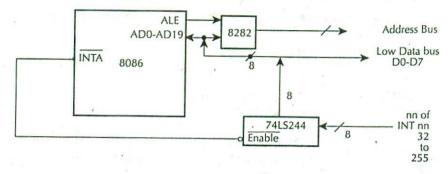

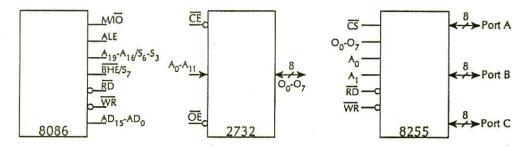

I/O ports are addressed using either standard I/O or memory-mapped I/O techniques. The standard I/O, also called isolated I/O, uses the IO/M control pin on the microprocessor chip. The processor outputs a HIGH on this pin to indicate to memory and the I/O chips that an I/O operation is taking place. A LOW output from the processor to this pin indicates a memory operation. Execution of IN or OUT instructions makes the IO/M HIGH, whereas memoryoriented instructions, such as LDA and STA, drive the IO/M to LOW. In standard I/O, the processor uses the IO/M pin to distinguish between I/O and memory. For 8-bit microprocessors, an 8-bit address is typically used for each I/O port. This is because 8 bits are the basic data unit for these processors. Eight-bit processors are usually capable of directly addressing 64K bytes of memory using 16 address lines. With an 8-bit I/O port address, these processors are capable of addressing 256 ports. However, in a typical application, there are usually four or five I/O ports required. Some of the address bits of the microprocessor are normally decoded to obtain the I/O port addresses. With memory-mapped I/O, the processor does not differentiate between I/O and memory and, therefore, does not use the microprocessor's IO/M control pin. The microprocessor uses the memory addresses (which may not exist in the microcomputer's physical memory) to represent I/O ports. The I/O ports are mapped into the microprocessor's main memory and, hence, are called memory-mapped I/O.